AMD’s Ryzen 9000 series desktop processors are by now well into the second half of their lifecycle as AMD’s leading-edge desktop chips. With a complete product stack in play – ranging from 6 up to 16 CPU cores on a single chip – In most generations, this would be where AMD would stand pat on their chip lineup, tweak prices, and otherwise ride out the rest of the generation with a fully ramped and readily available product family.

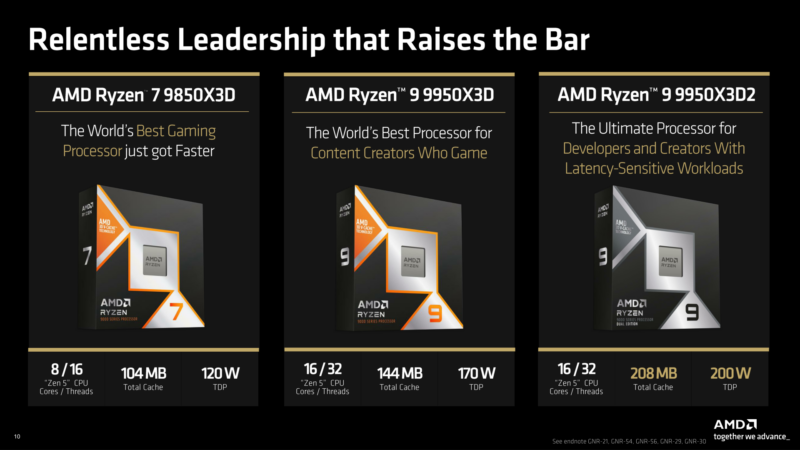

But these are far from normal times for anyone in the industry right now, and the desktop CPU market is no exception. With DRAM prices taking the wind out of the sails (and the sales) of chip manufacturers, AMD is throwing out one last halo product for this generation, the likes of which we have never seen before. And that is the Ryzen 9 9950X3D2 Dual Edition, a version of AMD’s flagship 16-core part with large L3 caches on both CPU dies – a product configuration that AMD has never previously released on the consumer market.

| AMD Ryzen 9950X Processor Specs | |||||||

| V-Cache Cores | Standard Cores | Turbo Freq |

L2 Cache |

L3 Cache |

TDP | Price | |

| Ryzen 9 9950X3D2 |

16 | n/a | 5.6GHz | 16 MB | 192 MB | 200W | $899 |

| Ryzen 9 9950X3D |

8 | 8 | 5.7GHz | 16 MB | 128 MB | 170W | $657 |

| Ryzen 9 9950X |

n/a | 16 | 5.7GHz | 16 MB | 64 MB | 170W | $520 |

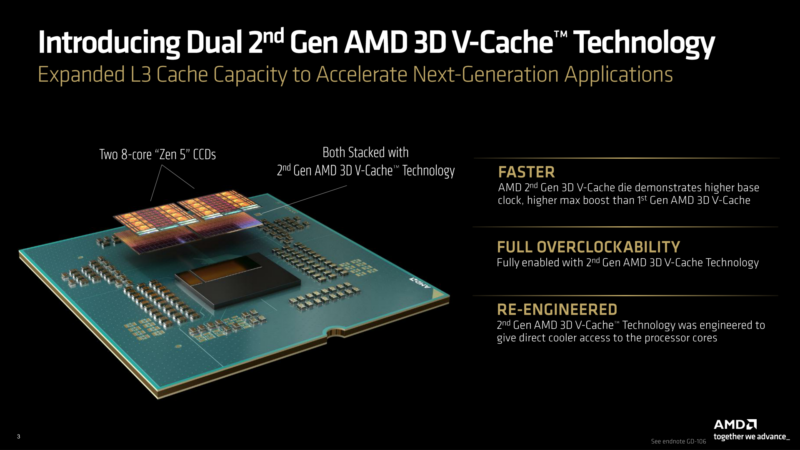

Now in its second generation of technology (and third generation of processors), AMD’s stacked 3D cache technology, V-cache, has become a regular sight within AMD’s product lineup. By stacking an additional die onto (or rather, underneath) AMD’s core complex dies, AMD is able to greatly expand the amount of L3 cache available to its CPU cores. For the right workloads, it can offer a significant boost in performance by keeping critical data closer to the CPU cores. It is a classic CPU design tradeoff that AMD has taken to the next level by stacking additional cache if and when they want it, without having to design multiple versions of their CCDs.

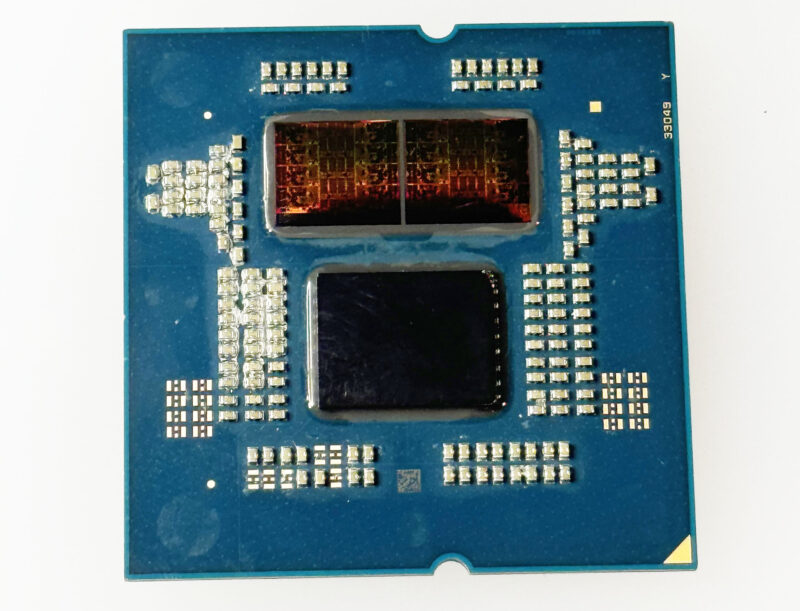

In prior iterations of V-cache-equipped chips – including the most recent 9950X3D – AMD had only installed additional cache on one of the two CCDs in their high-end parts, citing market needs and performance trade-offs. But for the Zen 5 generation, they are going one further and delivering on a product that a lot of techies have always been curious about by placing stacked cache on both CCDs.

The resulting chip, using the aptly named X3D2 configuration, is in principle a specialty chip that customers with heavily threaded (and highly parallel) workloads can benefit from the extra cache on the second CCD. AMD is taking particular aim at the professional market here, pitching the chip at developers and content creators who need the best and have a suitable workload, treating the chip as sort of an alternative, entry-level high-end desktop (HEDT) option.

Notably, unlike past X3D chips, AMD is not explicitly chasing the gaming market with the 9950X3D2. To be sure, the chips work just fine at gaming and you will see gaming system vendors lining up to offer the chip in their systems, but games are not the type of workloads that benefit from the additional L3 cache on the second CCD. This, coupled with an MSRP of $899, has AMD going after the professional market and a more specific flavor of workloads.

But regardless of AMD’s intended markets, the end result is that the Ryzen 9 9950X3D2 Dual Edition is AMD’s newest (and presumably final) flagship Ryzen 9000 series processor. With 16 Zen 5 CPU cores, a ridiculous 192MB of L3 cache, and a 200 Watt TDP, AMD is not leaving any performance on the table. The 9950X3D2 is designed to deliver every last bit of performance that the Zen 5 architecture can offer.

With reviews going out today, the chip will go on sale at retail and in OEM systems tomorrow. If you would like to buy it, you can find it at this Amazon affiliate link.

9950X3D2 Dual Edition Overview: The Architectural Trade-Offs of More Cache

With AMD having launched its first Ryzen 9000 series processors almost 18 months ago, the Ryzen 9000 chips are a well-understood architecture at this point. AMD’s chiplet-based approach to construction sees the company place its Zen 5 architecture CPU cores on its own chiplets – up to 8 cores on a CCD – pairing up to two CCDs with the company’s I/O die, which links everything together while providing I/O, memory, and integrated graphics, among other features. This split structure helps AMD to control risk by not having to manufacture a single large monolithic die, as well as control costs by only building the CCDs on a cutting-edge process node, while the IOD is built on an older and cheaper process node.

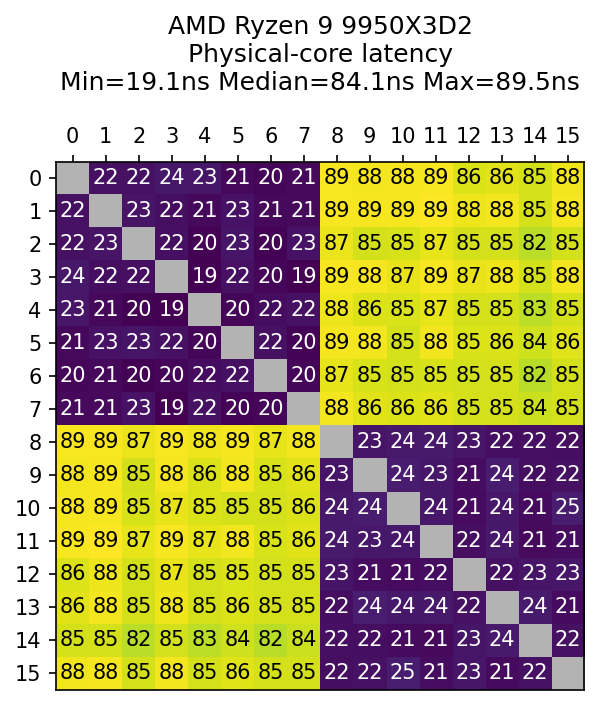

This chiplet-based approach, which AMD has now used for several years, comes with its trade-offs, a few of which are directly relevant to the 9950X3D2, and AMD’s decisions around using their V-cache technology in general. In particular, while the CPU cores within a CCD have very low latency access to each other, anything that requires going off the CCD and through the IOD incurs a significant latency penalty. This includes the other CCD in a 12 or 16 CPU core configuration, as the only way to access the other CCD is through the IOD, resulting in a roughly 65ns penalty versus staying on-die – a small eternity for a CPU core operating at upwards of 5.6GHz.

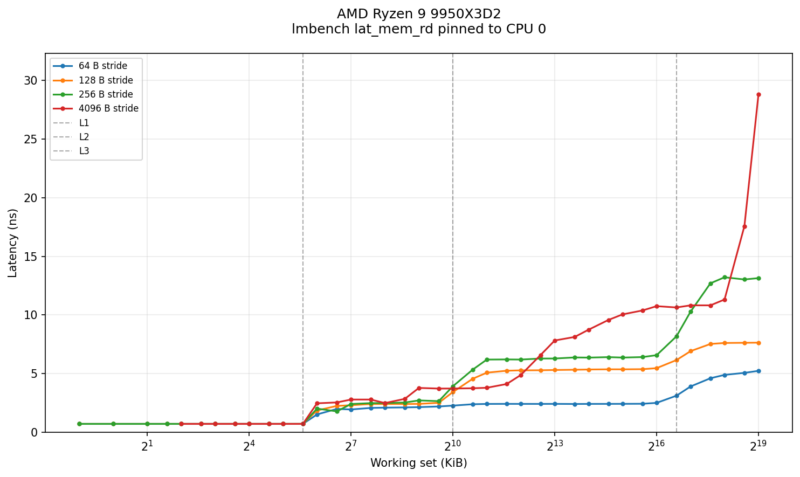

The high cost of going off-die has meant that AMD’s chip architecture has, for the last few generations, favored workloads that either keep everything contained within a single CCD (8 CPU cores) or workloads that are so highly parallel (if not embarrassingly so) that the constituent threads only minimally talk to each other. Thankfully, most workloads do fit within these limitations – workloads with chatty threads are difficult to scale out at all – but it has a special significance for X3D chips thanks to the large cache sizes in play. Large caches increase the chances that a critical piece of data is in a chip cache, but in a multi-CCD setup, it also increases the odds that a critical piece of data is in another CCD’s cache. And having to reach out across CCDs to fetch that data can crater performance if it happens frequently.

As a result, for the consumer market, AMD has, up until now, only placed additional L3 cache on one of the CCDs. Working in conjunction with the OS’s thread scheduler and additional thread scheduling tools (such as AMD’s PPM provisioning driver), the goal is to put workloads that benefit from the additional cache onto the large cache CCD, while the standard CCD gets everything else.

As AMD has argued as far back as the Ryzen 5000 days, when V-cache was introduced, and the question of multiple CCDs was posited, this configuration delivers the bulk of the potential performance gains for the large cache architecture, striking a balance between performance and costs. Adding V-cache to a CCD is relatively expensive, but it can be worth it for one CCD; adding V-cache to a second CCD adds just as much to the cost, but provides much less in the way of performance returns.

This was especially the case for AMD’s first generation of V-cache technology (5000X3D/7000X3D), where V-cache CCDs had a peak clockspeed several hundred megahertz lower than standard CCDs. That meant adding cache could actually hurt performance on throughput-intensive workloads, which is still the case today. Ultimately, the problem was largely solved by the second generation of V-cache, resulting in a much smaller 100MHz clockspeed penalty that makes a dual-V-cache chip more viable for the consumer market.

In practice, there are workloads that can meaningfully benefit from additional cache on the second CCD. There are not a ton of them, but they exist. And this is something we have seen first-hand in the server space with AMD’s 3rd and 4th generation EPYC processors, where the company offered X-class chips with V-cache on all of the chips’ numerous CCDs.

Now in 2026, AMD believes that workloads have evolved enough that a dual-V-cache part is viable for the consumer/prosumer market. Which is not to say that all of the trade-offs mentioned above have gone away, but that newer workloads put just enough weight on the scale for AMD to justify shipping a part with V-cache on both CCDs. (It does not hurt either that as AMD is not shipping any EPYC 9005 Turin parts with V-cache, they have more spare capacity this generation)

The end result is that AMD is tossing a dual V-cache part on the market with the belief that the demand is finally there to make such a product viable. In effect, this is wringing out the last bits of performance from the Zen 5 architecture that AMD was not already able to deliver with the 9950X3D, which is not much, but AMD believes the market is there.

Next to the changes in cache configuration, the other notable change with the 9950X3D2 are its power limits. And this is what we will look at next.