As part of the Intel Xeon “Ice Lake” generation, we expect Intel to adopt a new microarchitecture generation called the Intel Sunny Cove architecture. Intel Sunny Cove will likely first come out on desktop parts sometime in 2019. With it, Intel is making one of the biggest changes to its cores in many generations that will yield a bigger than 5% generation-on-generation instructions per clock performance increase.

Quick Recap on the Intel CPU Core Roadmap and Strategy

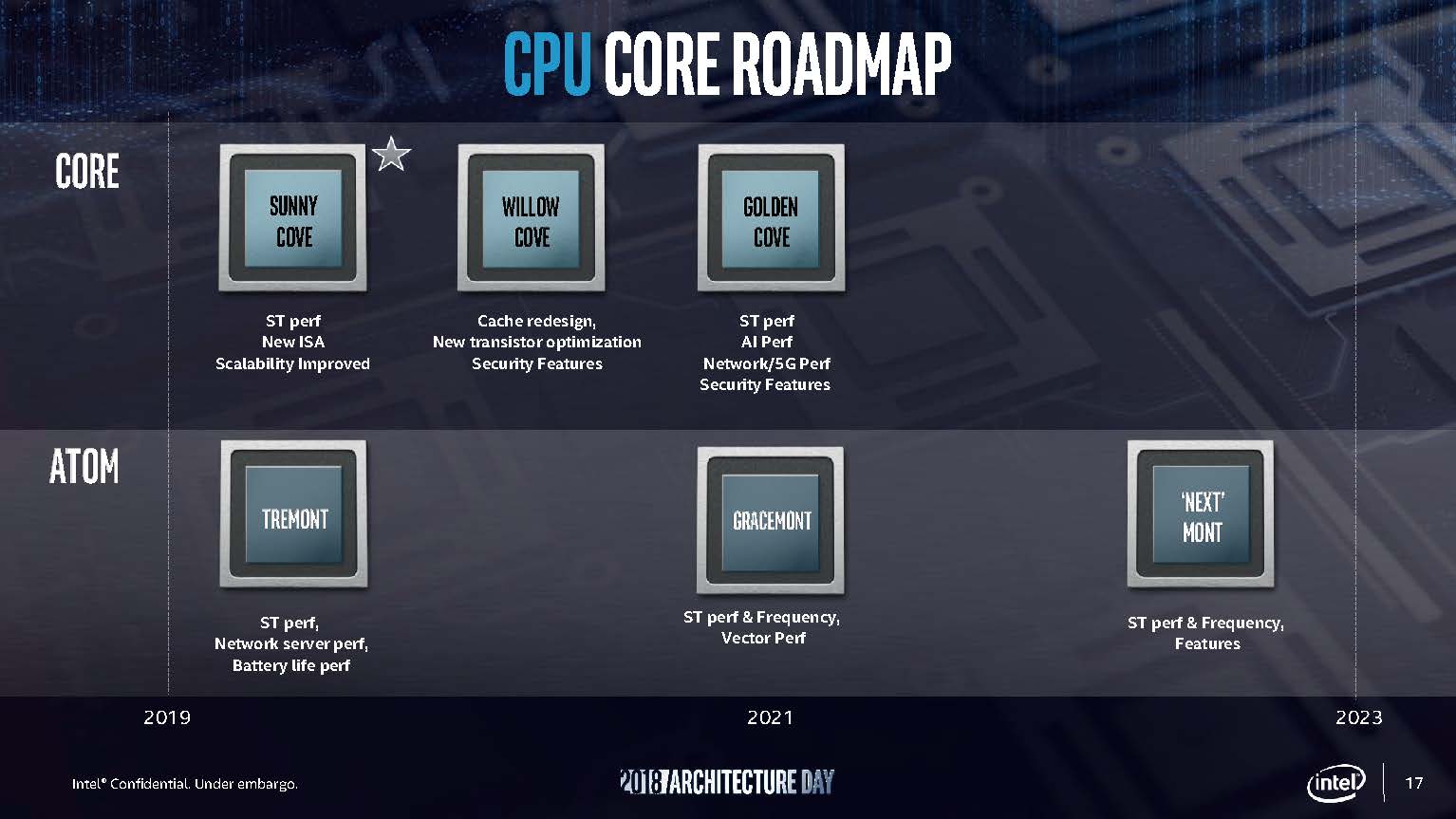

We had a piece on the New Intel Core Strategy Outlined At Architecture Day 2018. Check that out for more details. Two pieces of pertinent background information are that Sunny Cove is the next architecture expected in products for the 2019 year.

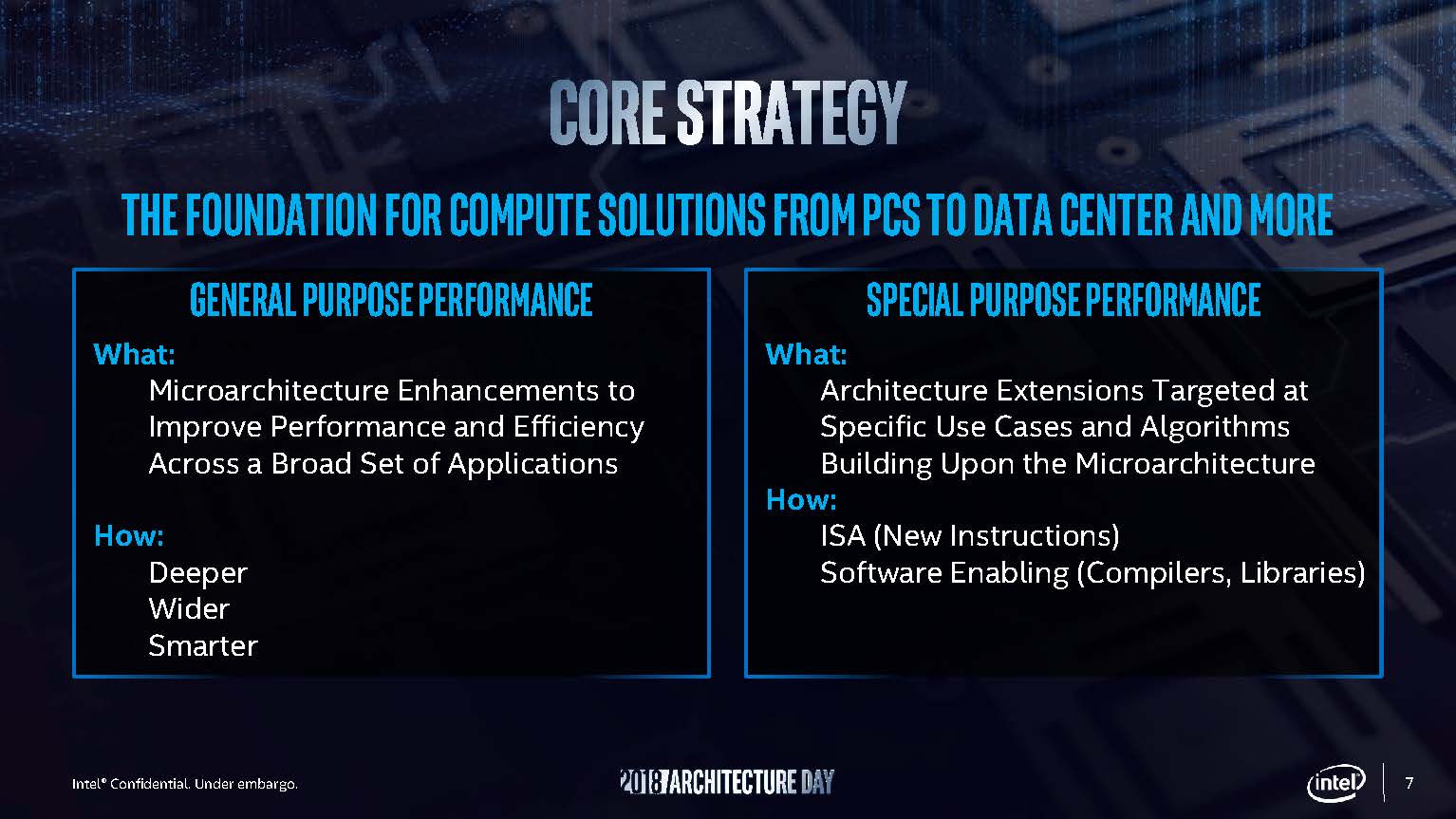

Sunny Cove will be followed by Willow Cove and Golden Cove successively. In terms of the goals for each, Intel is looking to increase general purpose performance (e.g. for unoptimized and single-threaded code) as well as increasing special purpose performance for things like AI inferencing.

Sunny Cove is going to have both types of improvements, along with some security enhancements. This is going to be the biggest microarchitecture update in years for Intel.

Intel Sunny Cove Microarchitecture

Intel Sunny Cove will be the biggest microarchitecture update in some time. Realistically, Skylake has been in the consumer and low-end server/ workstation market for a long time. In the server market, Cascade Lake has some improvements but is a much milder update over Skylake.

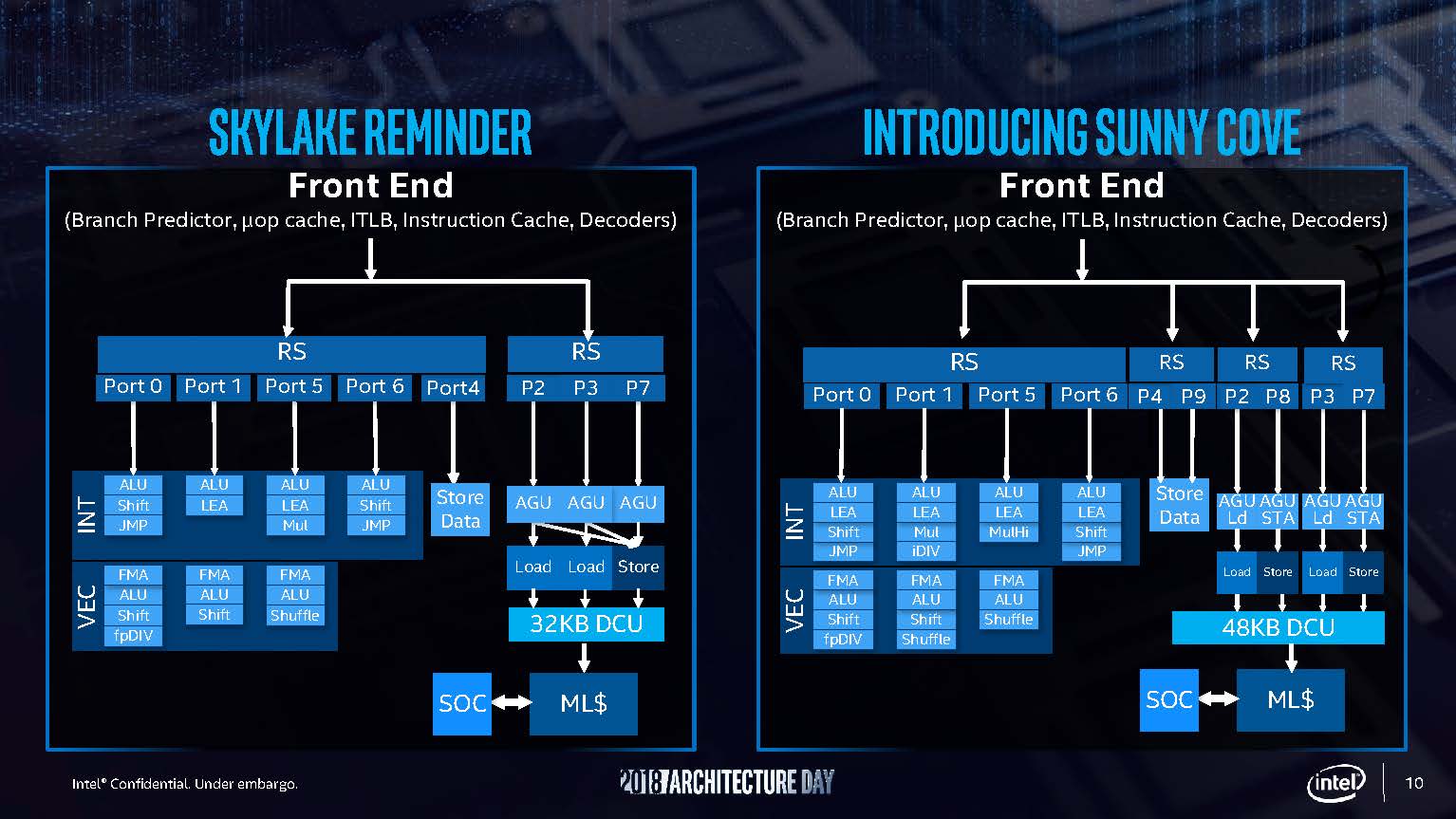

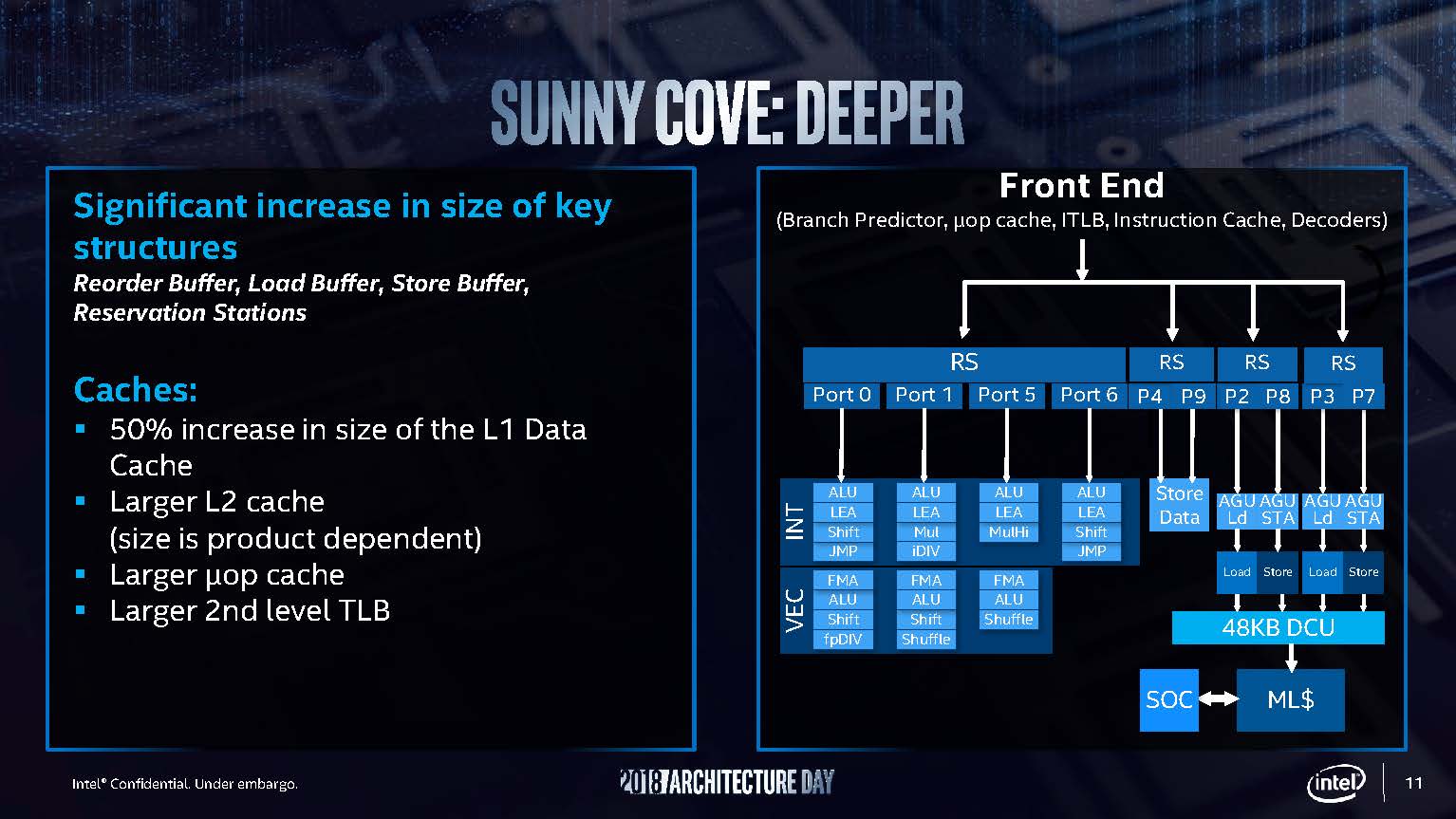

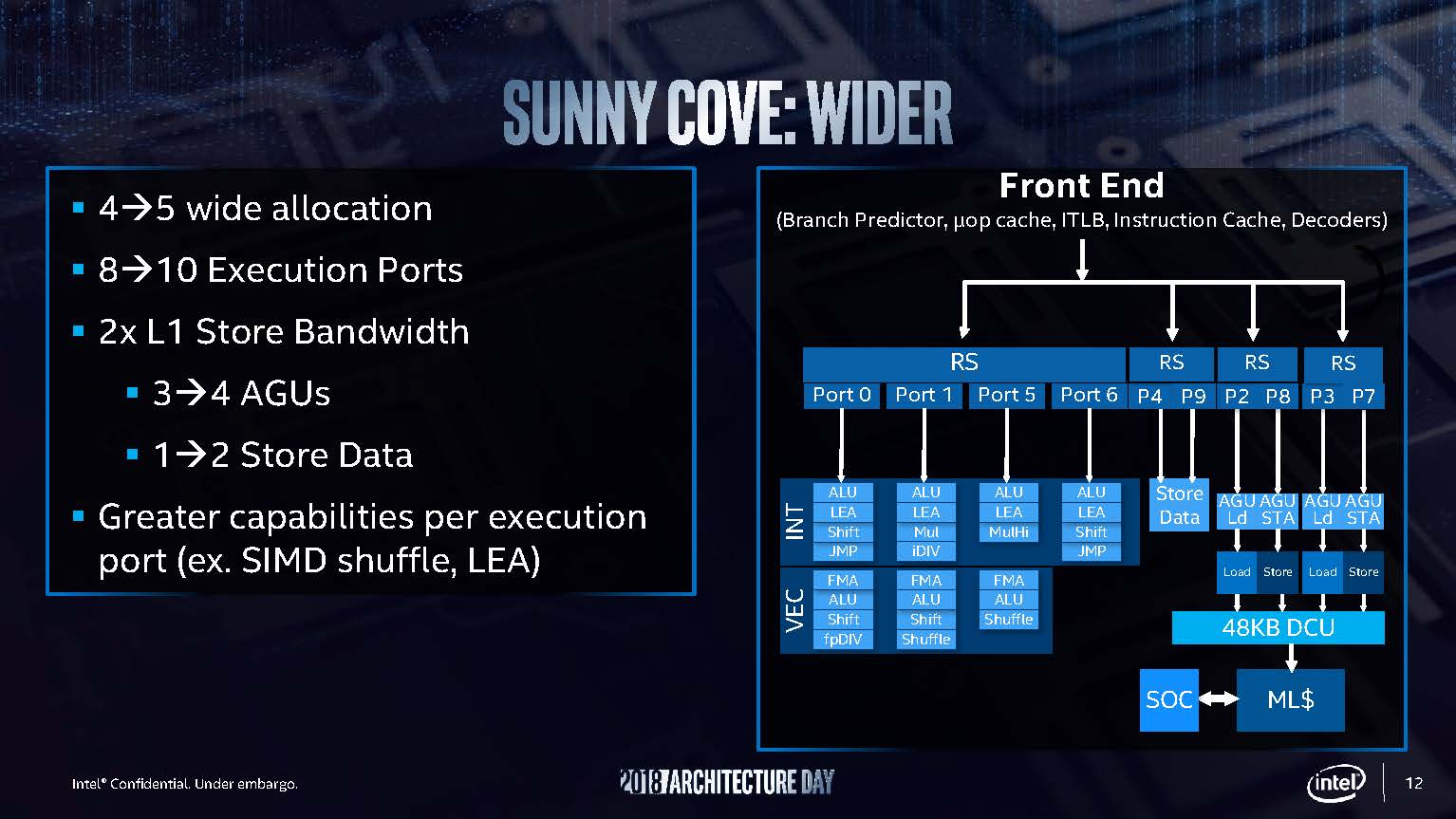

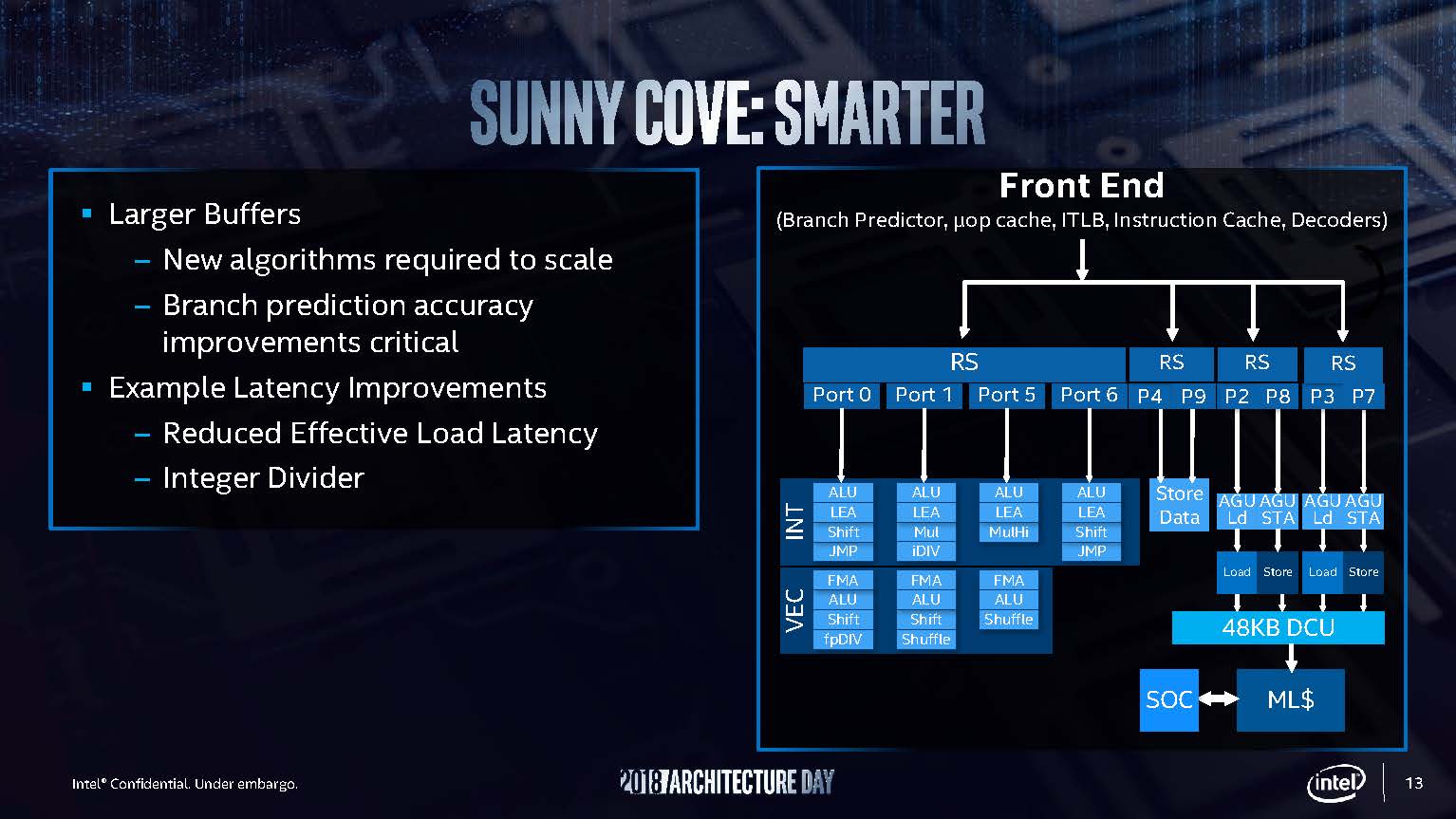

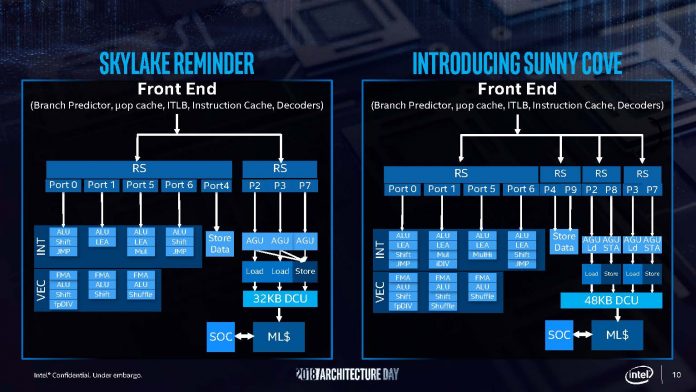

The microarchitecture is growing. Intel has made the reservation station structures much wider at four instead of two. Ports have gone from eight to ten. L1 caches on Intel CPUs are getting 50% bigger. This is the first increase since 32KB became standard over a decade ago. There is a larger micro op cache, larger second-level TLB. The L2 cache is set to get bigger. We were told that the L2 cache, like in today’s server and desktop parts, will vary based on CPU segment.

Intel Sunny Cover will go from 4-wide to 5-wide allocation while increasing the execution port count from 8 to 10. One of these extra ports is dedicated to storing data (P9) to take advantage of larger caches, the other is for memory access (P2, P8, P3, P7.) Beyond this, there are additional capabilities being added such as another SIMD shuffle (now two) and LEA units (now four.) LEA is often used for computing addresses and general purpose math.

There are also larger buffers in the design and a number of latency driven improvements in the microarchitecture.

Taking a pause here, this is going to be a big IPC impact, not a 3-5% increase as we have seen recently. A major increase in compute power is important because it has a direct impact on even unoptimized code. This is what Intel calls General Performance in its current Core Strategy.

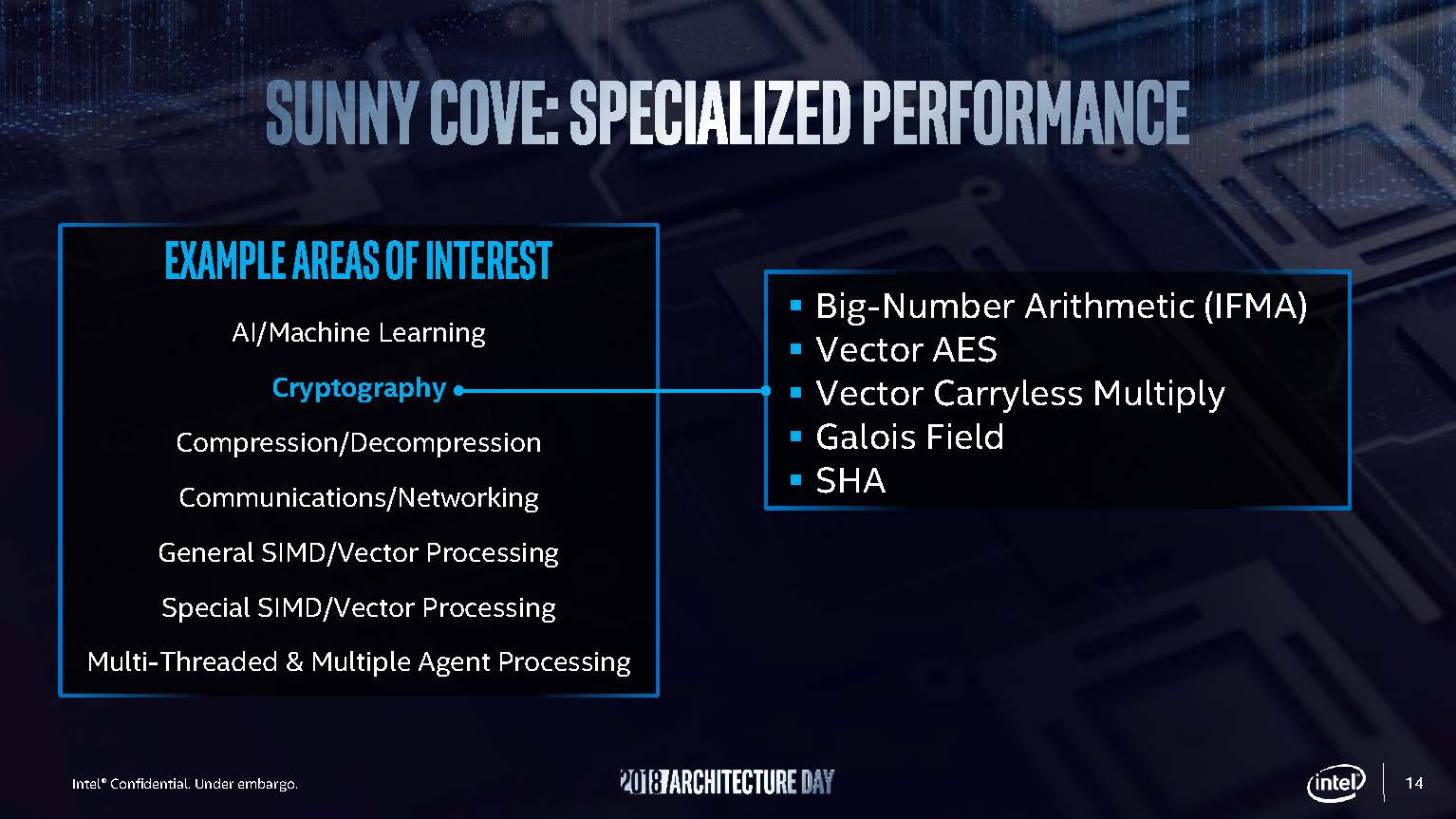

On the specialized compute, Intel Sunny Cove will introduce a number of enhancements targeting specific application domains and functionalities. Cryptography is going to be a hallmark of Intel’s security strategy so this will get a major boost.

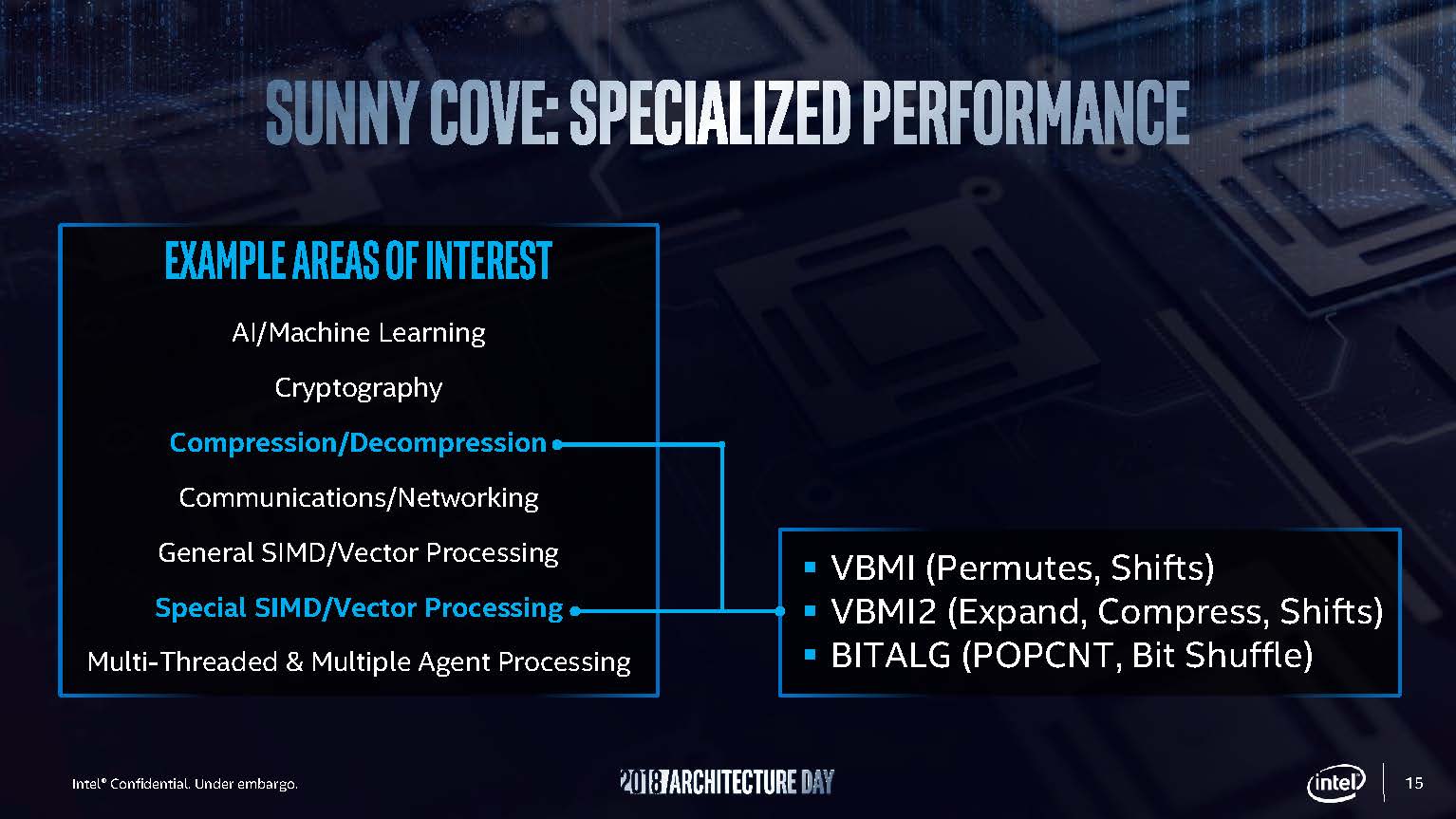

Compression is important because data is being compressed throughout pipelines these days in order to maximize the storage of expensive memory tiers. For that, Intel is also adding specialized instructions. Intel showed a 7-zip demo with 75% compression performance increase using some of the new Sunny Cove features.

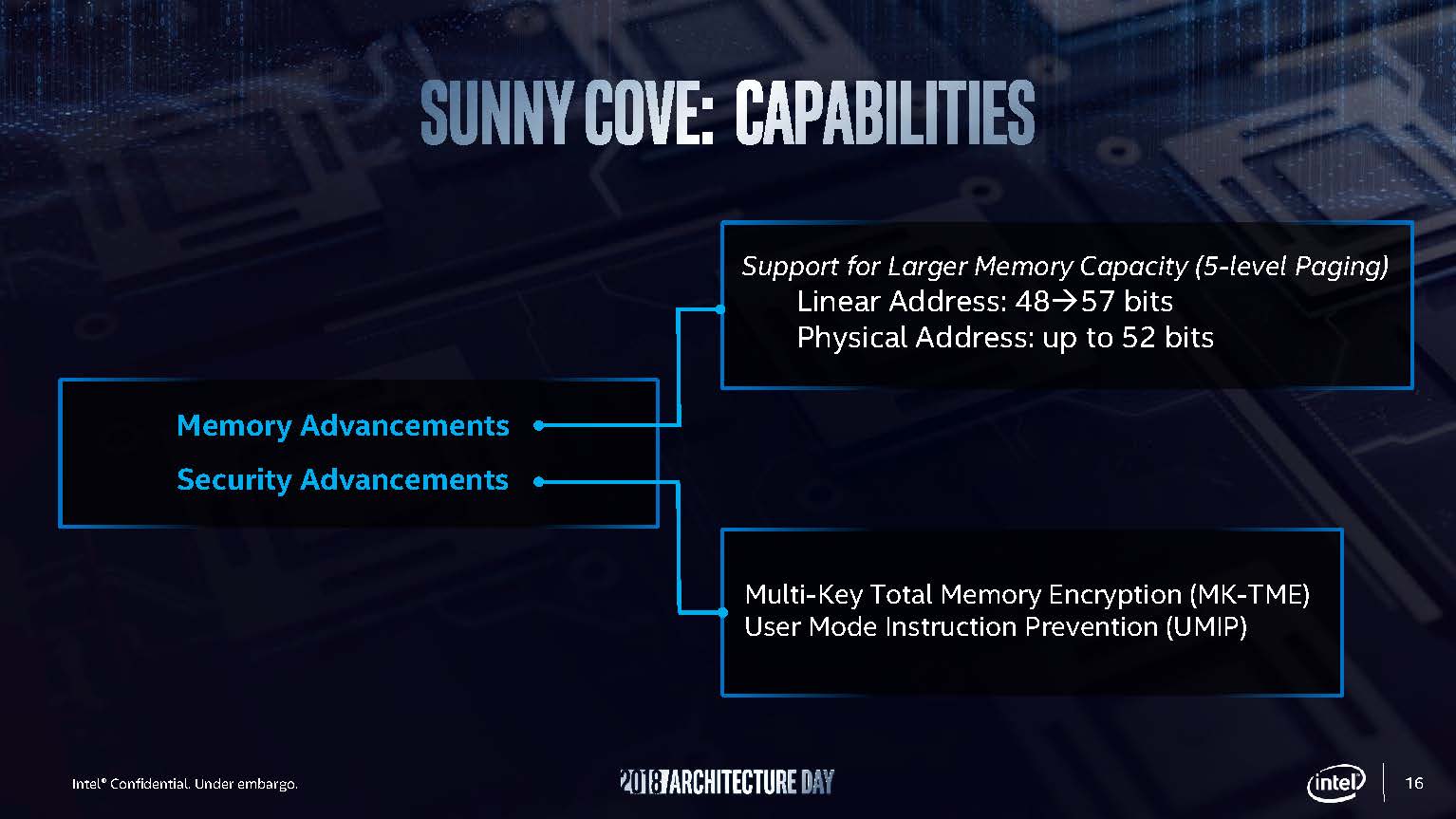

Other major capabilities are around memory and security. Here, we see the Linear Address space moving from 48 to 57 bits and the physical Address space moving up to 52 bits. This will have an impact as memory space will move from 64TB to 4PB. While we are unlikely to see 4PB in a single system soon, if interconnect technology improves alongside persistent DIMMs, it is not too hard to see 64TB becoming too limiting in the near future.

Along with these enhancements are security enhancements. The Multi-Key Total Memory Encryption will be very interesting to virtualization hosts and cloud providers. It will allow memory encryption using different keys per user. That will allow VM1 to use User1’s encryption keys while VM2 can use User2’s keys. AMD has been pushing secure memory encryption. If Intel is putting it in their roadmap, we see cloud providers have likely taken to the concept.

Final Words

Understanding many of our readers have little interest in microarchitecture, and simply want to know what this means for buying servers, the impact of these changes is simple. The general performance improvements are going to be much larger than 3-5% generation on generation. Post-Cascade Lake, you will not be able to simply take two CPUs of successive generations at the same clock speeds, multiply the performance of the previous generation by 4% or so and get very close to the performance of the next generation. Instead, we are going to see double-digit performance gains just from the improved cores on a clock-for-clock basis. Beyond that, Intel is pushing a series of application and domain-specific optimizations that software can be optimized to take advantage of to get even more performance.

Too bad we aren’t going to see Ice Lake in channels anytime in 2019, at least if the e-2100 launch has been any indication.

I think Icelake on Server is definitely a 2020 product. AMD has one year lead time to fight its way in.