At Hot Chips 30 we had the opportunity to talk to Akhilesh Kumar, the architect of Cascade Lake-SP and we had the opportunity to sit through the presentation. We covered much of this at the Intel Data-Centric Innovation Summit a few weeks ago but there were a few new disclosures at the show. The key theme seems to be that the Intel Xeon Scalable platform is not so “scalable” after all.

Cascade Lake Incremental Update over Skylake

First off, we want to thank Akhilesh. He did a great job in his briefing, his presentation, and the questions that arose afterward. He was in the unenviable position of being the chip architect announcing what amounts to a bug fix chip, at a chip conference, and instead of having to talk about Optane Persistent Memory. He displayed absolute grace in handling the task. The thrust of Intel’s message was simple: Cascade Lake-SP, from a compute perspective, is a bug fix chip.

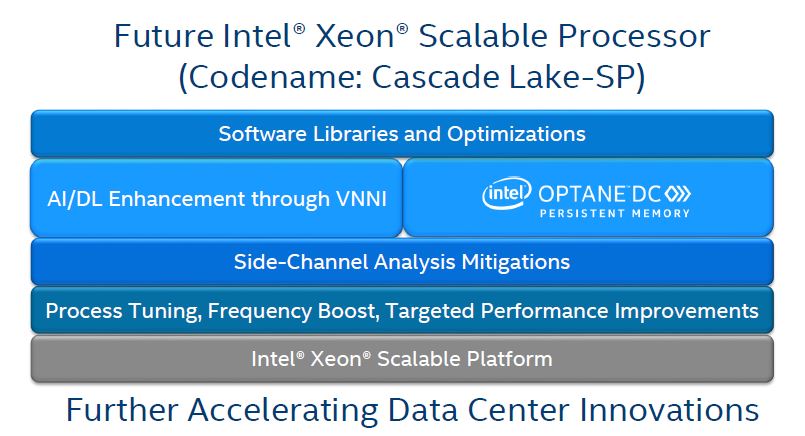

Here is the Intel Xeon Scalable Cascade Lake-SP summary. The platform and performance boosts are at the bottom for a reason.

We are going to work from the bottom up. Talking about the basic x86 core specs themselves, then moving up to the mitigations, the new VNNI inferencing extension, and Optane Persistent Memory.

Intel Cascade Lake-SP Base Specs

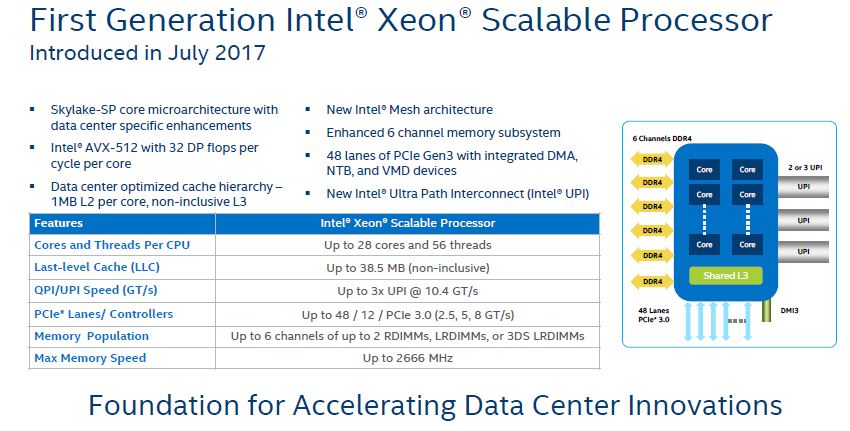

Here are the setup slides around Skylake-SP and the scalable platform:

We are not going to put much text here so that you can see the side-by-side with Cascade Lake specs.

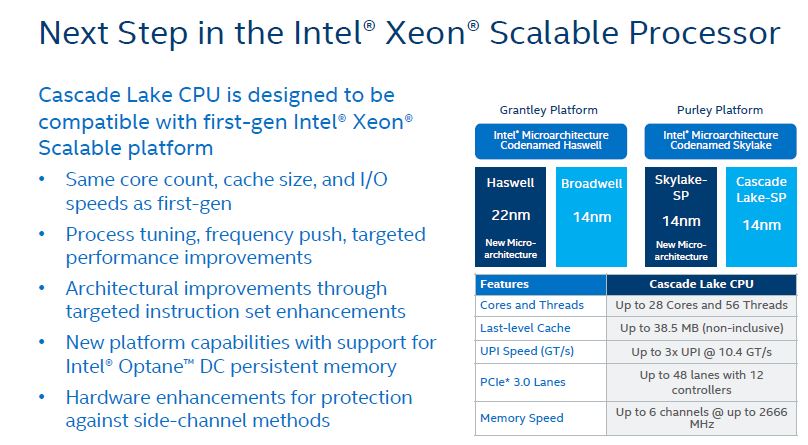

The first bullet is the eye-opener. We have known 28 cores were going to be the answer for some time. Cascade Lake-SP will offer the “[s]ame core count, cache size, and I/O speeds as the first-gen.” That means up to 28 cores maximum, the same size cache. It also means the same PCIe 3.0 x48 per CPU. DDR4 will be limited to 2666MHz as it is today. UPI for socket-to-socket communication will sit at 10.4GT/s, the same maximum as today.

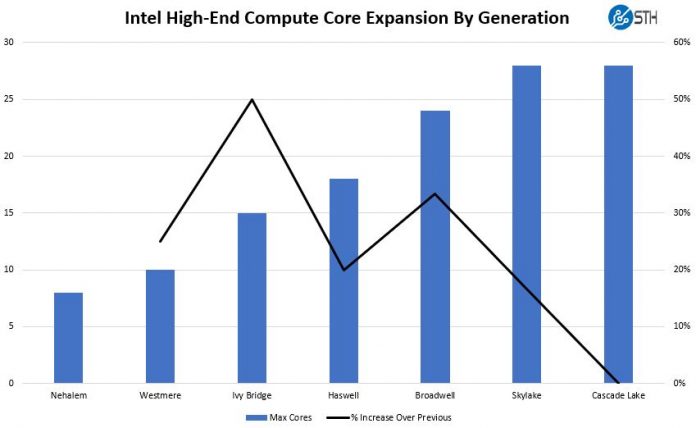

While Intel will have room for some additional speed bumps, it will have to add cores in another way. We think that if Intel increases core counts, it will add cores at a SKU level, much as it did between, say the Intel Xeon E5-2630 V3 and V4 generations. There the CPUs went from 8 to 10 cores at the same micro-segment.

Later in this article, we are going to show what that means for Intel looking across previous generations in the section “My Challenge to Intel.” Next we are going to look at some of the side channel mitigations, VNNI, and Optane Persistent Memory. Then we are going to wrap up with analysis and final thoughts.

OPMoF ???

Optane Persistent Memory over Fabrics. Need to be extra trendy!

This kind of sounds goodbye Xeon, hello EPYC2.

I thought this was going to be an Intel bashing piece but it really isn’t. You did a good job presenting the new parts first. I’ll agree that this isn’t going to keep everyone who is going epyc to stay Intel. Intel knows that too unless they know of some major security issue that’s not public yet and cascade fixes but amd can’t handle.

The Meltdown mitigation alone might be worth quite a lot in Performance for I/O heavy applications, and this is an area where the MCM Design of AMD is problematic. It’s going to be interesting to see if AMD manages to put more Cores on a die and perhaps also attach more memory channels and PCIe lanes, this would seriously diminish the last of Intels advantages.

Do i need a new motherboard when upgrading from Skylake Xeons to Cascade Lake xeons?? Would like to get a new Skylake Xeon SP motherboard (Supermicro, Tyan ??) and upgrade approx a year from now to Cascade Lake. The only thing keeping me from going Epyc is the Optane Persistent Memory feature…looks great for a fast OLTP sql database that fits within 4-8 TB…

Cascade Lake will use the same motherboards and chipsets with a BIOS update

It is going to take a while for IT Departments to adopt amd epyc. especially mission critical 24x7x365 operations to switch to a relatively new platform, from a company that has a less then stellar data center reputation. Core counts aren’t everything especially given certain software is licensed per CORE. So by Intel pushing forward and integrating new features and fixes that will filter in as IT Dept refresh cycles hit, this is a good. It would have been bad had they not introduced a refresh this year.

Totally agree with you Matthew, Intel has a stellar reputation these days, the leaks are all over the place, there have neverbeen more hacks on mission critical operations the last year and a half then ever before.

There have never been more speed decrease in a processor because of all the patches than ever bevor.

8 socket 28 cores is no problem with licenses per CORE, but 2 socket 32 cores is becomming a real problem and why do people need all those PCIe lanes anyway.

AMD are no saints but doing a pretty good job lately.

As EPYC has been mentioned a couple of times, while interested in it depending on your environment it may not be an option. While EPYC may be cheaper and faster, it also has higher power demands which could be a limitation for some.

“Just about everyone in the industry thinks that Intel Optane Persistent Memory (OPM) is going to be big.”

This is absolutely HILARIOUS with years of hindsight.