Intel is making another push with its FPGAs. This time, we have the announcement of the Intel Stratix 10 FPGA adding UPI support with PCIe Gen4. The company also talked about CXL and PCIe Gen5. Its first big launch customer is VMware, which we will discuss in a bit.

Intel Stratix 10 Adds UPI and PCIe Gen4

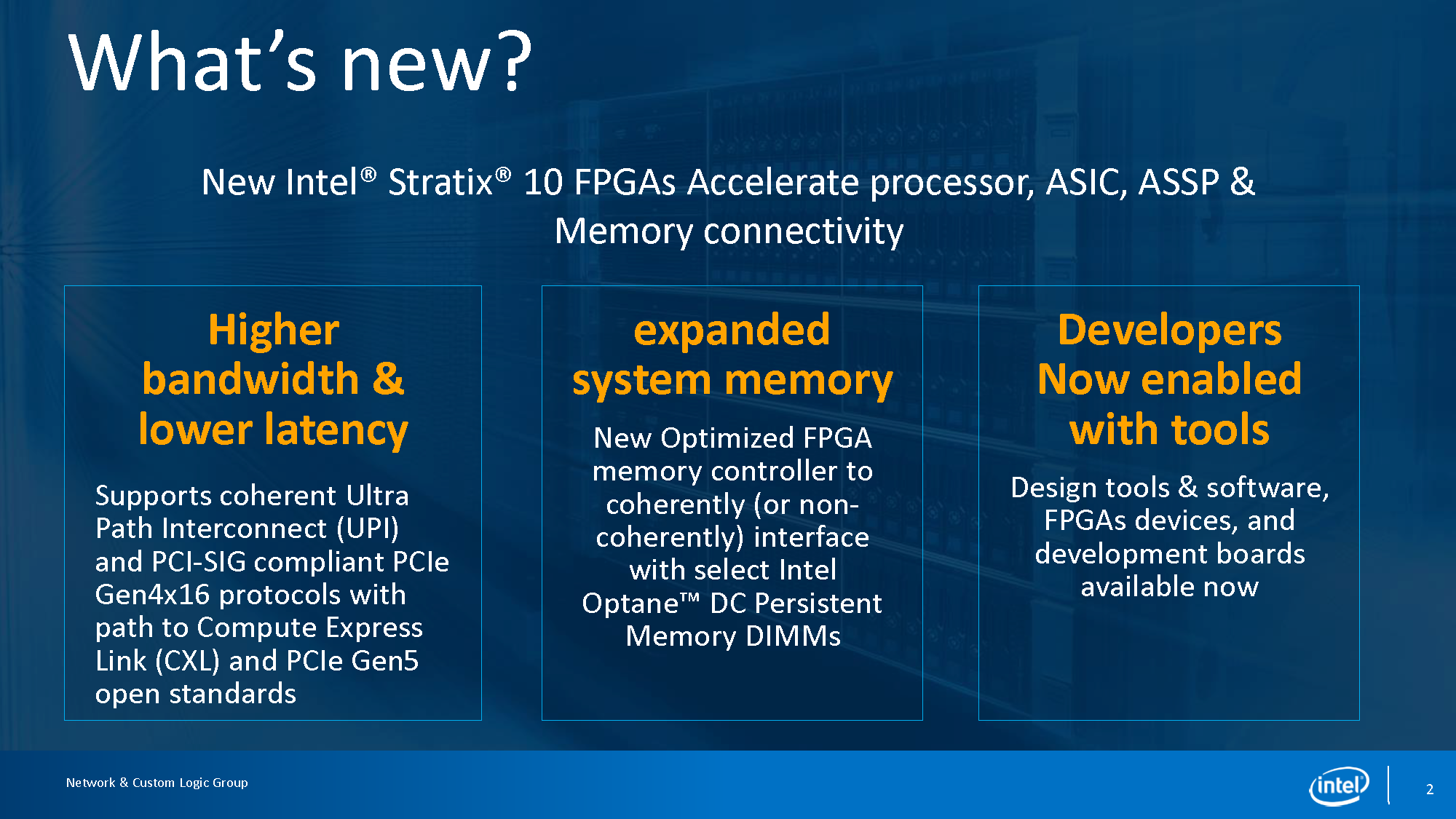

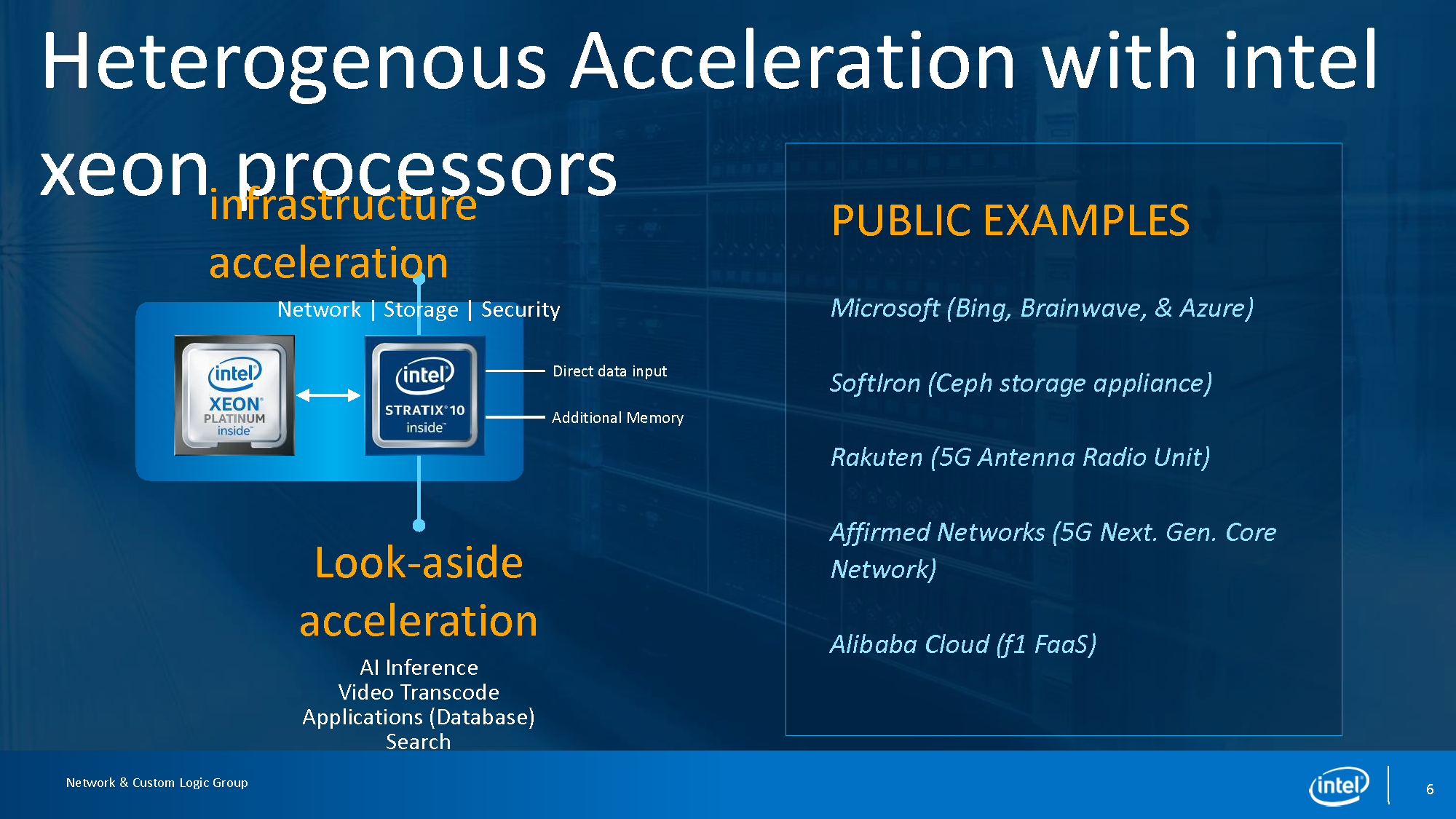

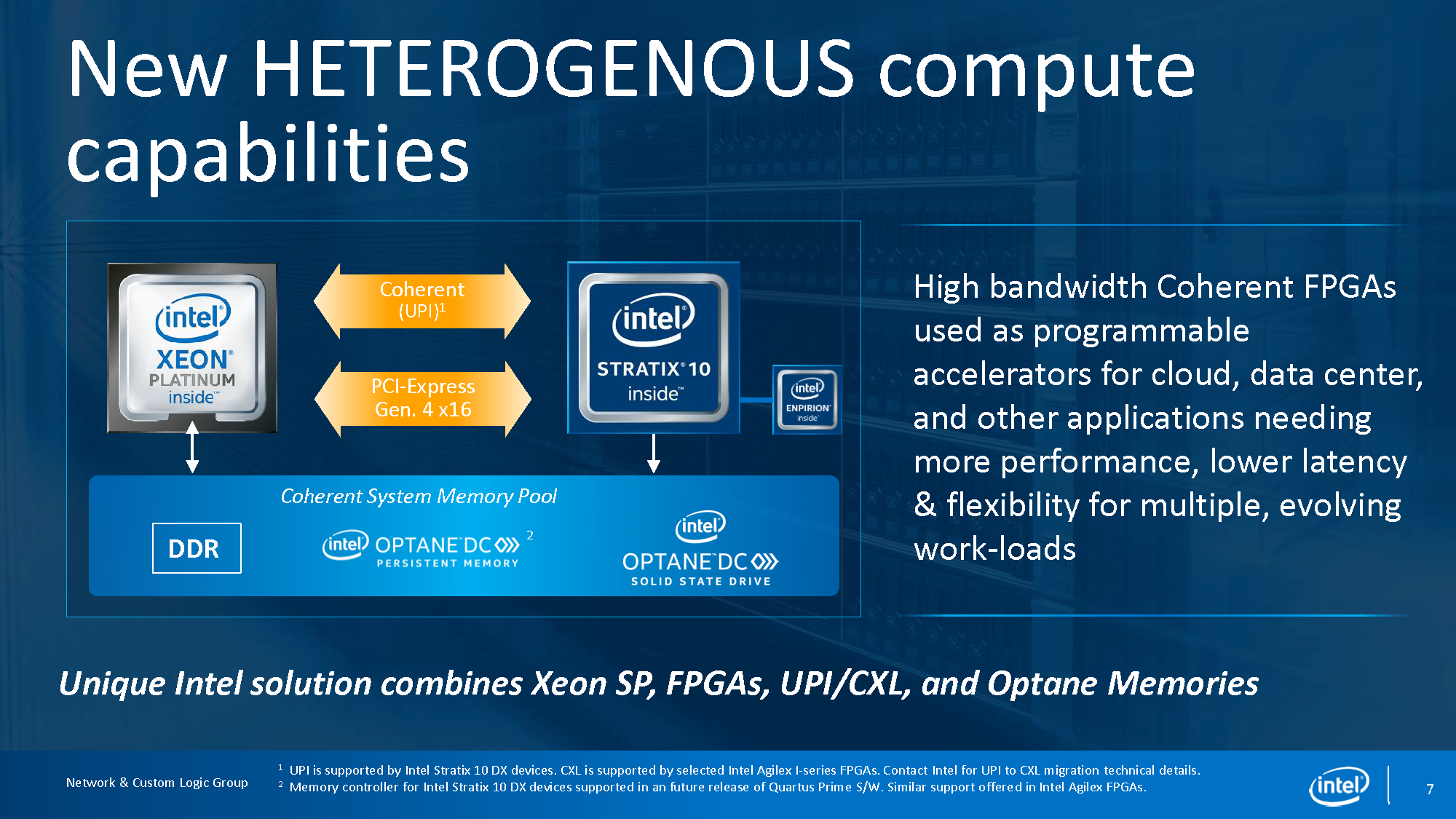

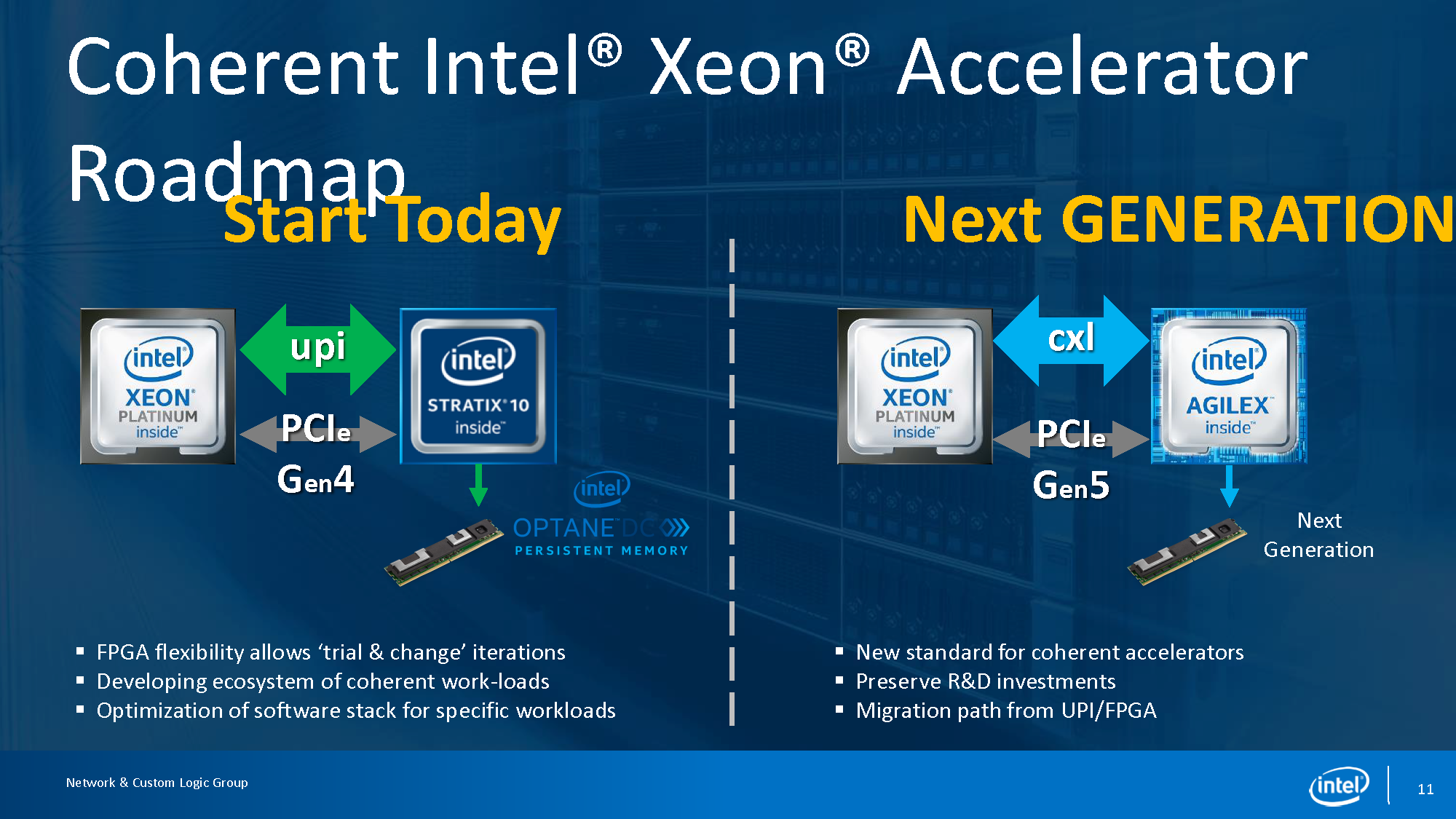

One of the key advantages of the Intel Stratix 10 FPGA family is the ability to combine programmable logic along with high-speed I/O and memory. With the new announcement, Intel is adding the chiplet capability to add UPI and PCIe Gen4 to the Stratix family. Ultra Path Interconnect, or UPI, is the cache coherent protocol that Intel Xeons use to create one large coherent system in common 2 socket and 4 socket servers. By adding UPI to the Stratix 10, it allows the FPGA to pull directly from memory attached to the Xeon CPU’s memory controllers. That can include Intel Optane DC Persistent Memory Modules (DCPMM.)

PCIe Gen4 doubles the bandwidth which allows for faster communication between the FPGA and other devices. Intel said that these products had samples and developer resources out. Later, Intel said that these would go into volume production in 2020 for companies like VMware. We are going to talk about that next. With PCIe Gen4 and UPI in 2020, we think this makes more sense as an Ice Lake next-generation Intel Xeon companion. AMD EPYC 7002 processors ship with PCIe Gen4 but Intel Xeon does not yet have a Gen4 capable part. PCIe Gen4 will give 2x the PCIe bandwidth which is important and we have seen practical benefits such as being able to handle 200GbE in a single PCIe x16 slot.

Looking ahead, Intel says that PCIe Gen5 with Intel Agilex is going to further build on those capabilities. Instead of using UPI, in the PCIe Gen5 generation of silicon, Intel will adopt CXL. Intel said it may bring UPI to Agilex and 10nm, but for now, the plan is to use CXL.

The Intel FPGA VMware Announcement Non-Announcement

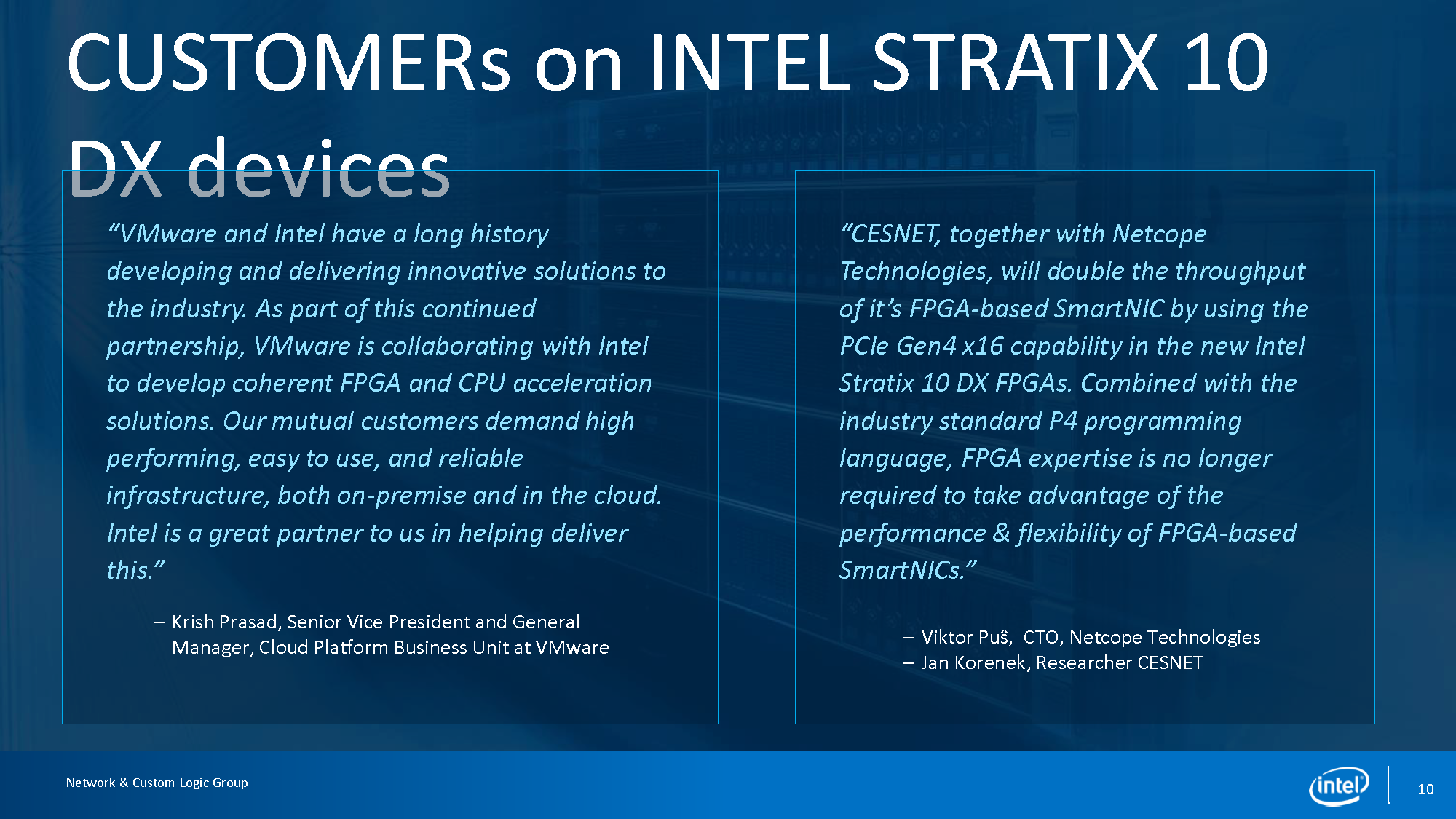

VMware was a part of this announcement and we were told that we should expect something next year. FPGAs tend to have a much longer announcement to general availability periods than CPUs. Given the timing, we expect to see something at VMworld 2019 on the Intel FPGAs plus VMware.

One potential use is a VMware analytics platform. At this year’s VMworld the company touted being an analytics platform for all of an organization’s data. VMware needs to move beyond being seen as a virtualization platform. Instead, it is focused on being the orchestration for apps and data.

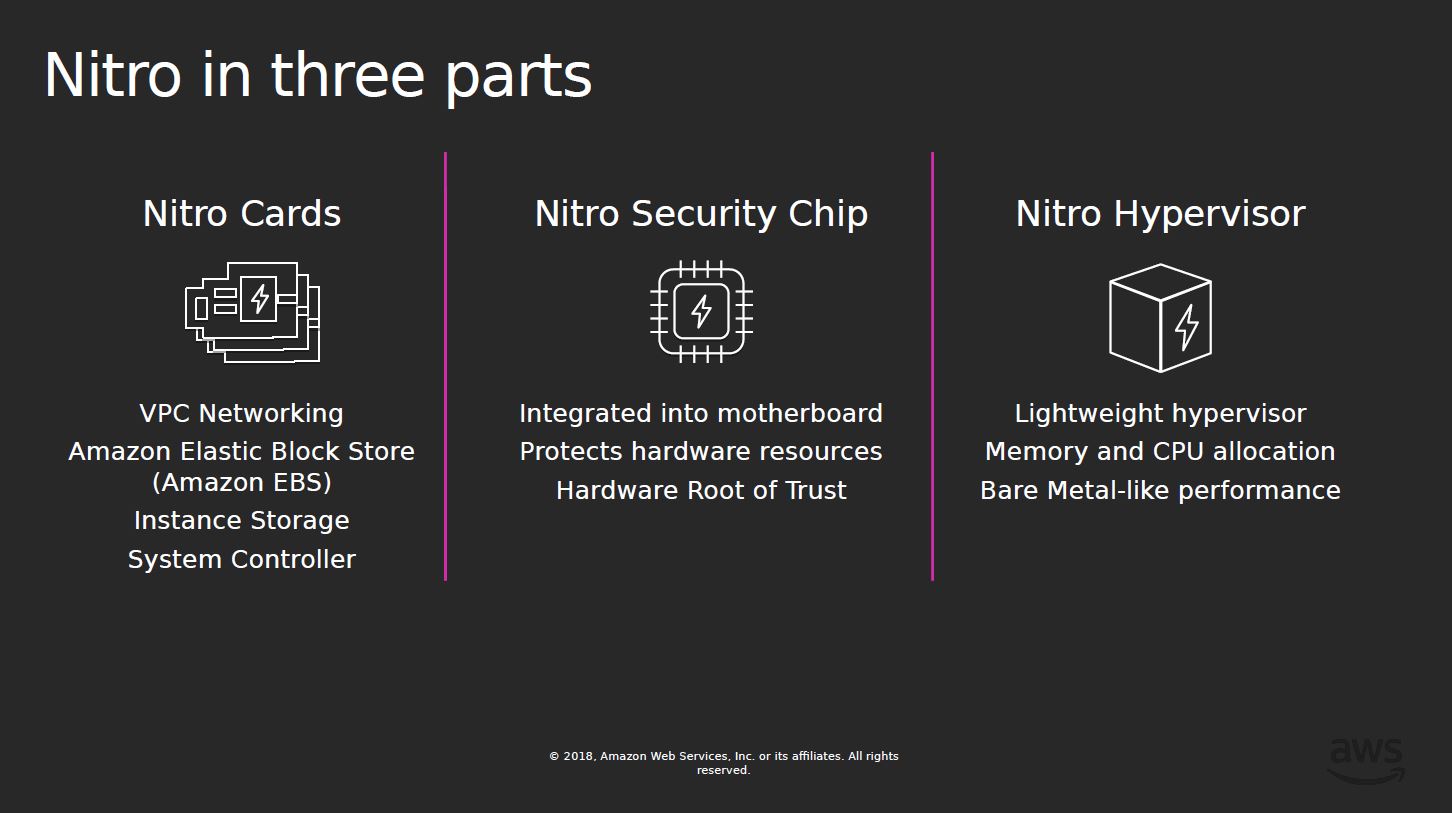

The company also desperately needs an answer to the AWS Nitro as we covered in Mellanox Bluefield-2 IPU SmartNIC Bringing AWS-like Features to VMware. Having a cache-coherent PCIe Gen4 FPGA in its stable helps to that end.

Final Words

The fact that Intel is mentioning VMware as an early customer is very telling. As was clear at VMworld 2019, the company is moving to run apps and data on any infrastructure cloud or company-owned. If VMware is saying they will be using a cache-coherent protocol with an FPGA in 2020 infrastructure, that means it will necessarily need to have key public cloud partners running the same infrastructure in their cloud deployments. While Intel named VMware, by the PCIe Gen5 and CXL era, we expect all major cloud players will have CXL enabled accelerators.