Today at Intel Innovation 2021, the company is unveiling its new Alder Lake architecture. This is a huge deal. Alder Lake is bringing the company’s hybrid architecture along with the enabling technologies to the client market. There are other technologies as well such as DDR5 and PCIe Gen5 making their debut in this generation as well. There was a bit of a debate on whether to call this the launch event, but since availability and benchmarks will follow at a later date, we are going to call this a “details” piece.

Intel Alder Lake Details at Intel Innovation 2021

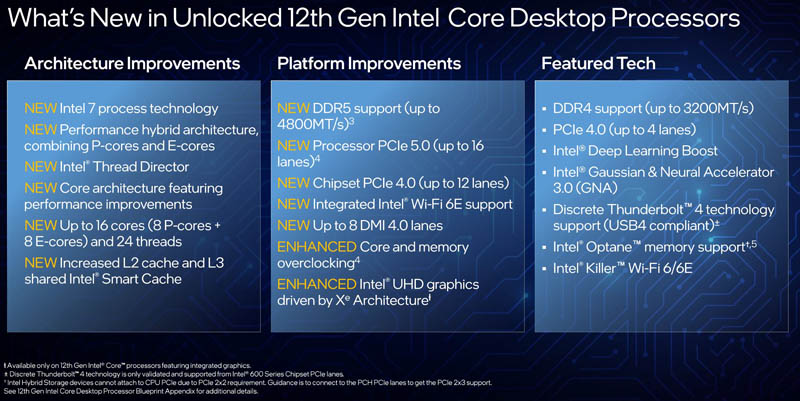

Here is the list of new features, and there are clearly a lot. This generation will see sixteen cores from Intel, but with a big caveat. Let us get into the details.

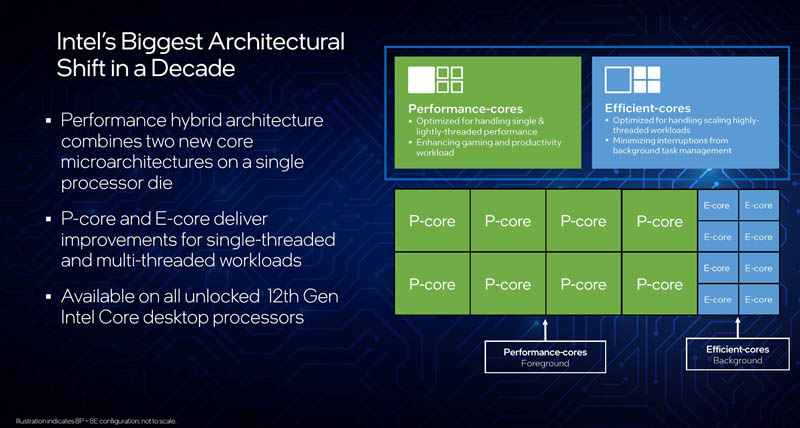

Intel says this is its “biggest architectural shift in a decade,” and it certainly is. We previously did features on the Intel Golden Cove Performance x86 Core and the Intel Gracemont Efficient/ Low Power x86 Cores. Alder Lake is bringing the traditional high-single thread performance Core cores (P-core) plus the new Atom efficient cores (E-core) into a single processor. The benefit is that Intel can fit roughly four efficient cores in the die footprint of a single performance core.

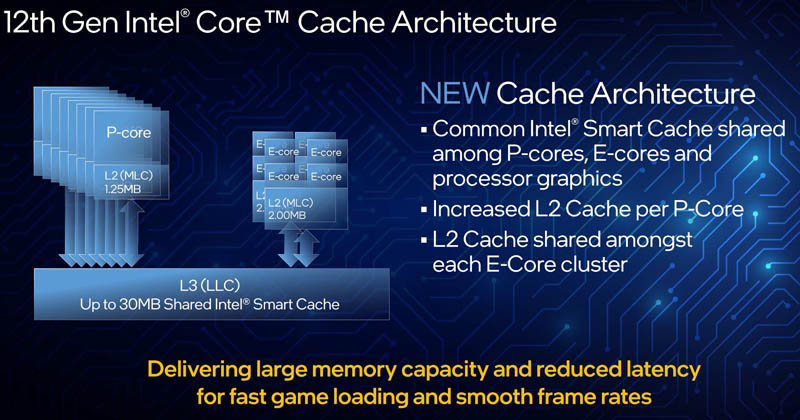

There are certain technologies that will need to be enabled to make all of this work. For example, each P-core gets 1.25MB of L2 cache while each cluster of four E-cores gets 2MB of shared L2 cache between them. Then, they all have access to a shared L3 cache. Remember that in previous Atom designs, we had L2 cache but not necessarily L3 cache so this is a big change.

Of course, there is another major challenge. Threads need to be scheduled on both the P and E cores. Intel calls its technology Intel Thread Director, and Windows 11 will support this. The reason this is important is that having two different types of cores requires more intelligent placement, otherwise there can be a big performance impact. In a week or so when benchmarks start coming out, expect to see a stream of stories that say “XYZ app slow on Alder Lake” as folks find cases where threads are not scheduled properly. Realistically, this is something that will get better over time, so we expect a few early sensational stories but that over time it will stabilize.

The other interesting thing is that this allows for different form factors because Intel can scale the P-cores and E-cores to meet different packaging and thermal envelopes. For example, it can make a 10-core processor, like the Apple M1 Pro and M1 Max except for Intel’s image here shows 8x E-cores and 2x P-cores whereas Apple has the opposite ratio.

One other quick note, and this is especially visible on both of the mobile diagrams, is that the cores are actually a relatively smaller size compared to the entire chip. At least, the cores are not 90% of the chip. Instead, all of the other functionality that is built into current SoCs such as graphics, I/O, and so forth actually take up a ton of die area. Often when chips are discussed, it is in terms of cores, but that is only one function of a modern SoC.

Intel Alder Lake Application

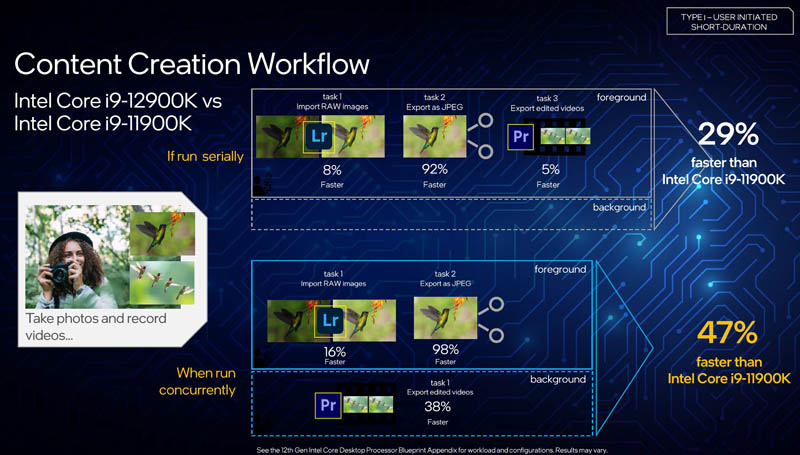

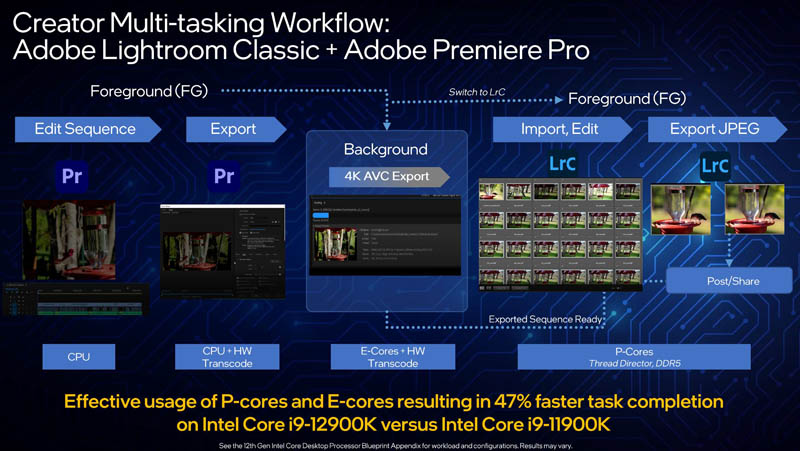

Putting this hardware into use, Intel says gaming tasks can run in the background, but let us look at the content creation workflow. Here, we can see that having new cores means that Intel can be faster than its previous generation, but by offloading video export to the background it can speed up things to a much greater degree.

As a quick aside, this is what I often do every day working on STH content. Adobe Lightroom, Photoshop, and Premiere Pro are open at almost all times for me along with Excel and a web browser. While the below may seem redundant at first, the item to keep in mind here is that below the E-cores are using hardware transcoding using the Xe GPU hardware. That is a great example of where having smaller cores to leverage acceleration on the SoC can pay large dividends.

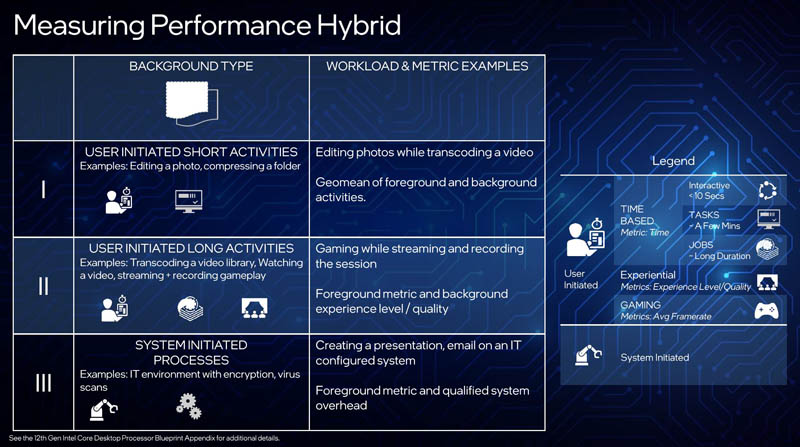

Instead of showing a bunch of gaming benchmarks that Intel put out, I wanted to focus on something that is important, and important in a broader context. Now that Intel has 16 core processors, plus accelerators, it needs to explain how one will get gains. The focus of Intel’s marketing deck is actually on multi-tasking rather than synthetic benchmarks that measure pure integer or floating-point performance of cores. This is actually important beyond just the desktop. A modern server often is running a number of containers or VMs simultaneously instead of a single big job. We have been working to bring more of these types of workloads to STH on the server-side for some time. What is more important here is that performance of not just Alder Lake, but also the Apple M1 Max silicon, and future CPUs will be dictated by mixes of workloads instead of just raw integer performance.

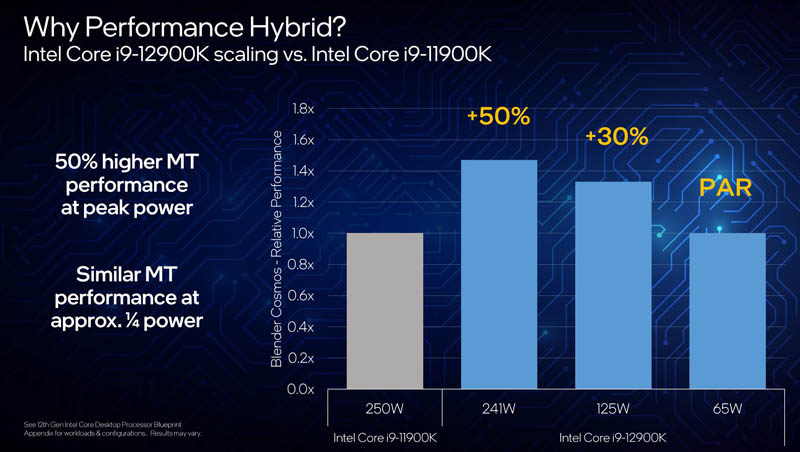

The overall gains here Intel is getting two benefits. First, it is transitioning to Intel 7 part of the company’s new naming scheme. We covered this in our Intel Accelerated Manufacturing Node Names Changing piece. Second, Intel is getting more cores and is able to drive more aggregate performance since the eight new E-cores are much smaller.

Overall, Intel is excited about this (as are we) since it is offering a new process node and a hybrid core design that is going to do a lot to change Intel’s value proposition in the industry.

Intel Alder Lake Platform

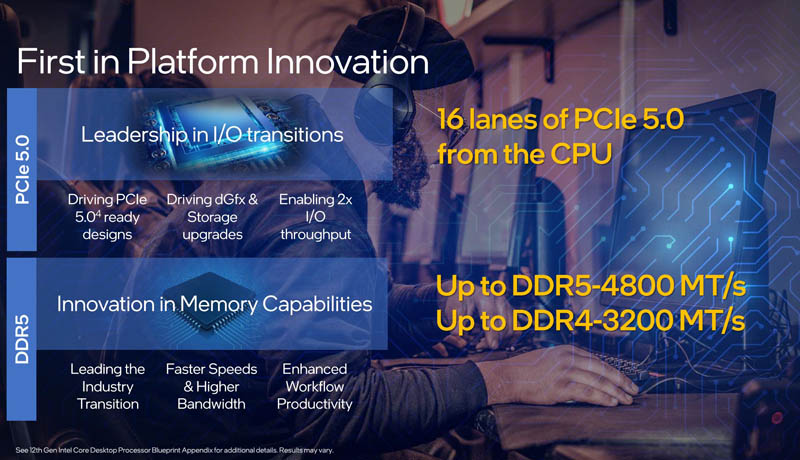

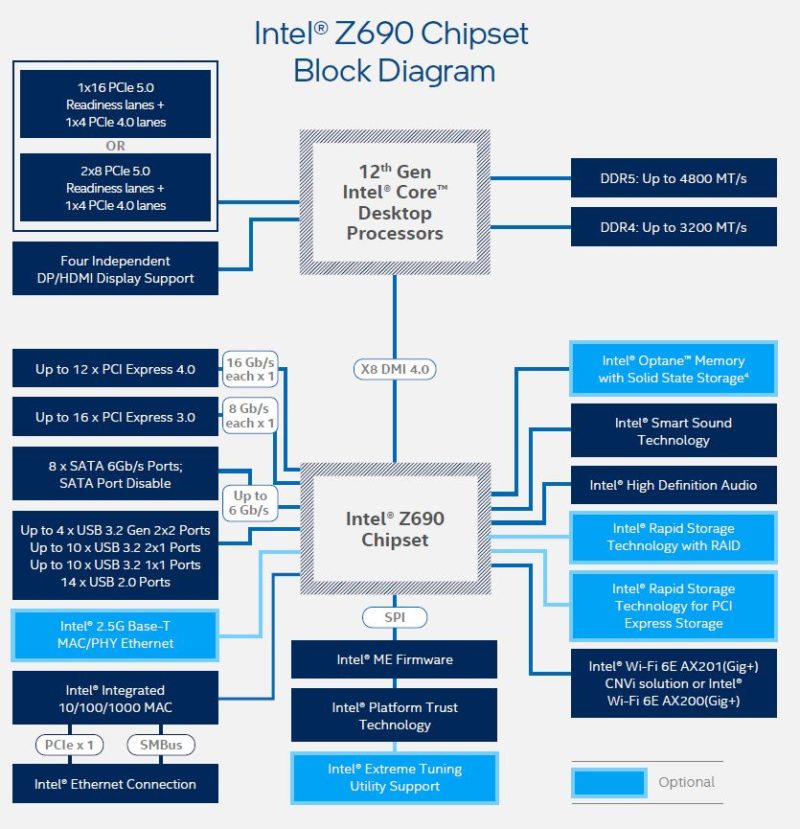

In terms of the Alder Lake platform, we are seeing a lot more innovation. While Intel was very late to PCIe Gen4 (but early on DDR4), it is changing the narrative here. It is adopting DDR5 and PCIe Gen5 ahead of AMD and others. As a quick note, the 16x PCIe Gen5 lanes are validated for GPU and storage only at this time, not networking (citation in the footnote of subsequent image.) Hopefully, this becomes a path to test early 400GbE adapters in the near future.

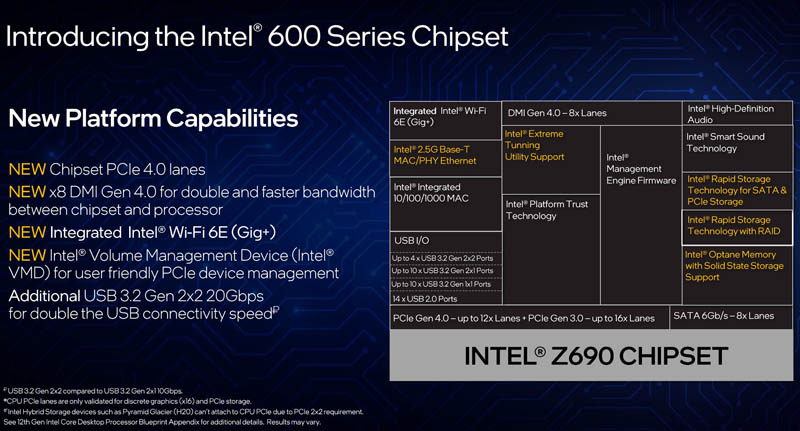

Along with this, Intel also has a new chipset. This new chipset is now PCIe Gen4 based with a few new features such as integrated WiFi 6E and PCIe Gen4 lanes with a higher-speed backhaul to the PCH.

Here is the diagram. Intel is pushing its partners to add 2.5GbE to its platform, but the standard is still Intel i219 1GbE. Hopefully, Intel just makes the move at some point since it would be a cheap way to get a 2-2.5x improvement on a platform.

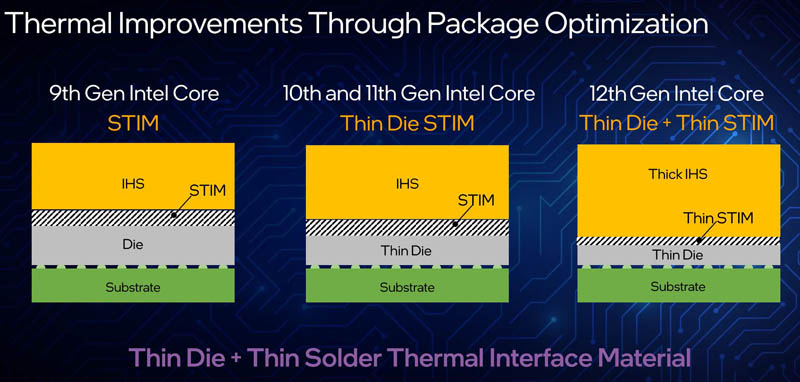

There are a few other technologies happening here. One is that Intel is offering overclocking. Overclocking has stagnated quite a bit as CPUs have been doing this automatically making gains significantly less for 24×7 operation. On the other hand, Intel is changing its die and thermal interface material to be thinner on its new generation, potentially allowing for better cooling. That has the impact of allowing the chip to continue seeking higher clock speeds more often.

Overall, we get some nice enabling technologies. here.

12th Gen Intel Core Unlocked SKUs

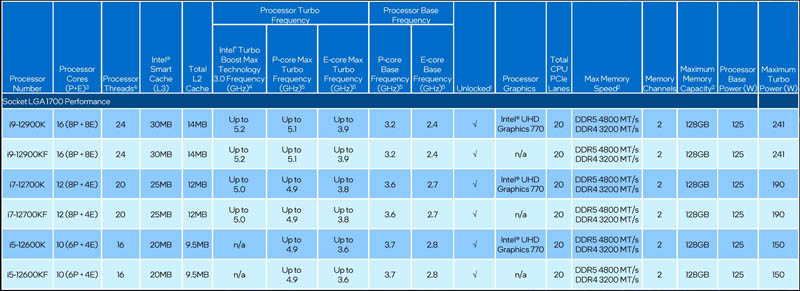

In terms of the SKUs, these are the initial SKUs that are being offered. One will note that there is DDR4 and DDR5 support. The motherboard will have to be one or the other. Given the price premium for DDR5 as a new technology, some may opt for the lower cost memory in the platform.

One can see the power numbers have quite a range, especially with turbo frequencies. We also will note that we still only get two memory channels and 128GB of memory capacity, the same limitations that have been around for generations now.

Final Words

Overall, this is a very exciting announcement from Intel. Alder Lake is a more modern design. As a result, it is also one that we are excited about since we get PCIe Gen5, DDR5, as well as a new hybrid core architecture. It feels a bit strange given we just started reviewing the Xeon E-2300 Rocket Lake-E series for servers and yet we see Intel massively revving its desktop line based on largely the same underlying product family. Still, the idea of having both P-cores and E-cores or many E-cores is a tantalizing proposition for many segments of the server market.

We will have Core i9 and Core i5 reviews after the embargo lifts and as soon as we can, but it is going to be a wild November.

Cool! So now, let’s wait and see ADL derived Xeons E-24xx and then next years SR for server and smaller workstation. Intel seems to finally catch some wind…

Still only 16x PCIe lanes? Hard pass.

Exciting how they upped the PCIe game, especially with more connectivity through the PCH. PCIe 5 is probably overkill at this moment but in the future might allow more cards with fewer lanes. I’d be very interested in a Xeon based on this.

One potential problem I see is that storage speed is constrained by encryption performance in the CPU – on my Tiger Lake Laptop it tops out at ~5GB/s per Core for AES-XTS with 256bit key. That’s where an accelerator could shine since a lot of CPU time is spent on encryption these days.

This is also the first time in a long while that Intel released the Desktop product first for a new architecture.

I’m confused on why PCIe lanes would not be validated for networking. A PCIe lane is a PCIe, isn’t it? Since it’s agnostic to the data it transports, why would Intel make a distinction as to how the lanes can be used? Is it a retimer/latency thing?

re: … benchmarks will follow at a later date …

I take this Intel embargo to mean: entirely ignore these not-really-a-launch slides (which are free of any real technical detail), and wait for the benches from non-NDA sites who test with production sand.