At Intel Architecture Day 2020, the company discussed more about its Xe GPUs that will arrive later this year. Since the Architecture Day 2020 was driven by Raja Koduri, Intel’s Chief Architect, who has a strong GPU background, this was clearly a subject he was keen to discuss. Hence, Raja and the Intel Xe HP GPU tile make it into our cover image.

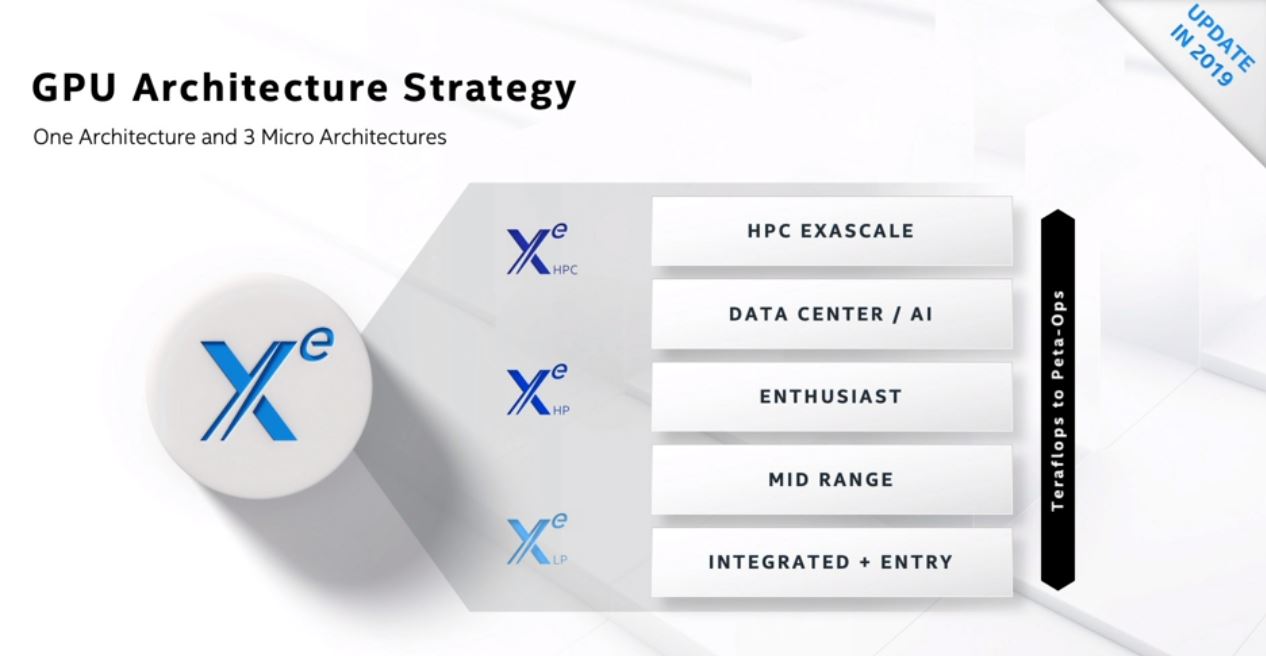

Intel Xe GPU Strategy Update

Intel showed off its 2019 GPU strategy with product lines focused from integrated graphics to HPC GPU products.

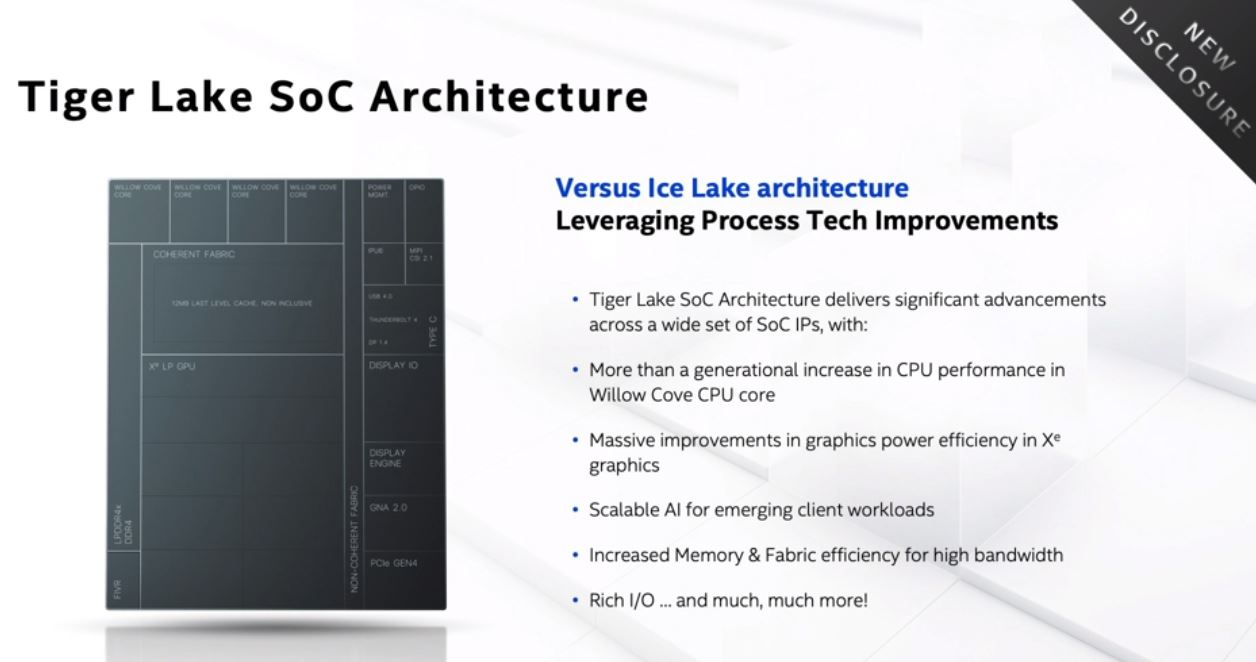

Intel released a lot on its new Tiger Lake SoCs during the event, but more details will come with the imminent launch. What we can say is that the new GPUs are using new Willow Cove cores, PCIe Gen4, and importantly, they are a launch vehicle for the Intel Xe LP journey for the Integrated and Entry segments.

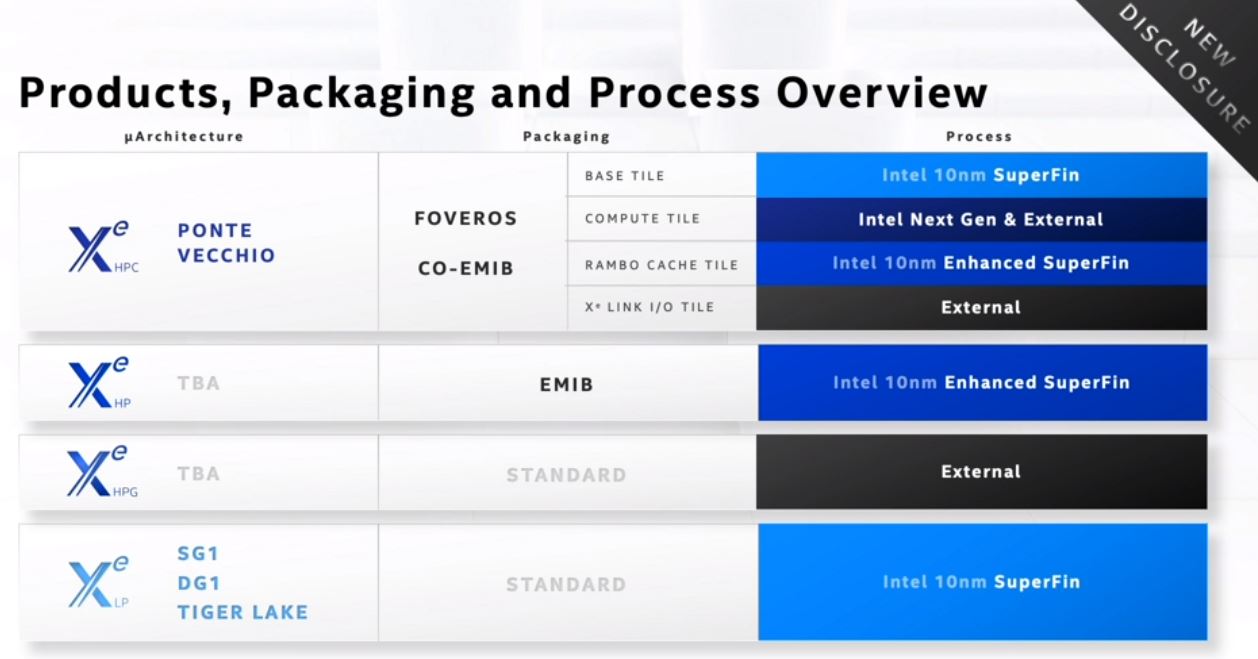

As part of the Architecture Day 2020 disclosures, the company is showing off its plans beyond Tiger Lake. We can see Ponte Vecchio, the HPC exascale product that uses features such as 3D FOVEROS, CO-EMIB, and its RAMBO Cache.

The company says that its HP products, which it disclosed more on, will use EMIB and be on a next-gen 10nm Enhanced SuperFin. Intel is replacing 14nm++++ with names like SuperFin and Enhanced SuperFin. Our hope is that we eventually see a “10nm Enhanced SuperDuperFin+” product one day (this is being said in jest if that is not clear.) Let us get into some of the disclosure highlights.

On the HPG products, we expect these to use GDDR6 memory and Intel is saying that they will be fabbed externally so not on an Intel process. These GPUs are targeted at gaming segments.

Intel Xe LP GPU

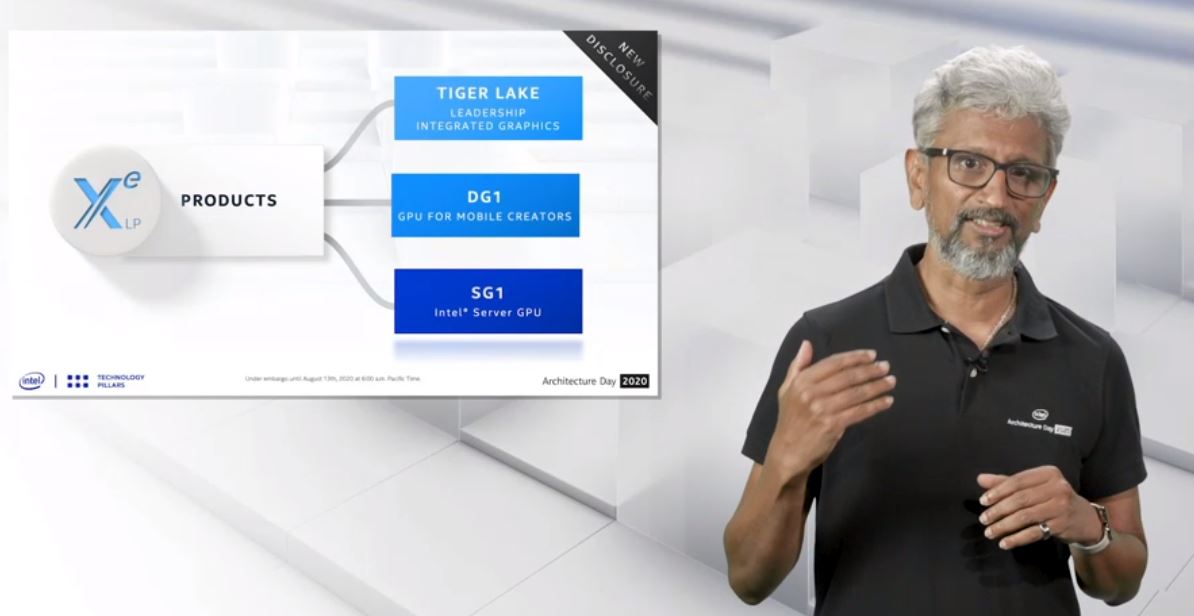

The Intel Xe LP underpins its Tiger Lake integrated graphics. This is a significantly enhanced integrated GPU offering that represents the volume/ entry market.

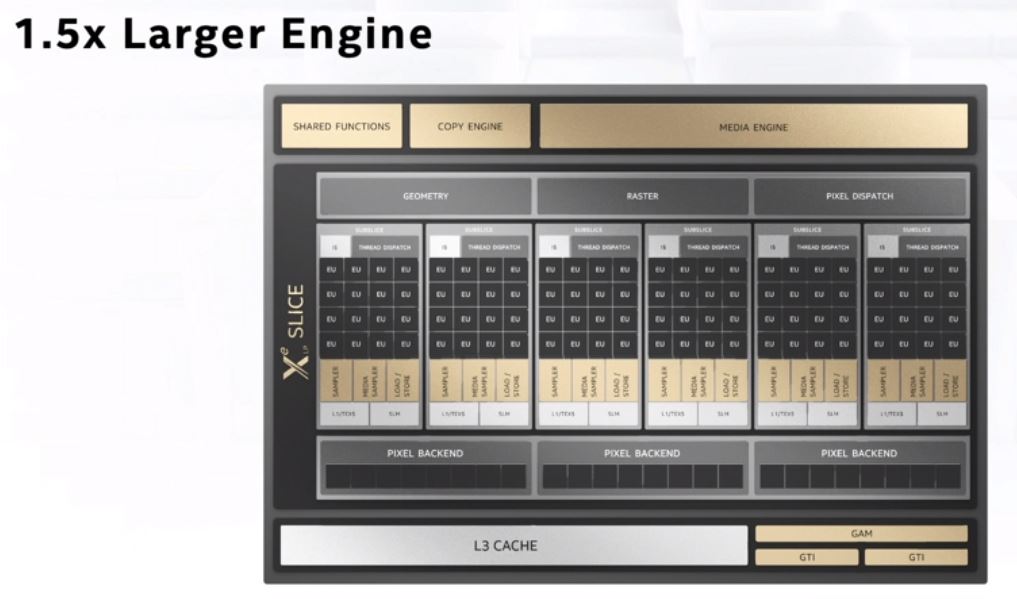

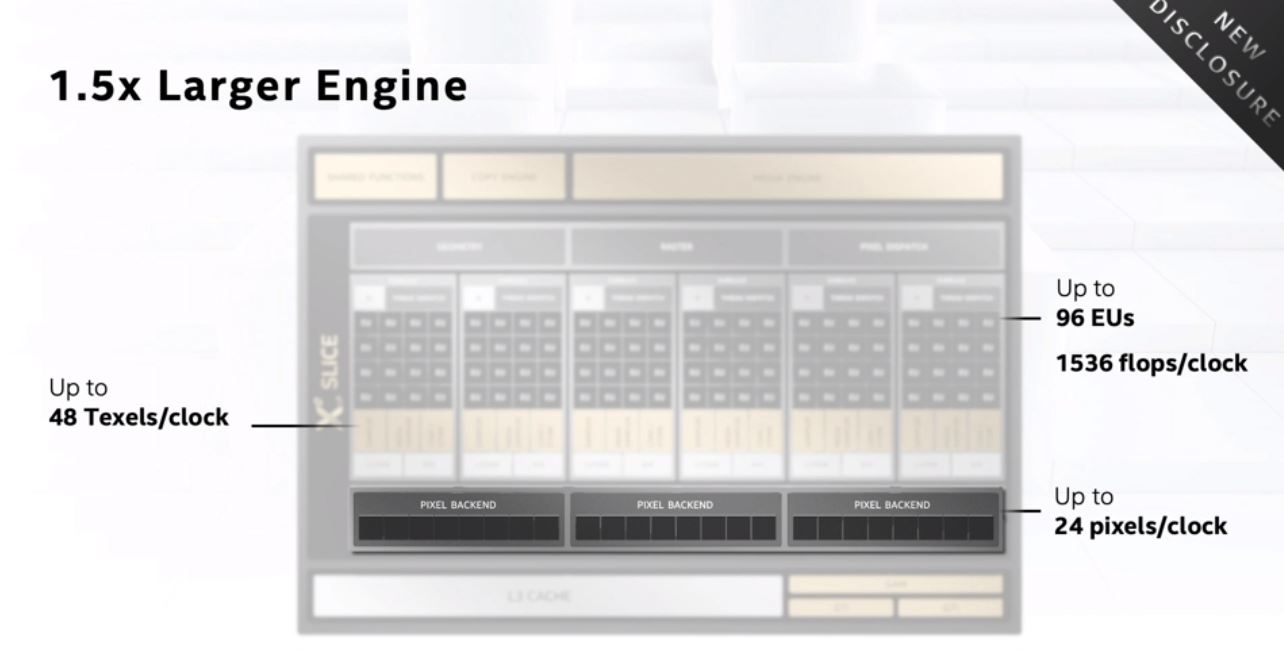

The size of the Intel Xe GPU will depend on the product, but it will have more compute resources than previous generations.

There are also changes to the execution units and compute sizes within the EUs for the new Xeon Xe LP generation compared with Gen11 GPUs.

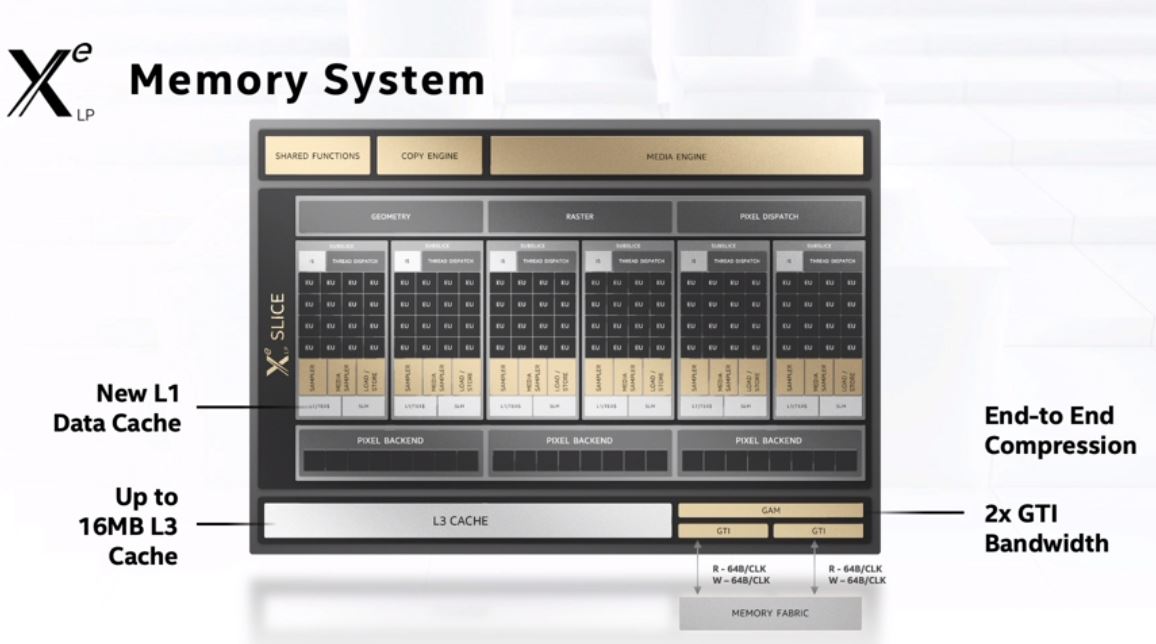

Intel is also increasing size and performance of its memory and structures.

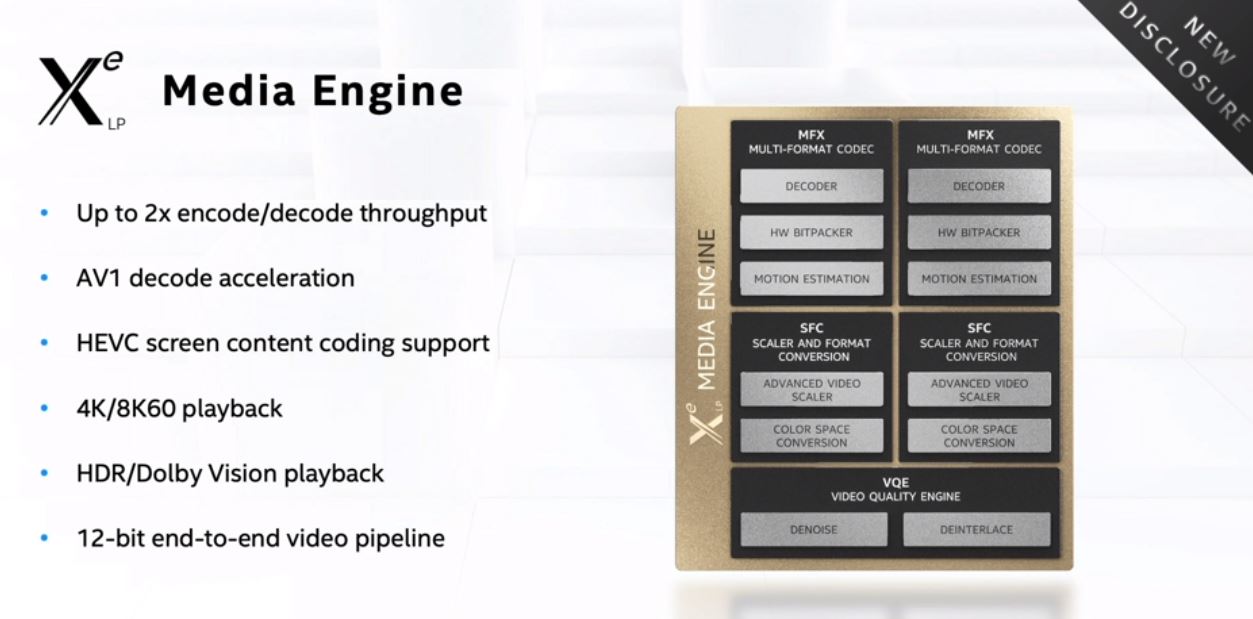

From the impression we got at architecture day, one of the big features is going to be the media engine in the Xe LP. Effectively these are the CODEC sets that are used for working with video using hardware acceleration. More on that soon.

Intel let us know that this slide will be updated, but Intel is also adding INT8 support to aid in inferencing performance.

What became fairly clear in this presentation is that the entire Intel Xe LP line is not designed to compete with the NVIDIA GeForce RTX 3080 Ti. Instead, it is designed to compete with integrated graphics and potentially some lower-end Quadros and perhaps T4s. Intel showed off many Xe LP gaming demos, but we are going to focus more on the server applications.

Intel Xe HP and Xe SG1

On the data center side, we were told about a few products. For the Intel Xe LP offering, we were told that there would be a SG1 low-end server GPU that we will discuss more. The Intel Xe DG1 we are going to cover closer to a formal launch. Still, we were told that the SG1 will be the first Intel Xe server GPU and will be LP-based.

Moving up the stack, the Intel Xe HP is very interesting. Intel disclosed that it has plans to scale from a single GPU tile up to four tiles. Intel plans to assemble the Xe HP GPUs using EMIB. Instead of having a monolithic die, this allows Intel to scale its package and potentially get better yields. This should be a bit later in the cycle as it is listed as using 10nm Enhanced SuperFin which we expect comes after 10nm SuperFin.

Raja showed off a Xe HP GPU. We double-checked what he said and this is a single tile version of the product that he said he was showing.

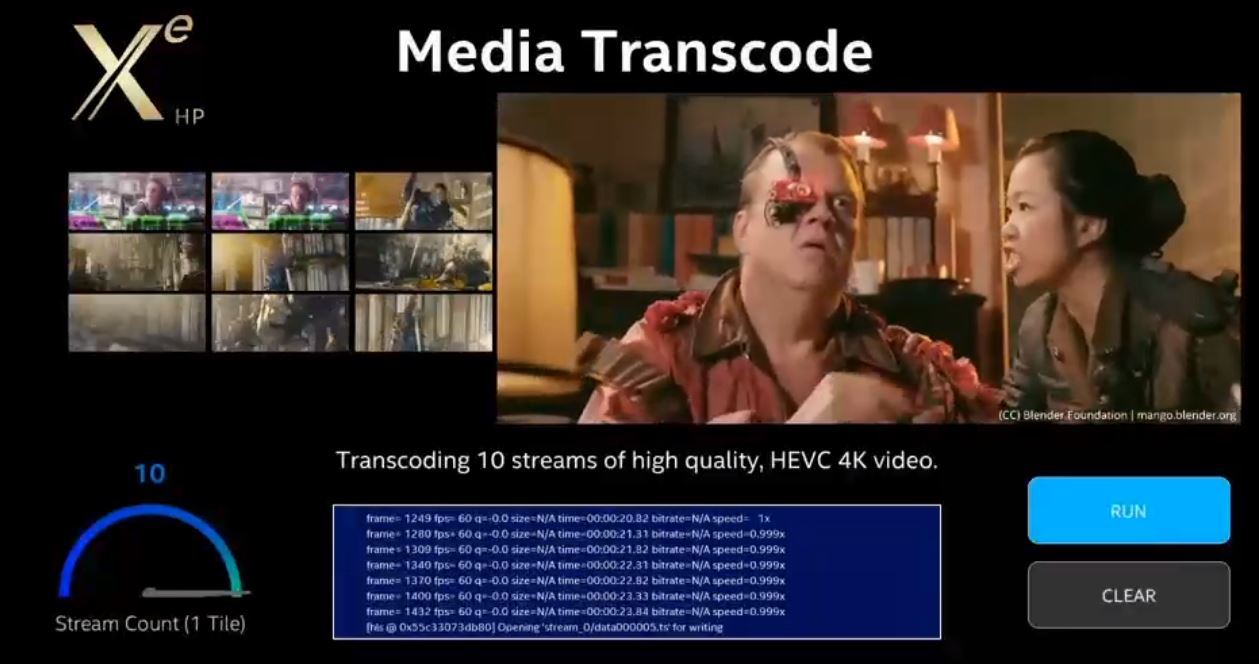

While one may have expected Intel to focus its Xe HP GPU discussion on AI or analytics, instead, it was showing off media streaming use cases.

Intel said media streaming would be a target market for this product. We know that in this space Broadcom is making a custom video transcoding chip for Google which we discussed a bit in our Xilinx Live Video Transcoding Product Line Launch piece earlier this year. The sheer volume of media transcoding workloads driven by video streaming seems to be driving a lot of effort in this space. For the Xe HP GPU, it is transcoding 10x 4K HEVC streams on a single tile which is the smaller configuration. Above we showed the Tiger Lake/ Xeon LP media engine so this seems to be a theme.

Intel Xe HPG

Gaming GPUs? Intel is doing that too. Intel says that its Xe HPG line will be designed for gamers.

We did not get a ton of information on this. Intel did disclose that it will have dedicated hardware ray tracing. Since NVIDIA pioneered this, and we are seeing AMD and Intel follow, this seems to be a standard in the industry going forward.

Since Raja Koduri has been burned by trying to bring HBM to gaming GPU segments before, we think this will use GDDR6 memory. HBM is great, but there are so few vendors that when the vendors decide to charge more since they have a key enabling technology for $10000 NVIDIA GPUs, it prices gaming solutions out of the market.

Final Words

We are excited to see what can happen with the Xe GPU line starting later in 2020. Given the team involved, and the size of Intel, we expect this to be a huge launch. At STH, the Xe HPC is still some time off which would be the biggest competitor to future generations of systems such as the Inspur NF5488M5 8x NVIDIA V100 Server we reviewed. Still, in the shorter term, we are very excited to see what the SG1, DG1, and HP can do.

SuperDuperSharkFin++++++++++++++++++

I think Xe HPG is sure to use HBM, because Intel uses EMIB as a cheaper and slimmer alternative to an interposer, and on the slide where they were showing manufacturing and packaging technology, HPG did not have EMIB listed. It’s probably manufactured at TSMC, but that wouldn’t stop them from using EMIB, just like they did on Kaby Lake G.

*Is sure to not use HBM, sorry