As part of Intel FPGA Day, which is running at the same time as Supercomputing 20, we have two new Intel launches. First, the Intel Open FPGA Stack, or OFS, is aimed at lowering the barriers to entry to utilize FPGAs. The second big announcement is the Intel eASIC N5X structured ASIC offering. We are going to briefly discuss both.

Intel Open FPGA Stack or OFS

Traditionally, FPGAs require a bit more work than a typical CPU or GPU to start utilizing for an application. For example, one has to build the memory and PCIe/ connectivity traces as well as the logic structure. At XDF19 Xilinx discussed its shell to help accelerate time-to-deployment by creating a standard basic starting point for FPGA development that included getting memory interfaces and networking connected. Intel is seeing the same need and addressing it with OFS.

With the new Intel Open FPGA Stack or OFS Intel is proving new modular components to help get some of the base functionality setup, as well as some common features. Developers can choose to use these components or build their own. For many who only have resources to focus on domain-specific acceleration, this lowers the barriers to entry for FPGAs.

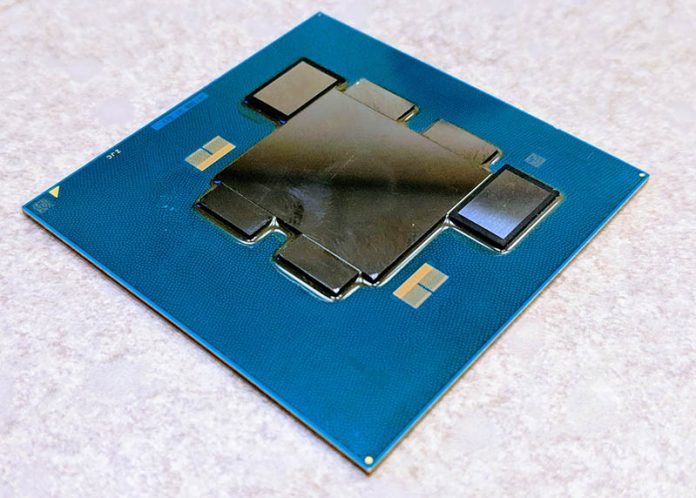

On the other end of the spectrum, as FGPA enabled workloads become more established, the Intel eASIC N5X is the next step in a IP progression.

Intel eASIC N5X

Intel recognized that while FPGAs are great for development and constantly changing workloads, at some point ASICs that trade flexibility for lower cost and power consumption make sense. To address that reality, Intel purchased eASIC to help with that transition of IP from FPGAs to ASICs. As fruit of that acquisition, we have the Intel eASIC N5X.

Intel says that its new eASIC N5X devices deliver up to 50% lower core power and lower cost compared to its FPGAs. At the same time, they provide faster time to market and lower non-recurring engineering costs compared to ASICs. In some ways, these are a compromise between FPGAs and full ASIC design efforts. Intel also notes that the eASIC N5X devices incorporating “a secure device manager adapted from the Intel Agilex FPGA family, including secure boot, authentication, and anti-tamper features.” (Source: Intel)

Final Words

In a world where we expect heterogeneous silicon, having the ability to prototype rapidly on FPGAs then transition to eASICs then ASICs can make a lot of sense. There is a lot of work on co-packaging new IP blocks so this path makes a lot of sense. The Intel OFS announcement helps more developers move down the paths of both delivering their own FPGA solutions as well as to develop IP blocks that can be put into the structured ASICs that eASIC provides and then integrated into other packages.