Marvell is launching two new infrastructure processors aimed squarely at the 5G infrastructure build-out. These are Arm-based processors that rely on heavy network acceleration blocks to process and move packets quickly. Recently, we saw the Intel Atom P5900 launch which is largely focusing on a similar market. Silicon providers realize that bandwidth needs are going to grow on an accelerating curve as 5G rolls out, and the infrastructure behind it will not rely solely on traditional general-purpose IP blocks to do all of the processing. In this context, Marvell is launching chips specifically designed for these emerging workloads, the Marvell Octeon TX2 and Fusion CNF95xx processors. We are going to look at some of the details of those chips in this article.

Background: Where Infrastructure Processors Are Used

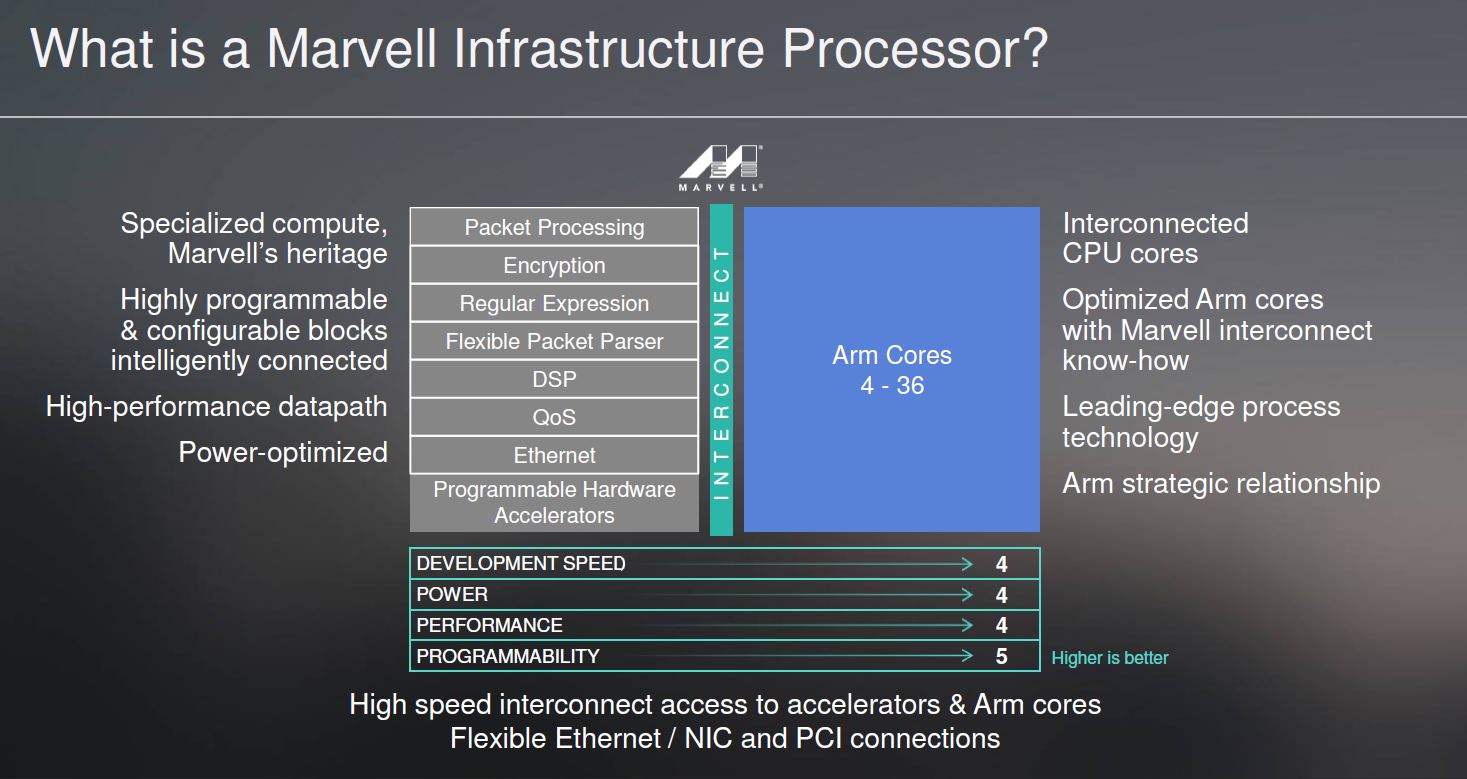

Most are familiar with general-purpose processors such as the one you are currently using to read this article whether on a phone, tablet, or PC, and those are similar in many ways to the CPUs used in data center servers. Infrastructure processors are instead designed to handle the flows of data between devices. Think of these as the processors used to get this article from STH’s servers to your device. Marvell essentially utilizes lower-power general-purpose Arm cores and combines them via a high-speed interconnect to hardened programmable IP blocks such as those for packet processing, encryption, DSPs, and other hardware accelerators. This gives an element of easy-to-program general-purpose compute along with dedicated acceleration blocks.

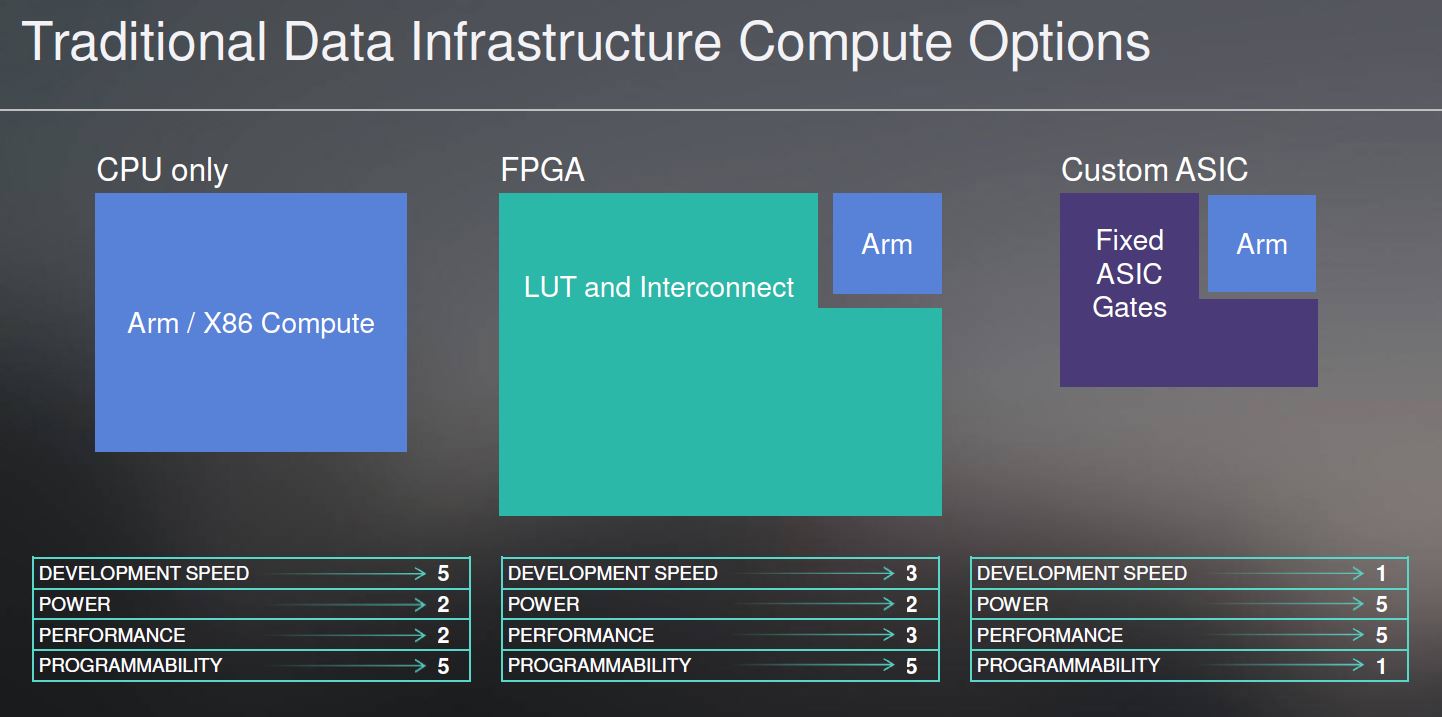

In our phone briefing, that bottom chart scale with 4’s and 5’s seemed like it lacked context. We found that context in Marvell’s backup. It is comparing its solution to traditional easy-to-use CPUs that sacrifice performance, FPGA’s that are flexible but are more difficult to program, and custom ASICs that are slower to design and lack the same level of flexibility but excel at their given tasks.

Marvell is noting that the FPGAs and ASICs often include lower-power Arm control cores much as we saw with the Xilinx RFSoC FPGA for 5G Networks. The company is noting that it has the ability to scale to higher-core counts for more performance.

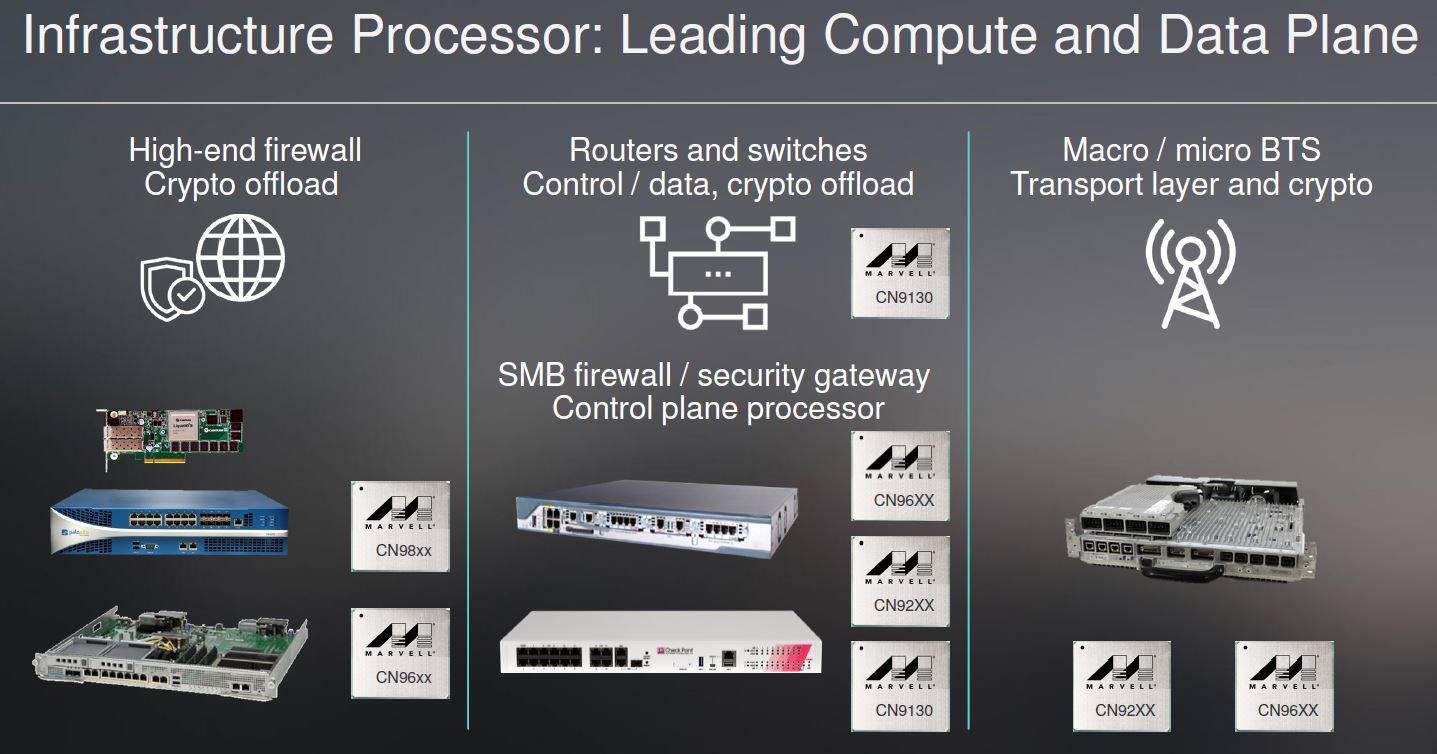

These infrastructure processors are found in devices such as firewalls and gateways as well as base stations for cellular networks.

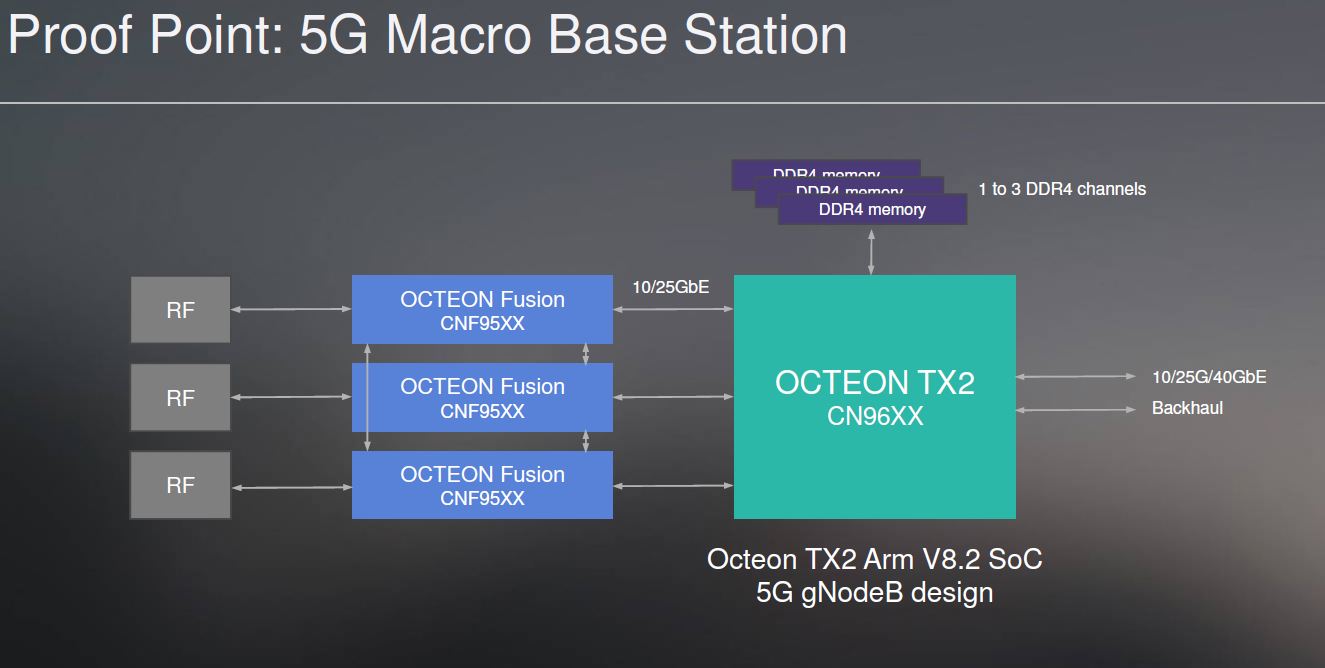

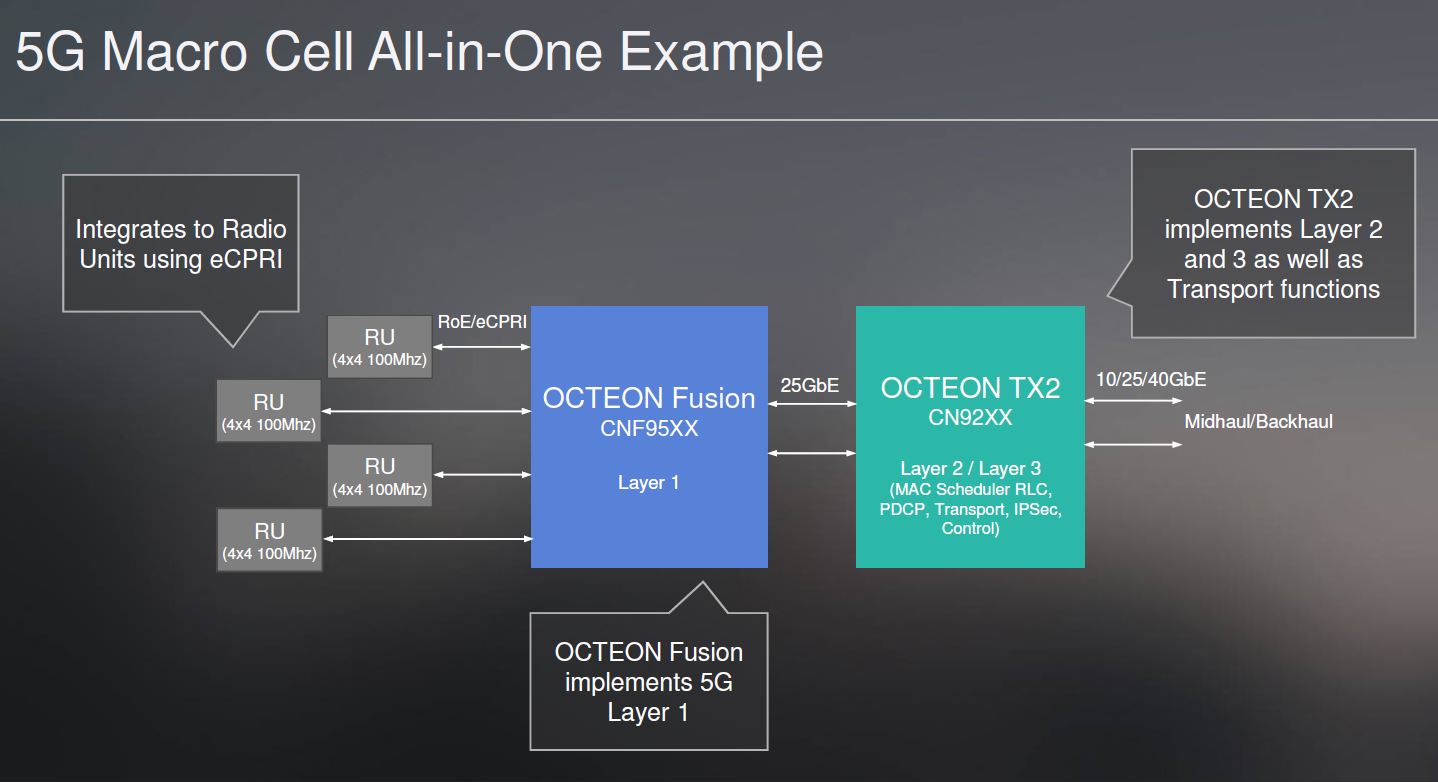

Marvell is showing a few solutions that use both the new Octeon TX2 as well as the Octeon fusion. An example here is of a 5G macro base station with an Octeon TX2 handling the heavier processing while the Octeon Fusion chips are being used for PHYs and lower-level networking.

For smaller 5G deployments, the Octeon Fusion is integrating to the cellular radios providing Layer 1 functionality and the Octeon TX2 is implementing Layer 2-3 along with backhaul networking.

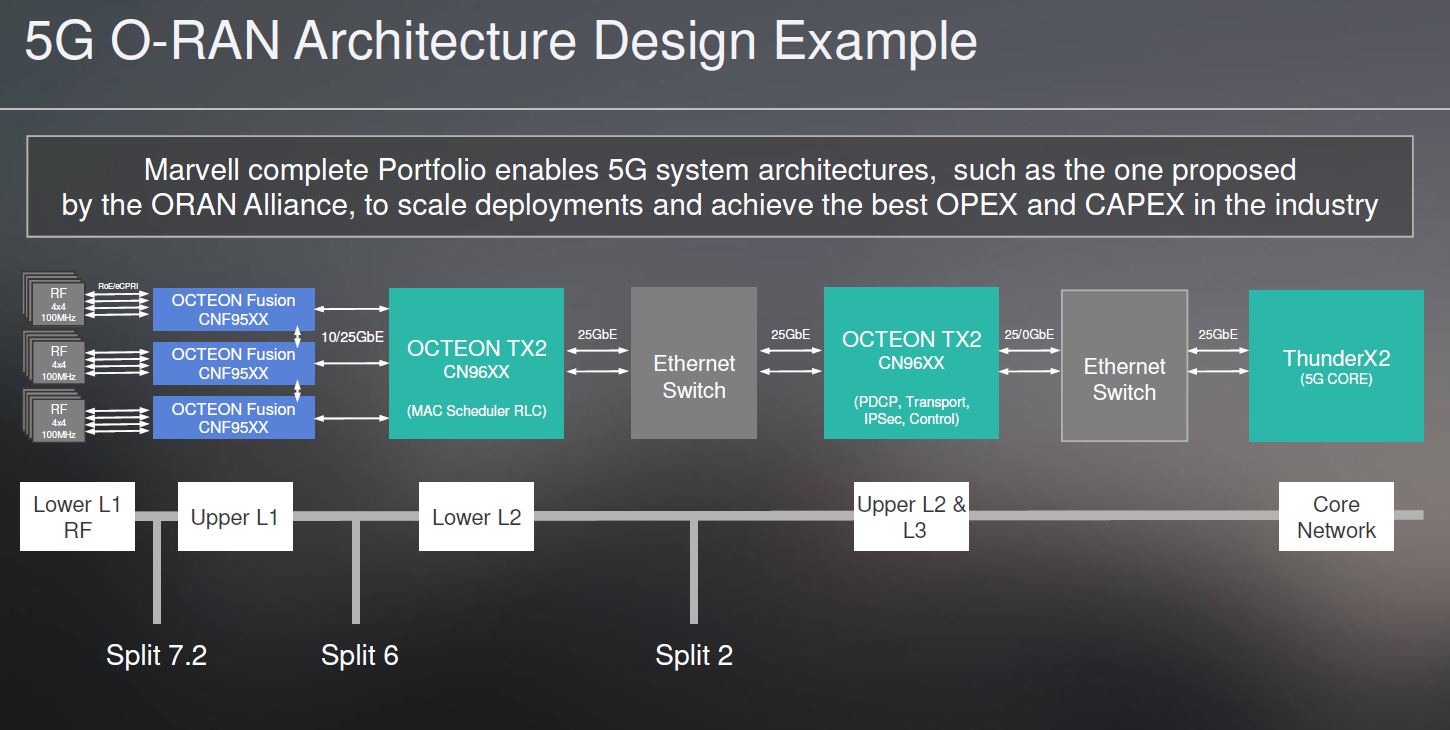

Marvell also showed a 5G O-RAN architecture with its new chips being used along the chain.

We were slightly disappointed that there were blocks labeled “Ethernet Switch.” Marvell is not necessarily the leader in merchant silicon for switches. Still, It would have been a great opportunity to plug a Marvell Prestera 98CX8580 or similar chip and show an all-Marvell solution.

Marvell OCTEON TX2 Infrastructure Processors

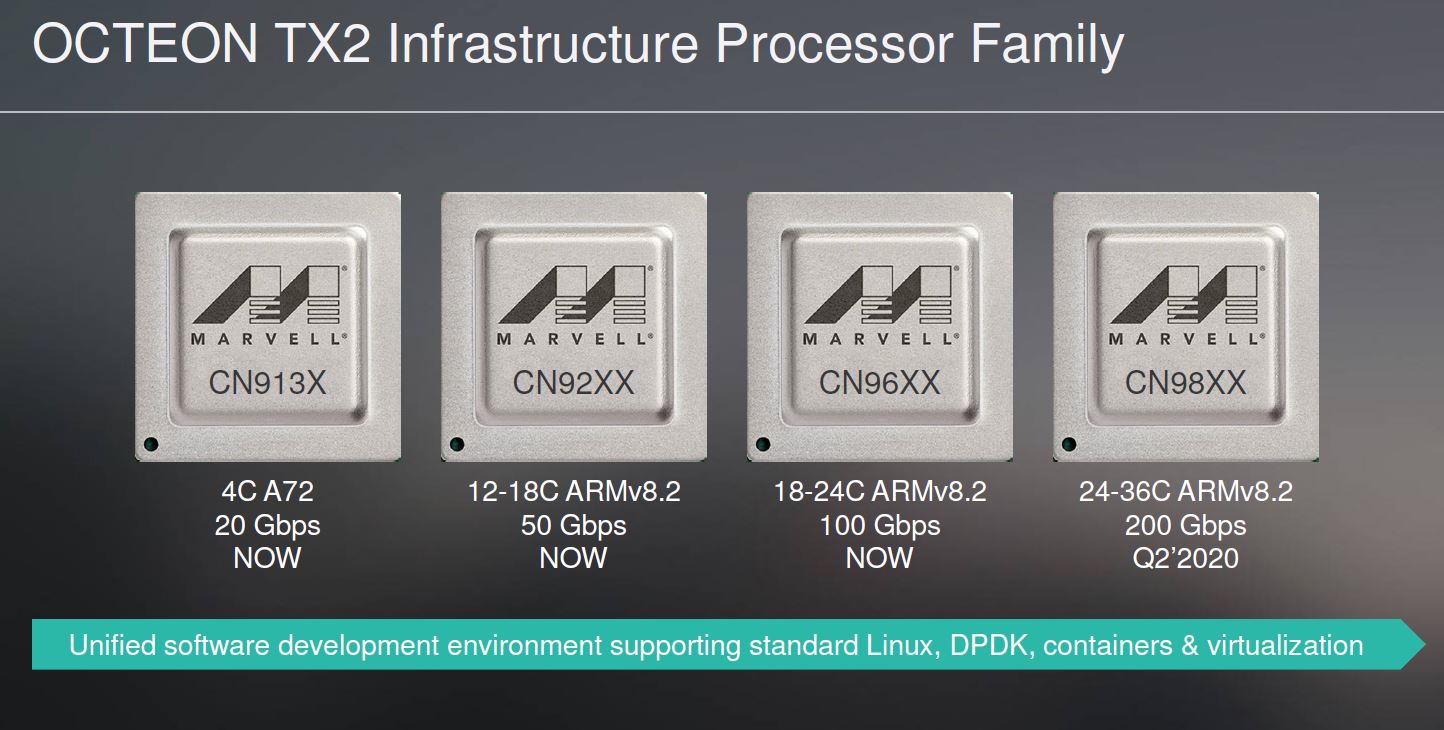

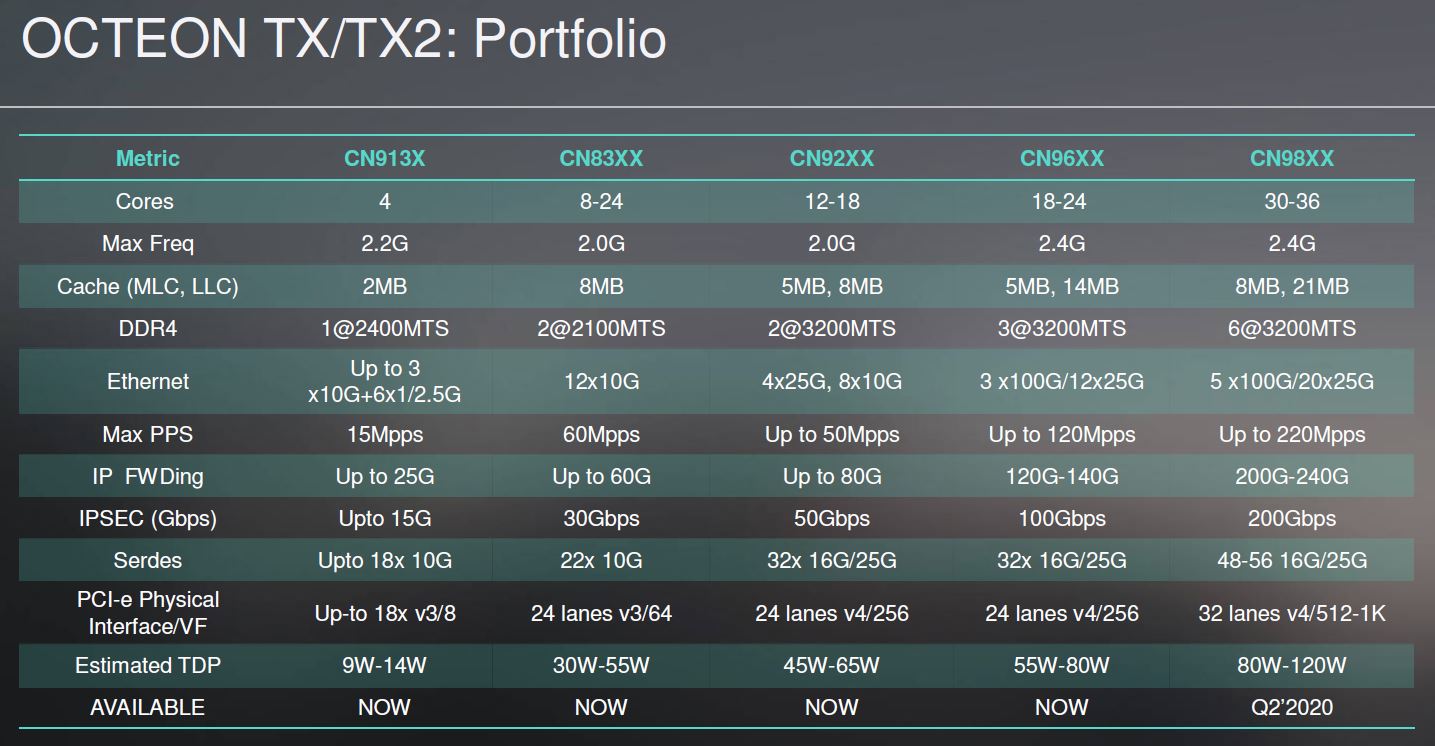

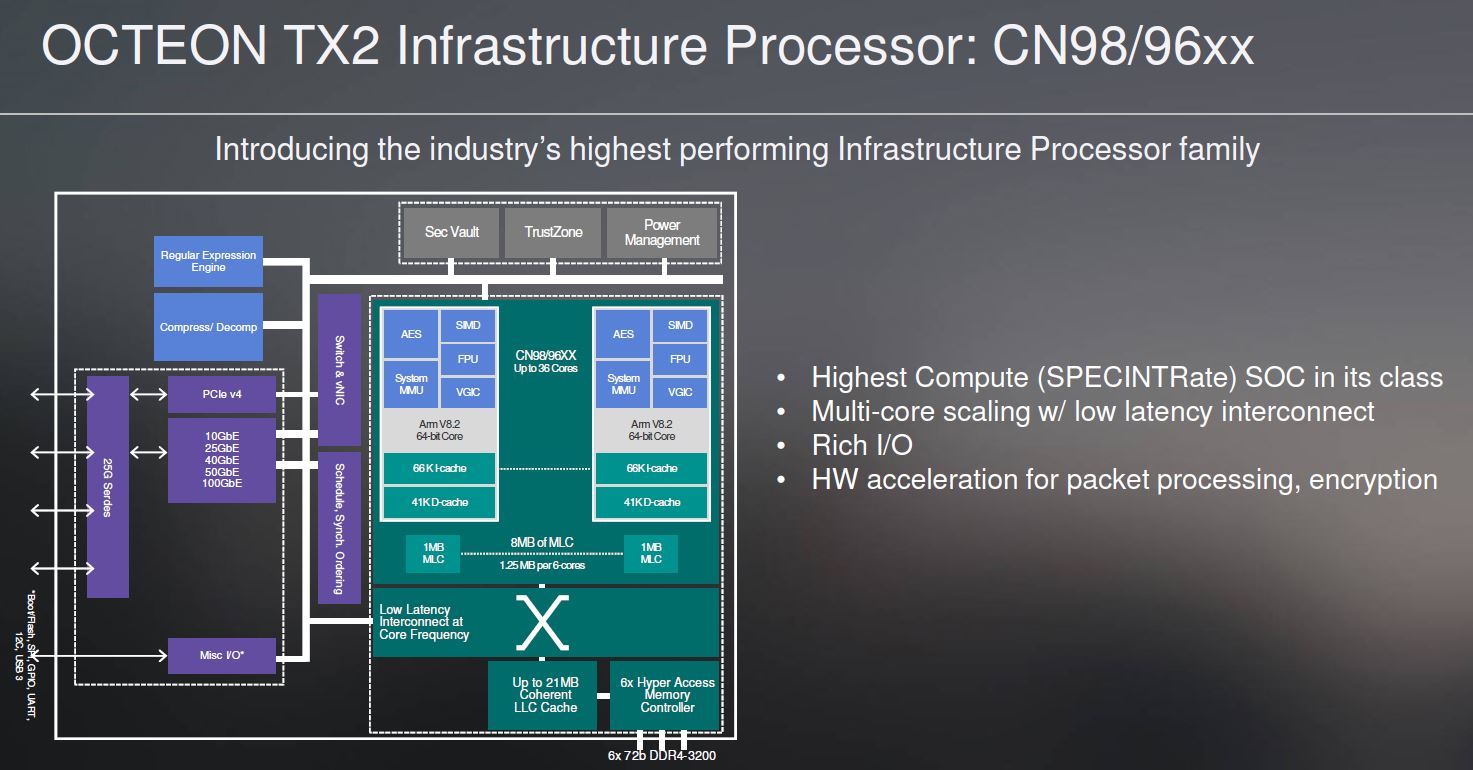

With 4-36 Arm v8-based cores, hardware acceleration blocks, up to 200Gbps data path bandwidth, and up to 5x 100Gbps MAC integrated, the Marvell Octeon TX2 is designed to enable high-performance and low-power infrastructure. This is not a single product. Instead the Octeon TX2 is a series of four lines of processors scaling in capabilities.

The power envelopes range from 9W up to 120W and there are a massive number of other differences between the different families. The existing Octeon TX CN83xx chip is in this chart as well.

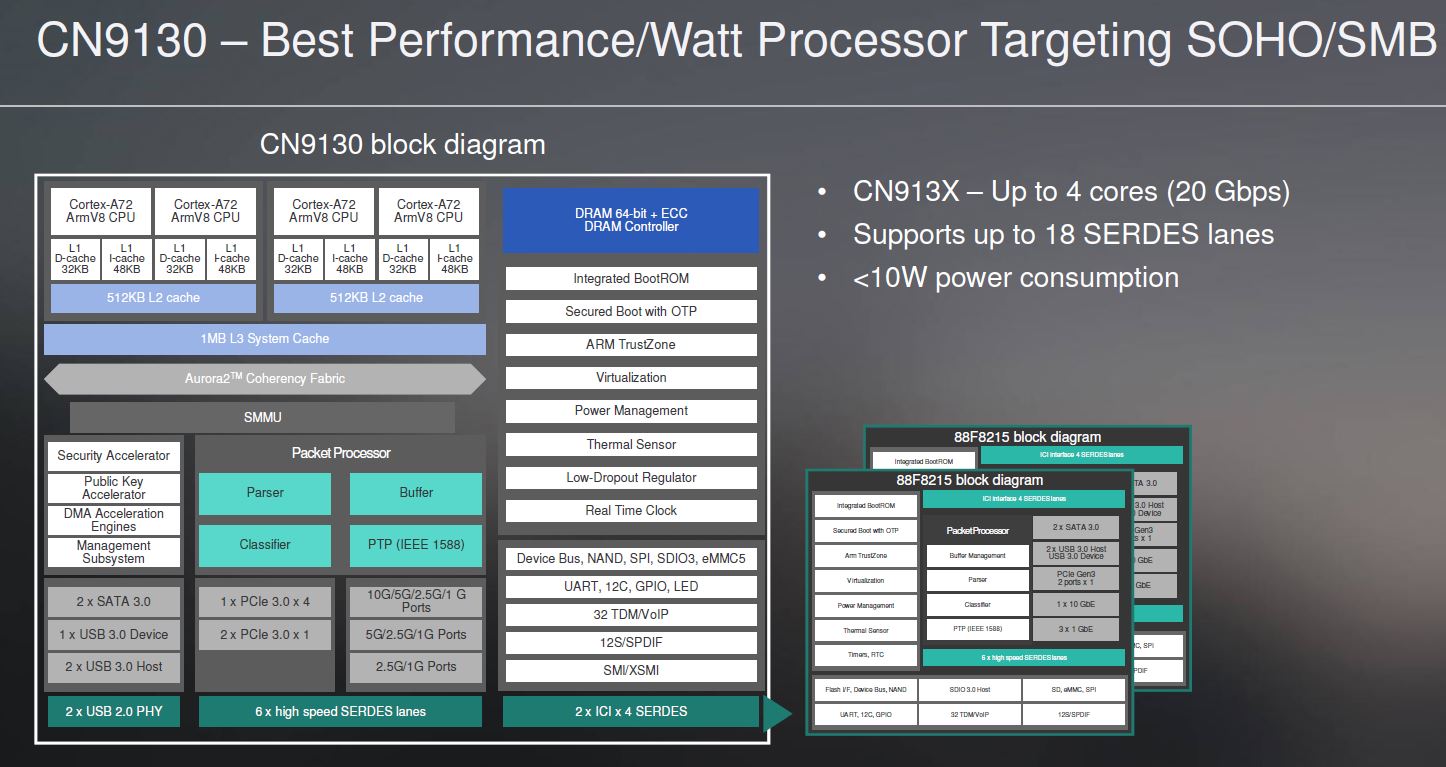

Starting on the left of that chart, the lower-end part is the Marvell Octeon TX2 CN9130. This chip has quad-core Arm Cortex-A72 cores with a shared L3 cache. Using an Arm core means that Marvell can use some of Arm’s platform features such as the ARM TrustZone. Marvell adds its network acceleration blocks along with platform I/O to create a sub-10W chip capable of powering the SMB, SOHO, and ROBO market network appliances.

At the higher-end, with the Octeon TX2 CN93xx and CN96xx series of processors, one gets higher-performing Arm V8.2 64-bit general-purpose cores. The idea behind this chip is to put enough compute onboard that one can potentially not add an x86 server alongside the system and consolidate to a single box. Also, in networking appliances, there is a model where many Arm cores are used to perform a lot of network processing logic. Marvell is adding its custom network acceleration blocks for packet processing and crypto so this work does not need to be done on the CPU cores.

One will also notice that this architecture can scale up to 6x DDR4-3200 memory channels which offer more theoretical bandwidth than current 2nd Gen Intel Xeon Scalable processors and even the 2nd Gen Intel Xeon Scalable Refresh CPUs. There is also higher-speed integrated Ethernet (up to 5x100GbE) versus the Intel Xeon SP Lewisburg PCH that is a separate chip that goes up to 4x 10GbE. Marvell even has PCIe Gen4 implemented in the higher-end Octeon TX2 versus PCIe Gen3 in Intel’s solutions and the TX2 CN9130. The CPU performance here will not outpace Intel’s high-end Xeon Scalable, but the idea is that these CPUs are much better at networking-related tasks than a general-purpose CPU.

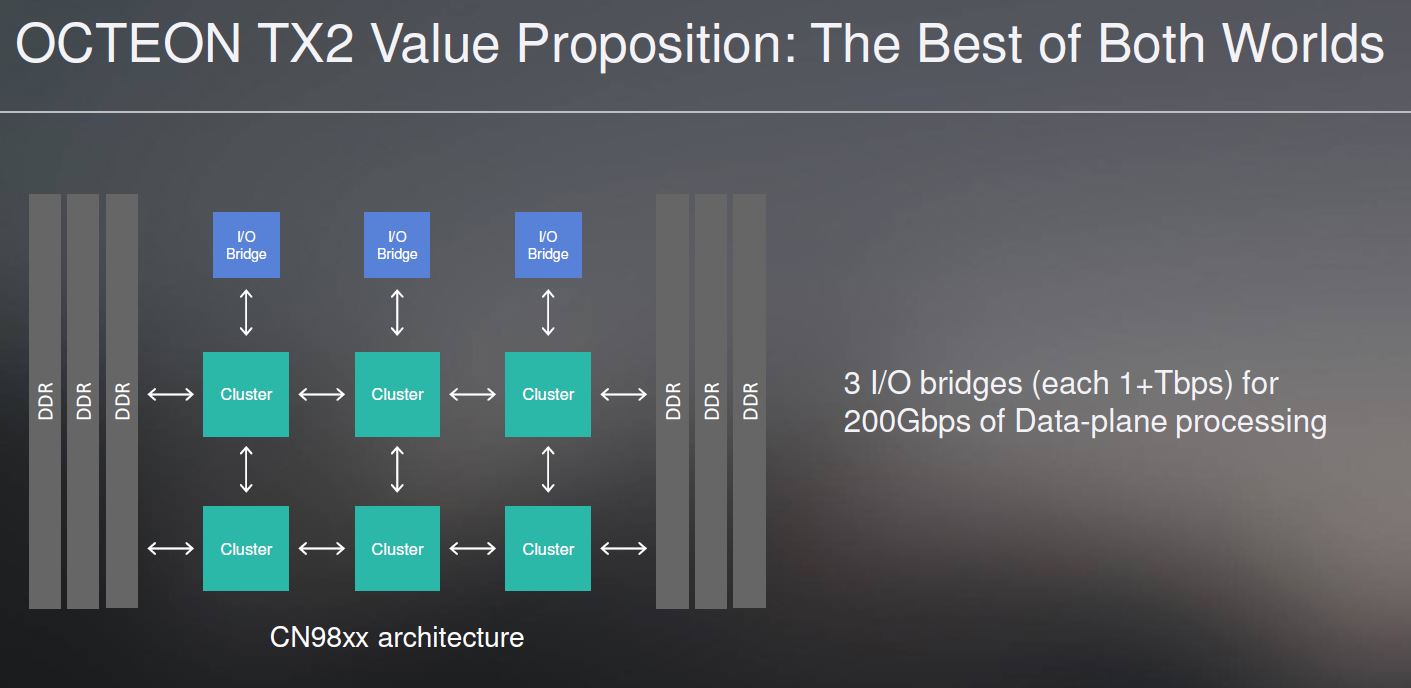

Here is another slide we did not discuss but we found in the backup which is that the CN98xx has clusters of cores with three I/O bridges running at over 1Tbps.

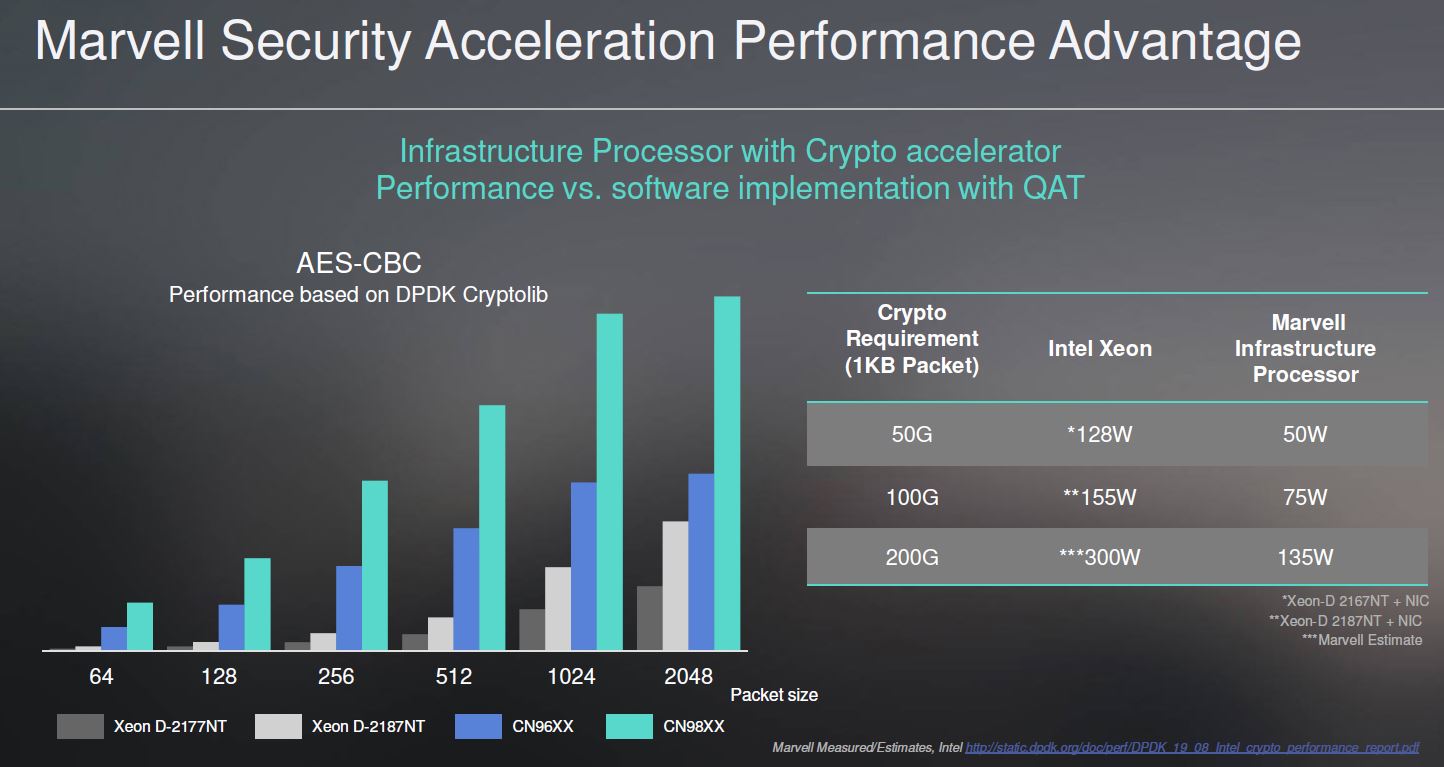

Marvell claims massive performance increases versus QAT. At STH, we did some benchmarking in the earlier days of QAT in: Intel QuickAssist Technology and OpenSSL Benchmarks and Setup Tips and Intel QuickAssist at 40GbE Speeds: IPsec VPN Testing. Marvell claims its acceleration is faster and uses less power.

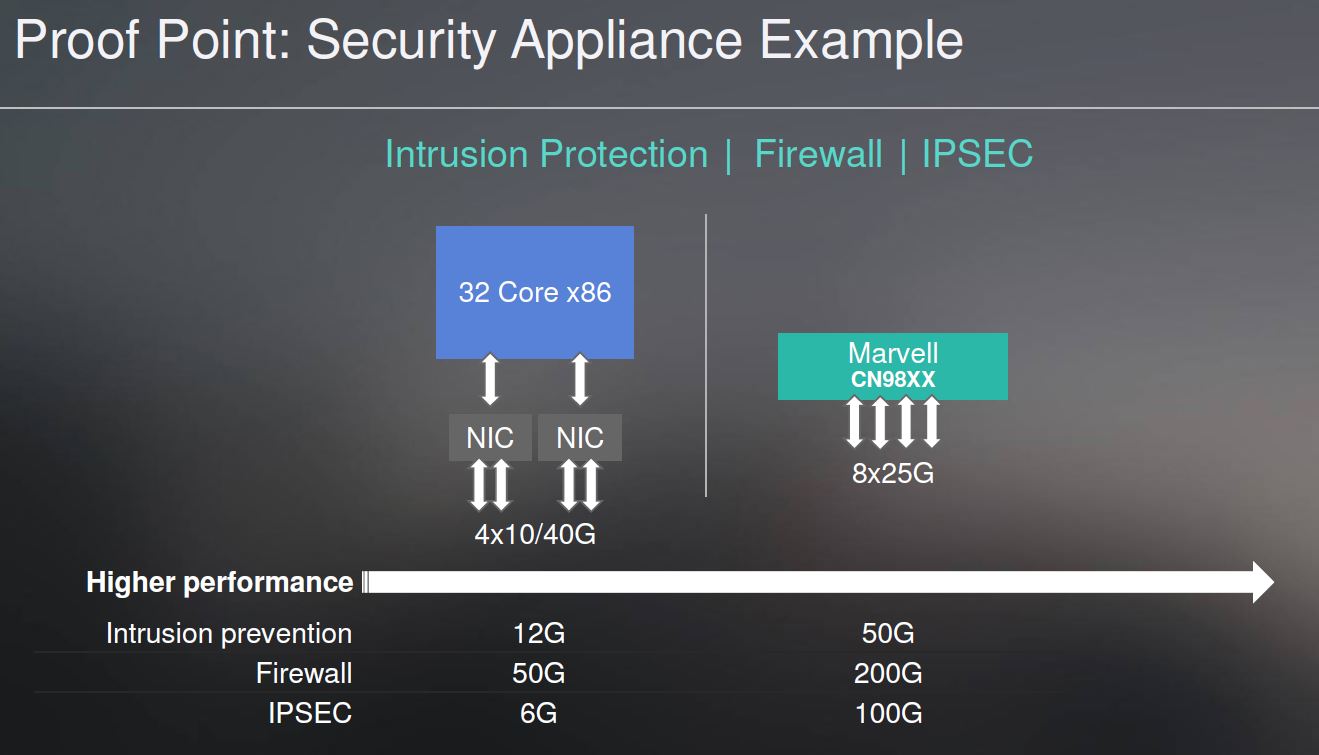

Likewise, for IPsec and firewall appliances Marvell claims higher performance due to its hardware accelerators.

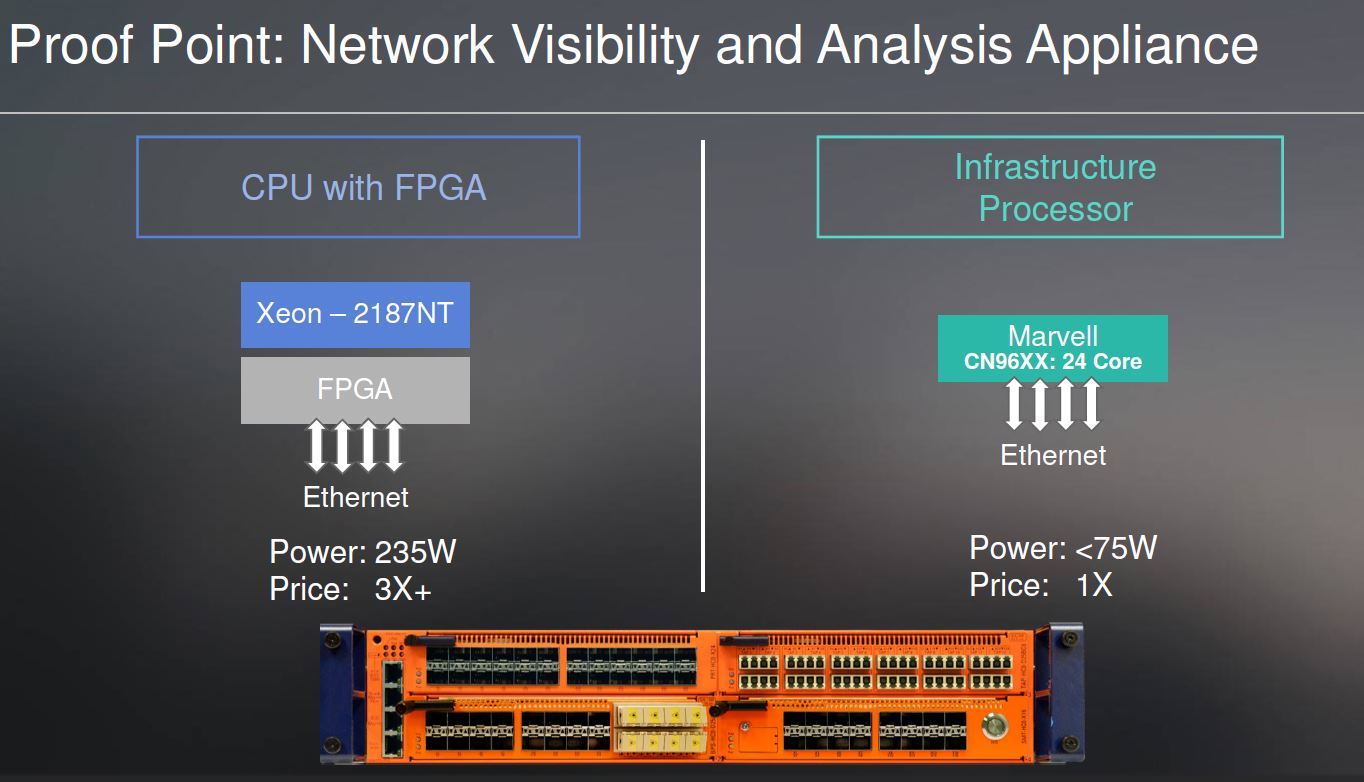

Marvell did not provide pricing, but it claims that it can match or exceed a CPU plus FPGA solution on both price/ performance and performance per watt.

Many of our readers are going to know exactly what these appliances being shown are. Since we are not sure if we are allowed to disclose them, we are going to pass on that but remind our readers there is a comment section below.

Marvell OCTEON Fusion CNF95xx Processors

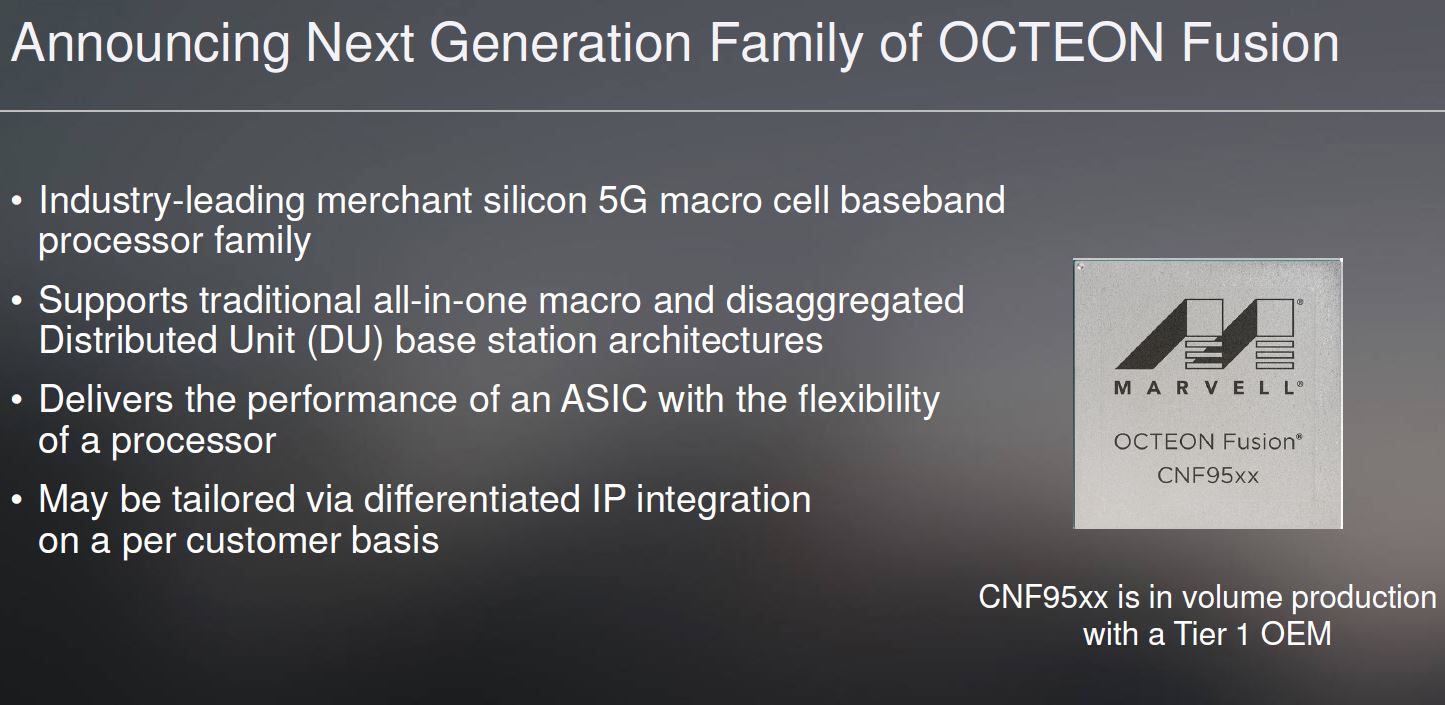

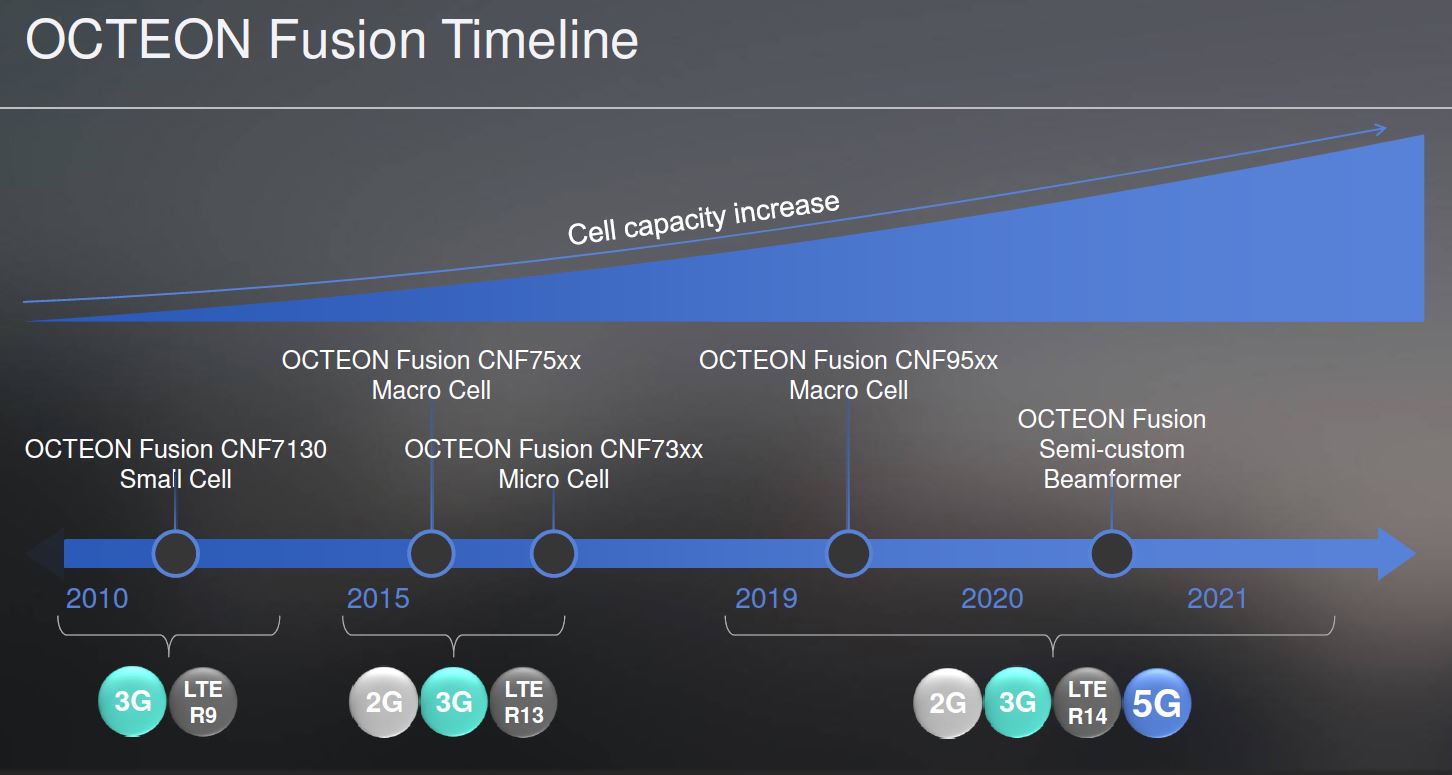

Marvell also has a 5G macrocell baseband processor solution that is called the Marvell Octeon Fusion CNF95xx family.

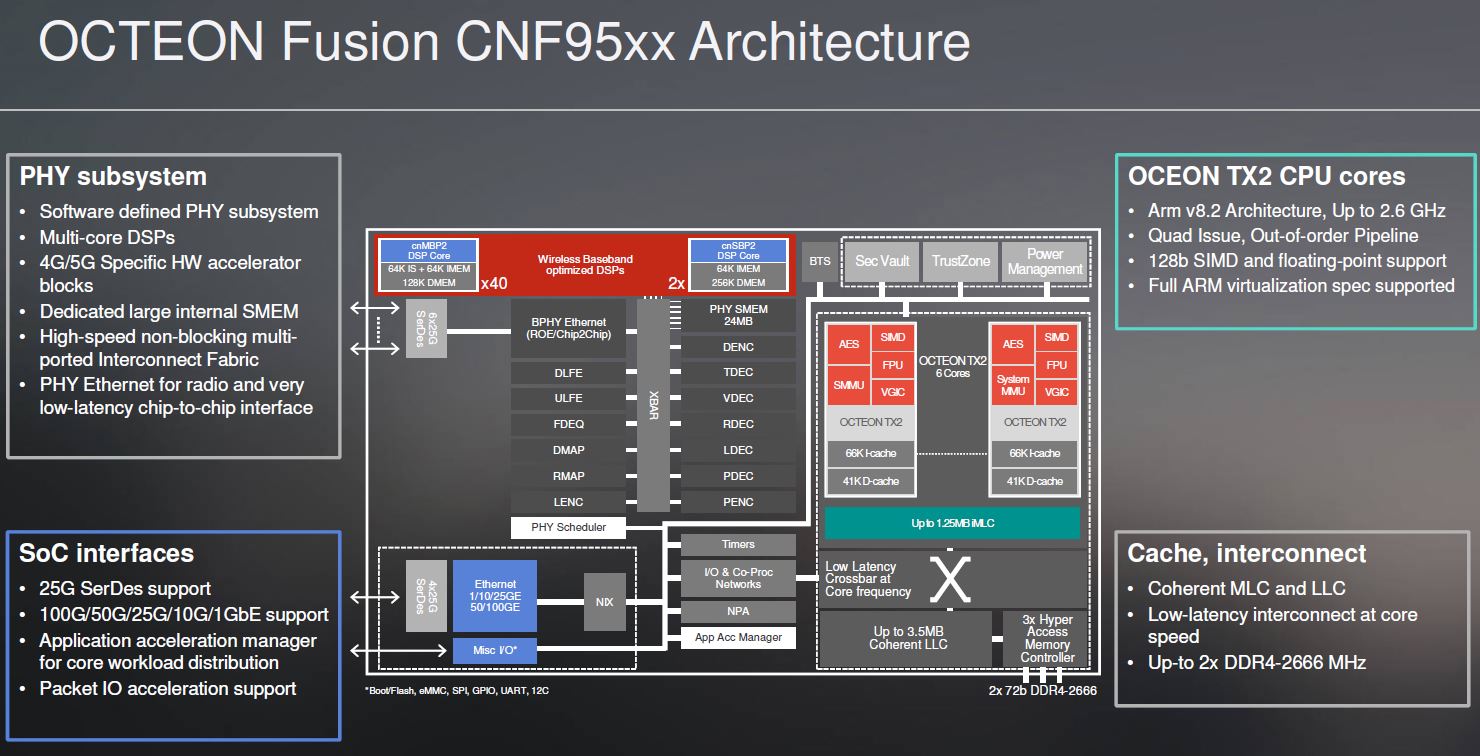

These processors offer a lower number of Marvell Octeon TX2 Arm V8.2 cores (6). We will note in this diagram that we think the box on the right labeled “OCEON TX2 CPU cores” should be “OCTEON TX2 CPU cores.” In the diagram, they are labeled as OCTEON TX2 so we are going with that.

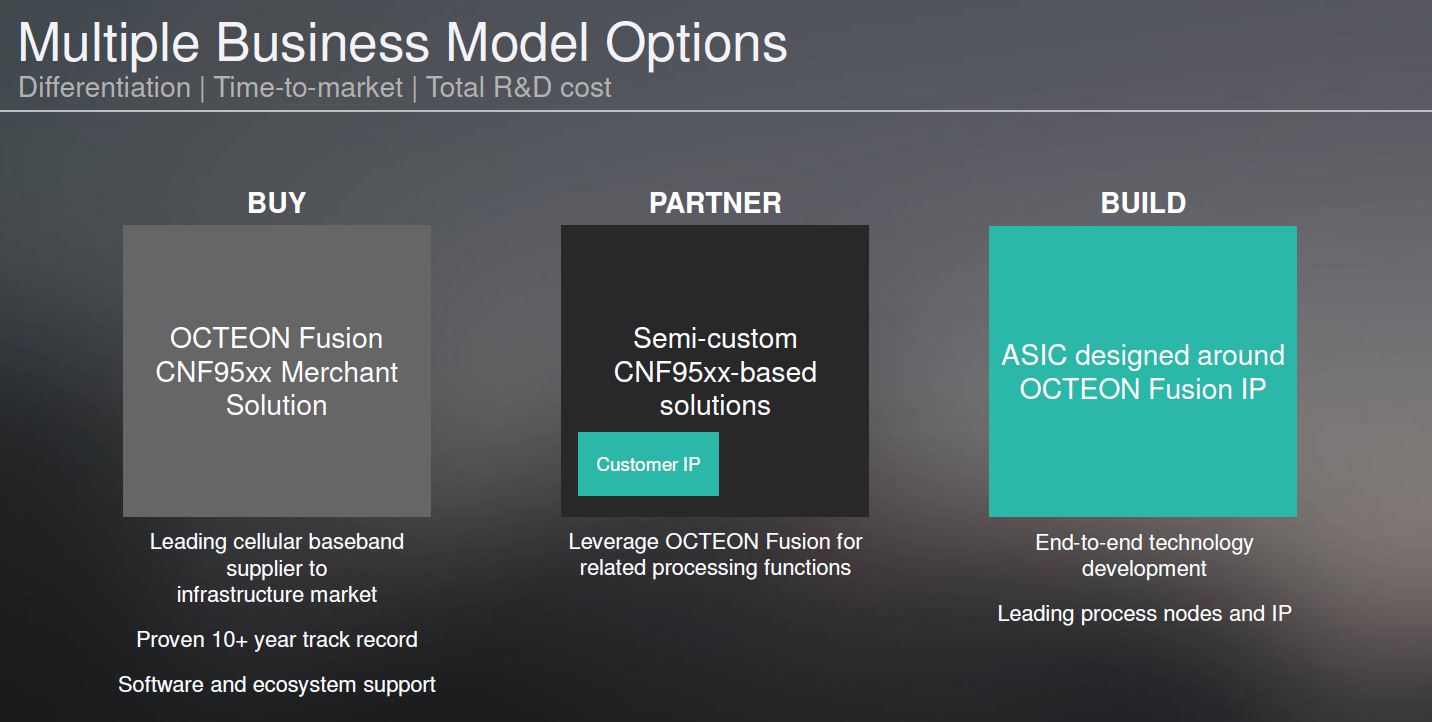

These are meant to be lower-processing power chips but they also have an important feature that is necessary for this market a PHY subsystem. These include DSPs and accelerator blocks to ensure high-speed and low-latency transmission from the CNF95xx to upstream and downstream devices. Marvell also has wireless optimized DSPs and allows customers to add in their own IP blocks in a semi-custom model or even do more customization as necessary.

This space is generally dominated by a few large 5G infrastructure players. Those customers often have specialized algorithms and IP that they may want to see integrated. Marvell says one is a customer and it has some of the flexibility to add others using these models.

Final Words

Overall, this is an important announcement. Just about every silicon provider is spinning something to go after parts of the 5G infrastructure built-out since it is an enormous opportunity. Many of the players, such as Marvell, who have been in the market themselves or through acquisitions, are undertaking massive efforts to upgrade their products with hardened features to address the data growth that is expected over the next 3-5 years. Now more than ever we are seeing companies focus on network functions because network speeds are reaching levels that they cannot practically be done efficiently on general-purpose CPUs. That is why we are seeing solutions such as these and even markets such as the SmartNIC market exploding.

Excellent article on infrastructure processors. Very well defined. I need your permission to reproduce this article at my website TechnologyTimes.pk.

May I allowed?

Patrick, an important information was missing: will these new Octeon processors have open source drivers and firmwares? Will they be fully supported by upstream Linux kernel?

If you watch what happened with Ubiquiti and their line of Octeon switches, you will understand the importance of it. Ubnt faced huge issues upgrading from kernel 3 and still had to move to a kernel 4 version that is already quite outdated. Closed-source blobs, buggy hardware acceleration deiven by blobs no one can fix… not nice in a world of faster software cycles, increasing security threats, etc.

@ Marcelo B while that may have been a headache for Ubiquiti I don’t see how that matter much in regards to this article. The chips are being rolled out for 5G applications. Any large customer buying this which is obviously marvells goal would be creating their own software to run on their boxes at a very large scale. Likely working close with marvel. In there intended use case open source or closed source real does not matter as there are a few big buyers and sellers. A closed source solution would just mean marvell would likely charge a little extra after the initial purchase. A company would know this going in and factor it into the purchase price when deciding on a vendor.