In the global rush for new 5G networks, operators have to contend with a number of challenges. Perhaps the most fundamental is translating analog radio waves to digital signaling. With 5G networks operating new frequencies and faster speeds, and the processing and physical environments involved creating more noise, RF engineers have a challenge on their hands. The new Xilinx Zynq UltraScale+ RFSoC is an FPGA solution the company believes is going to be a winner in the 5G service provider space.

Xilinx Zynq UltraScale+ RFSoC FPGA Solution

As part of the Mobile World Congress 2019, the Xilinx Zynq UltraScale+ RFSoC Gen 2 and Gen 3 solutions are being unveiled. This is a product line where Xilinx has devices specifically to turn RF signaling into a digital output.

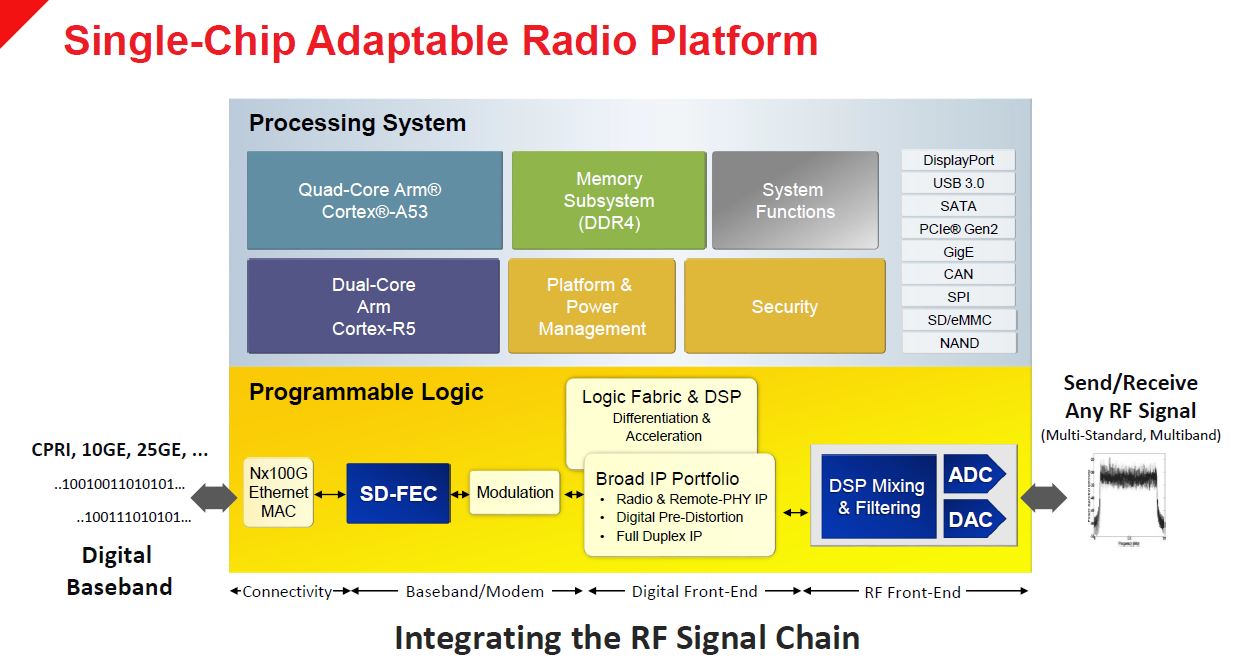

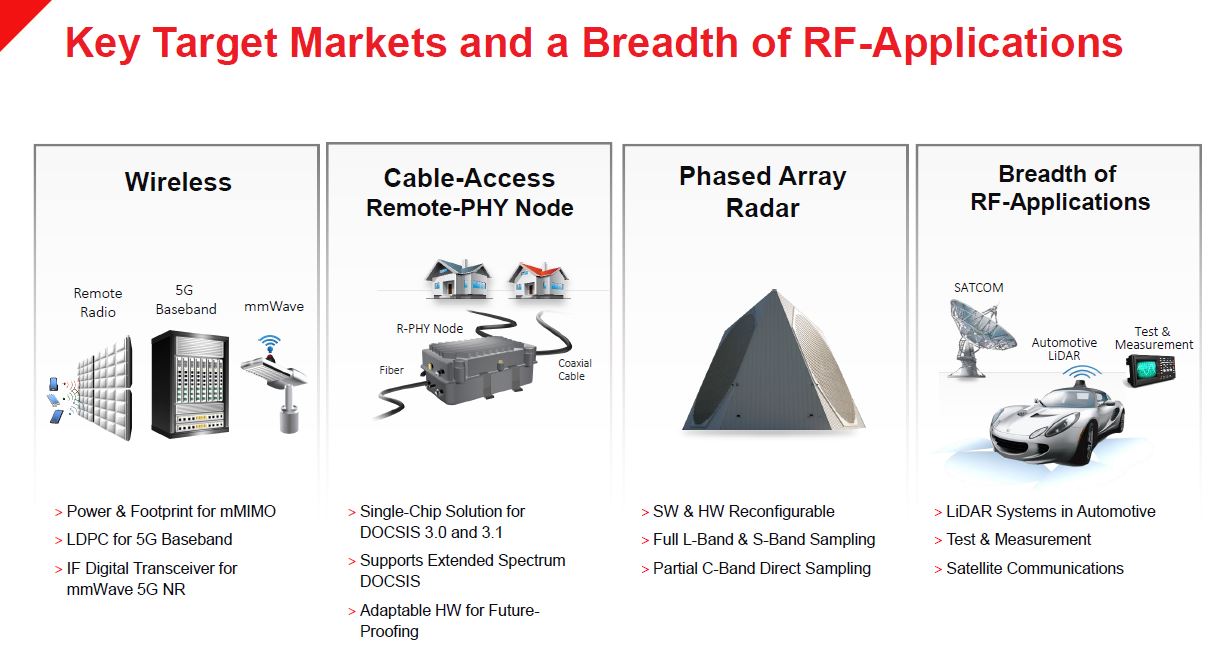

The main challenge that Xilinx is trying to solve is how to integrate a high-performance data converter to go from analog to digital. Integration on the FPGA, the company says, has been limited to lower-end converters. 5G is the first generation where RF needs to stay in step so there can be high-performance analog on a FPGA. Xilinx is looking at applications beyond 5G wireless, such as:

- Remote-PHY for cable operators (fiber to a PHY then cable to a small number of homes)

- Radar arrays

- Other higher-performance RF applications where integration is important

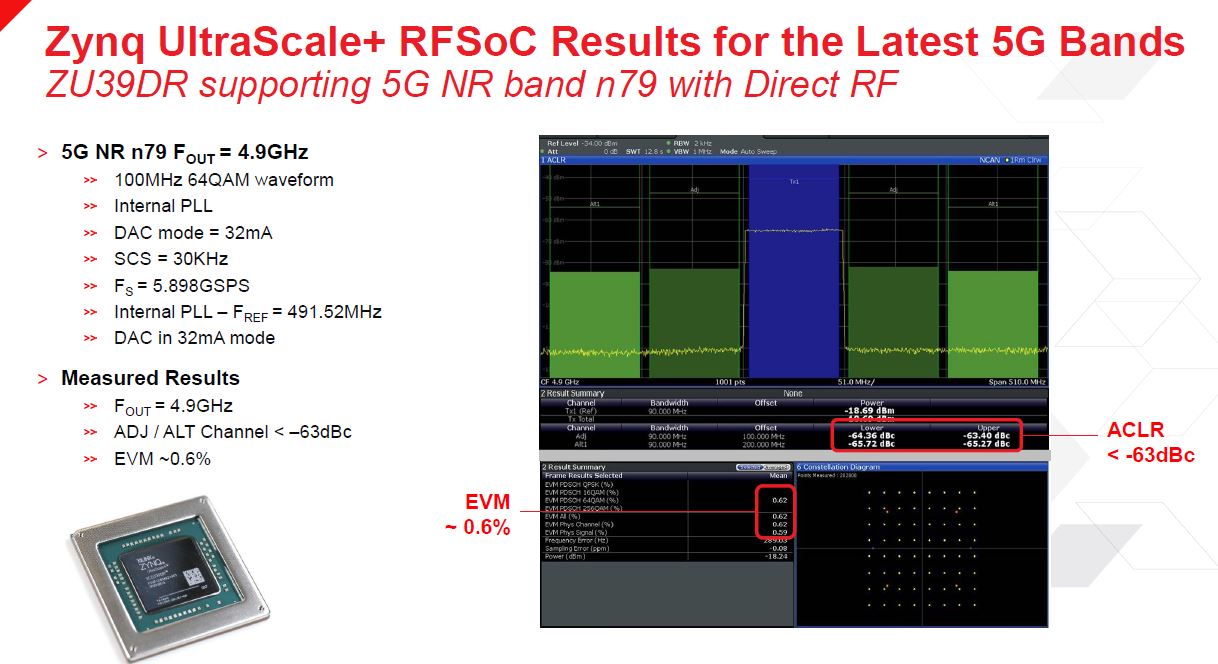

The new Xilinx Zynq UltraScale+ RFSoC products it says are performing very well against standards. For example, the screenshot below shows EVM at ~0.6% versus a target Xilinx had of 8%. Likewise, ACLR at <-63dBc compares with a target of 45dBc.

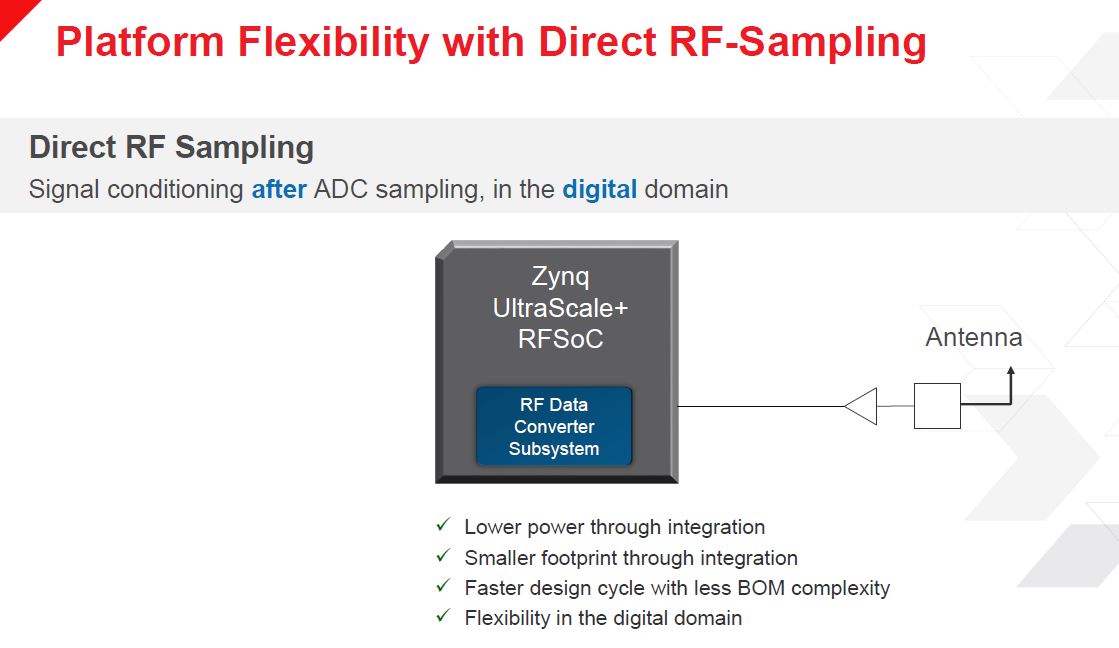

The way that the Xilinx Zynq UltraScale+ RFSoC does this is by integrating the RF Data Converter substem directly into the FPGA.

Instead of having to go from the antenna signal to a bunch of filters and conditioning components, then to a JESD204 interface, then to the digital subsystem, the RF signals go directly to the FPGA.

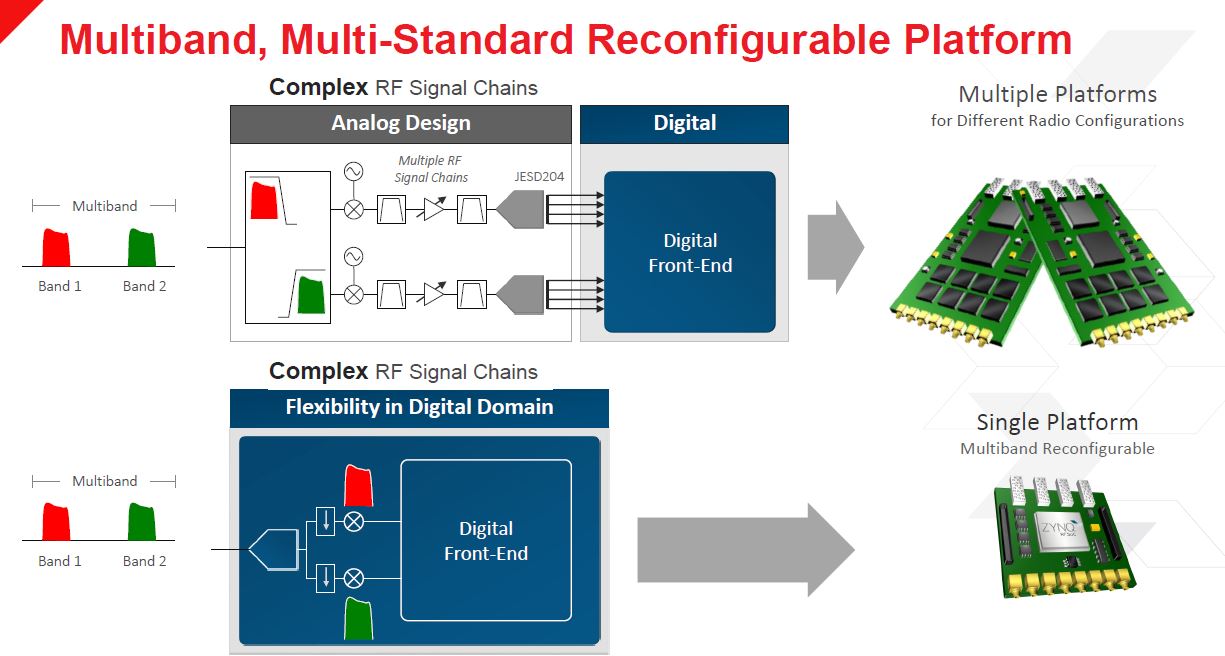

This integration means that one no longer needs additional components and connections between the components and the FPGA, thereby simplifying the design. Further, Xilinx says its solution is reconfigurable. If a carrier wants to deploy across multiple geographies and use different parts of the spectrum, it does not need to have different components for each deployment. Instead, Xilinx is offering software programmability.

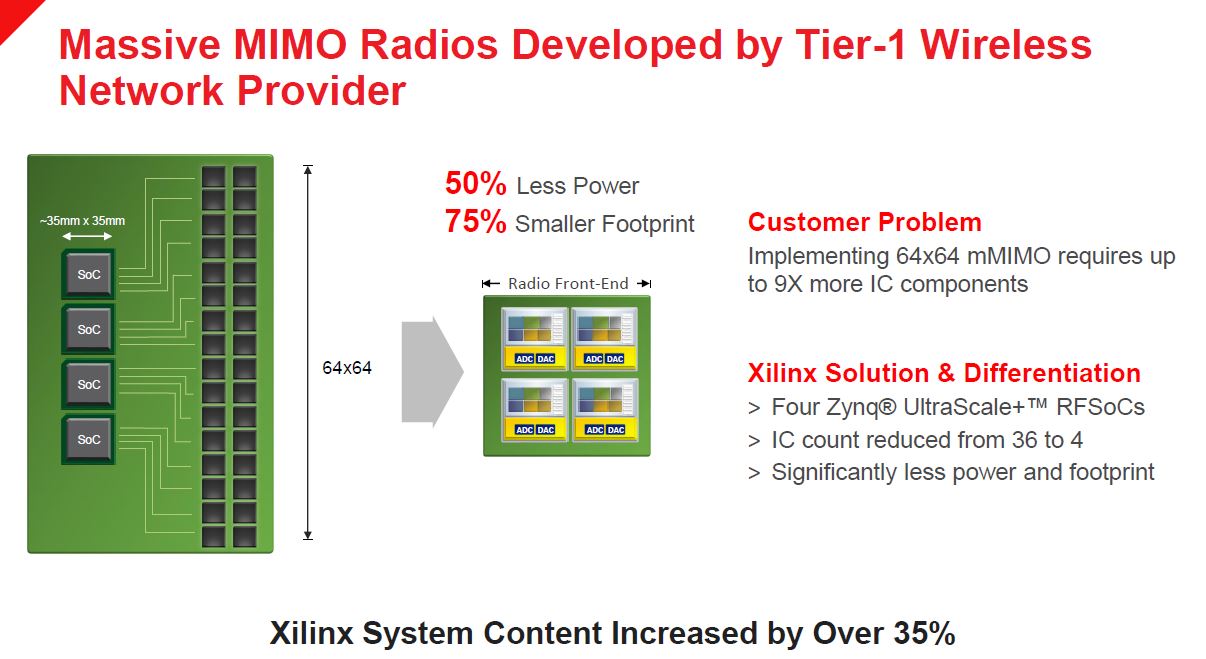

For applications where large antenna arrays are used, this is extra challenging due to additional noise created. Xilinx believes the Xilinx Zynq UltraScale+ RFSoC will be able to handle the increased load while utilizing fewer components. Ultimately, that reduces footprint size and complexity.

Next we are going to look at the Xilinx Zynq UltraScale+ RFSoC Gen 2 and Gen 3 solutions, SKU stacks, and availability.

Cool /johnoliver