One of the areas we have been tracking as a future technology is Silicon Photonics. We discussed this is likely a driver for the Marvell-Inphi Deal and we also covered a Hands-on with the Intel Co-Packaged Optics and Silicon Photonics Switch. At Intel Labs Day 2020, the company showed off its next-generation silicon photonics research with a view on where this is headed.

Intel Labs Day 2020 A Photonics Integration Future

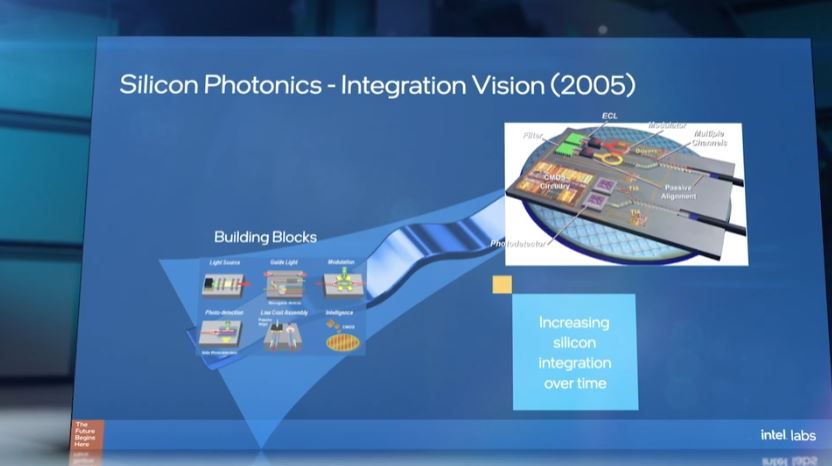

If it seems like we have been hearing about silicon photonics from Intel for some time, we have. Intel laid out a vision fifteen years ago around having chip to chip communication using optics. STH, in comparison, is only about 11.5 years old.

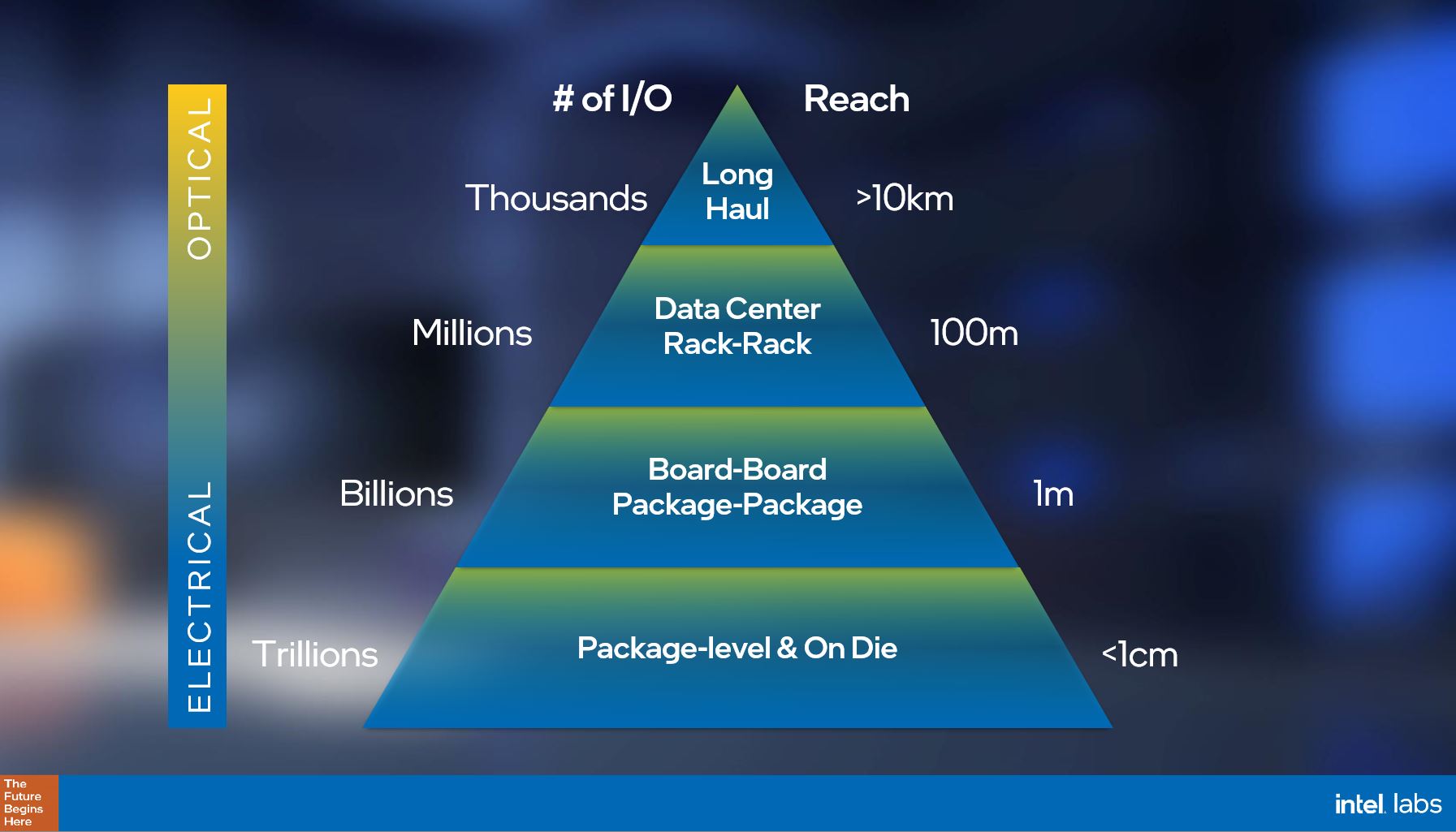

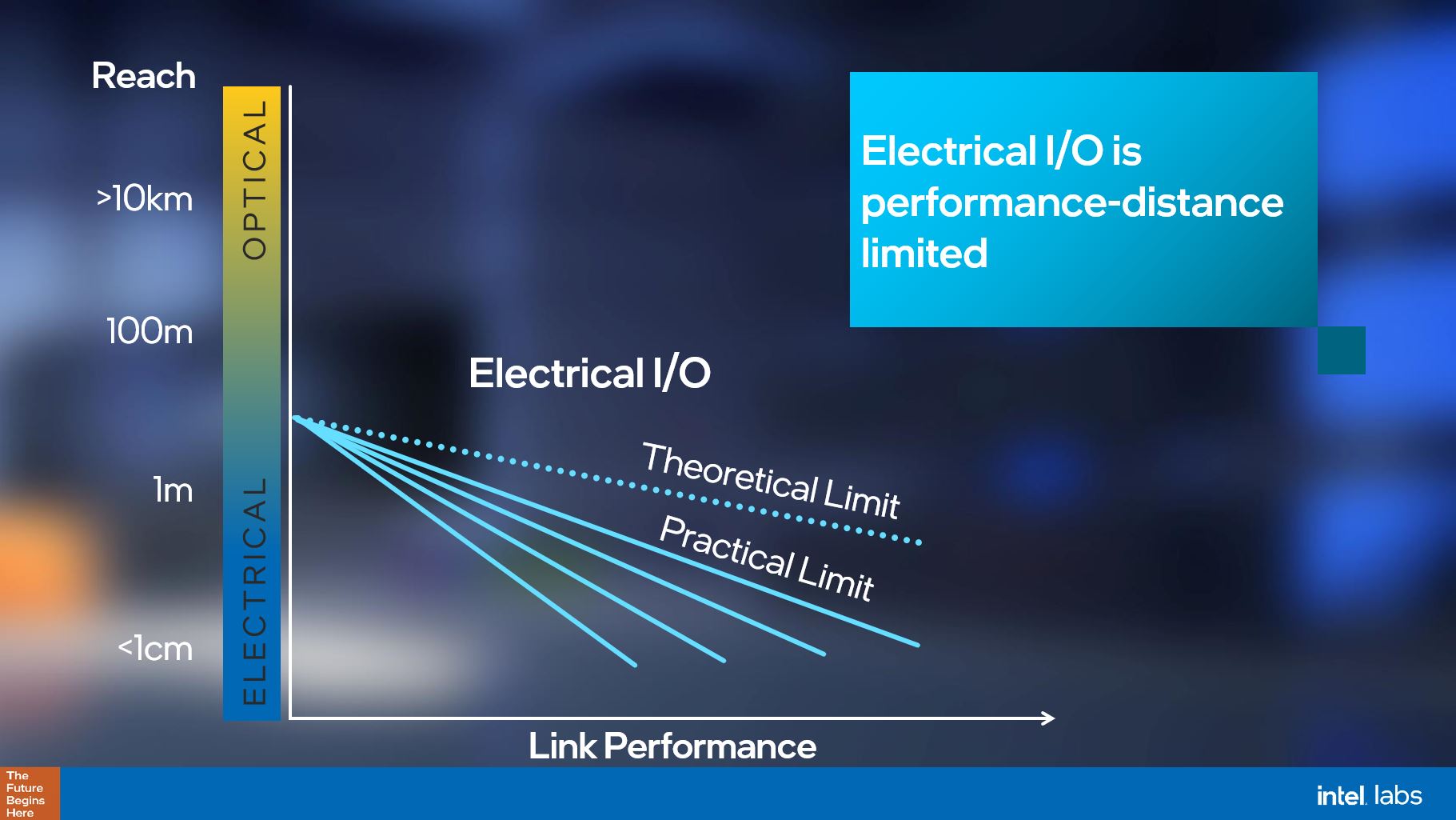

For some time, there has been a hierarchy. Electrical I/O is more efficient on the power side at shorter reaches. At longer distances (outside of the server and rack of servers) the effects of interference and signal processing make optical interconnects more appealing.

Although electrical I/O is fast and low power at short distances, as speeds increase, the reach goes down. It was heralded as a major achievement that NVIDIA Mellanox NDR 400Gbps Infiniband could use DACs in the 3-5m range preserving in-rack electrical efficiency for another generation. Still, everyone tends to agree that eventually as a technology community we are going to see more optical proliferation.

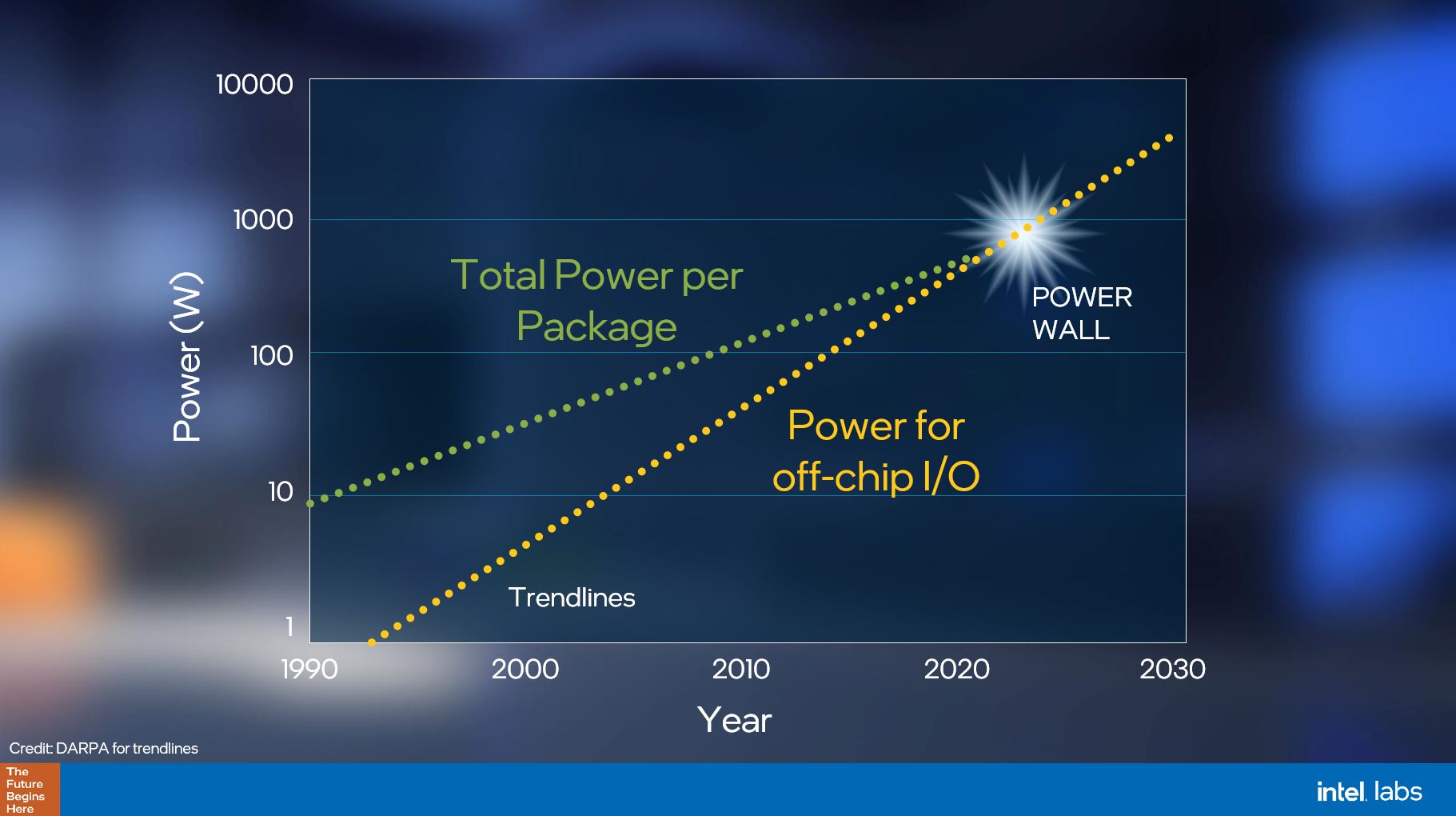

Although opinions vary a bit on when the general consensus is within the next handful of years. Getting I/O out of chips is becoming so power-hungry at higher-speeds that it is starting to consume more of the overall package power budget. At some point, just moving data between packages will use too much power with electrical interconnects.

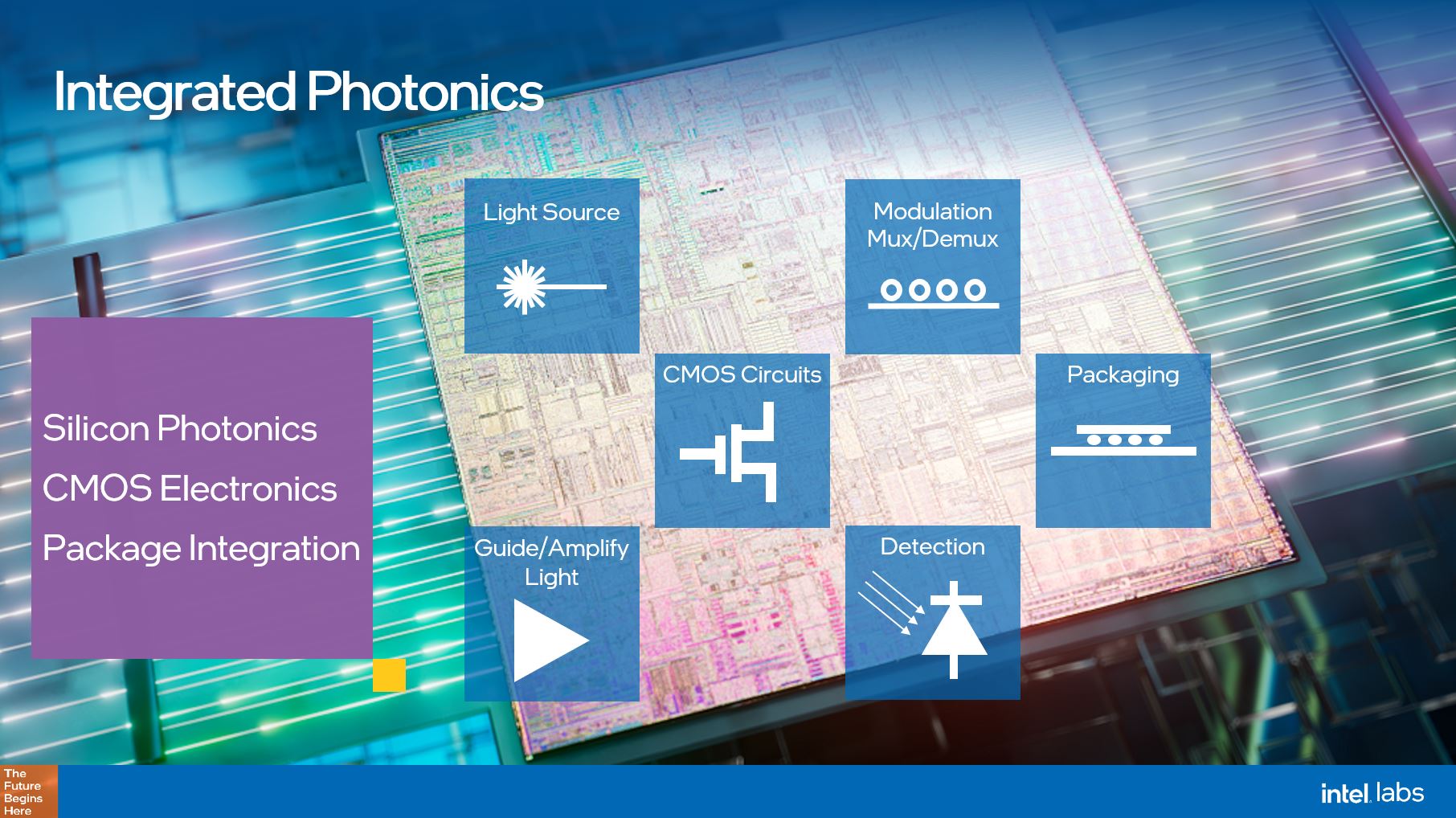

That is effectively where silicon photonics comes in. Instead of the traditional optical transceivers, using silicon photonics with integrated light sources, detectors, and other components means that I/O can be designed and manufactured in silicon rather than using precision modules housed in QSFP style connectors.

While Intel has now sold over 4 million silicon photonics QSFP packages, it knows that this model is bound to change. We already saw its next-gen switch chips hands-on using co-packaged silicon photonics:

For those unfamiliar, the reason switches are a key area of research here is simply that they are effectively massive I/O engines with much more connectivity than we see in CPUs or GPUs.

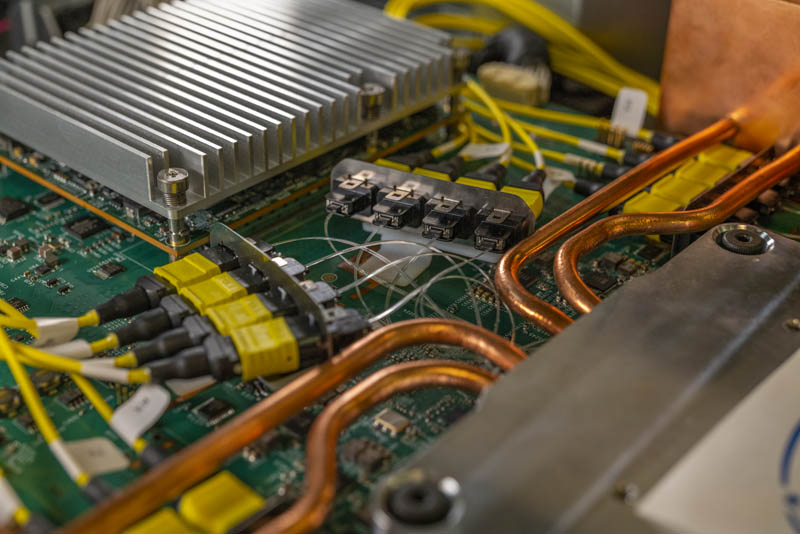

Beyond the switching space, the next step is to push optics beyond the chassis-to-chassis use case of today and down into the fabric of the server itself, often built using PCB and wires.

While the industry agrees that this transition will happen soon, the building blocks are not there yet. I asked Raja Koduri Chief Architect at Intel when he expected this would happen. He said at Architecture Day 2020 that it was less than 10 and closer to 5 years out.

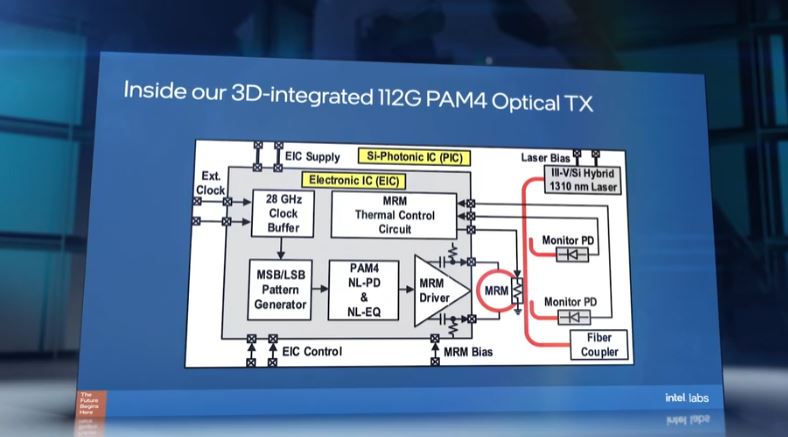

The key challenges are size, manufacturability, and power consumption per bit transmitted. Intel is making new smaller features to address the size. It is creating detectors in silicon instead of an exotic material to aid in manufacturability. Finally, it is finding ways of transmitting more data at a lower power level to increase efficiency.

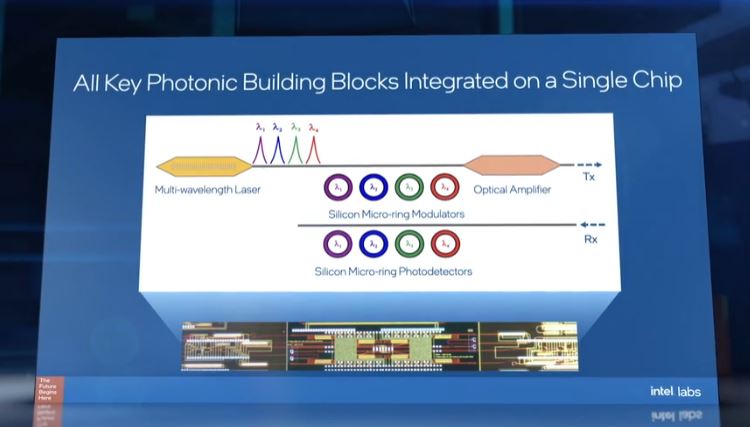

At the Intel Labs Day 2020, the company showed off its latest effort with a CMOS to optical connection.

While in 2005 this was largely a theoretical exercise, the company is now armed with working examples that are a few iterations and innovations away from being viable.

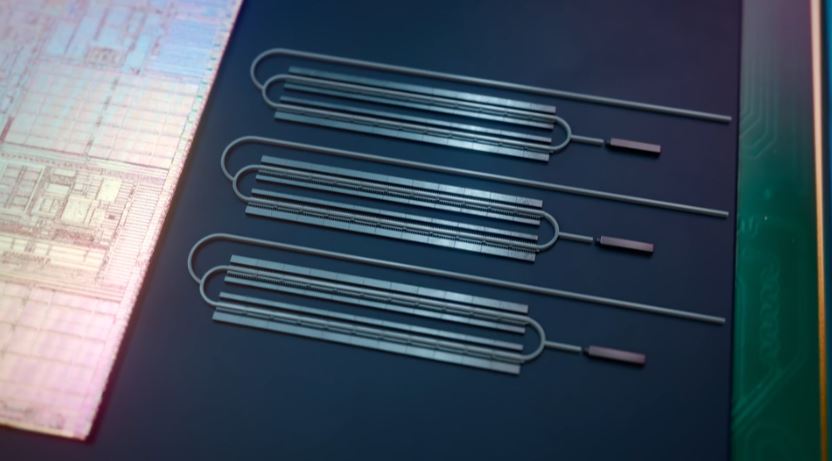

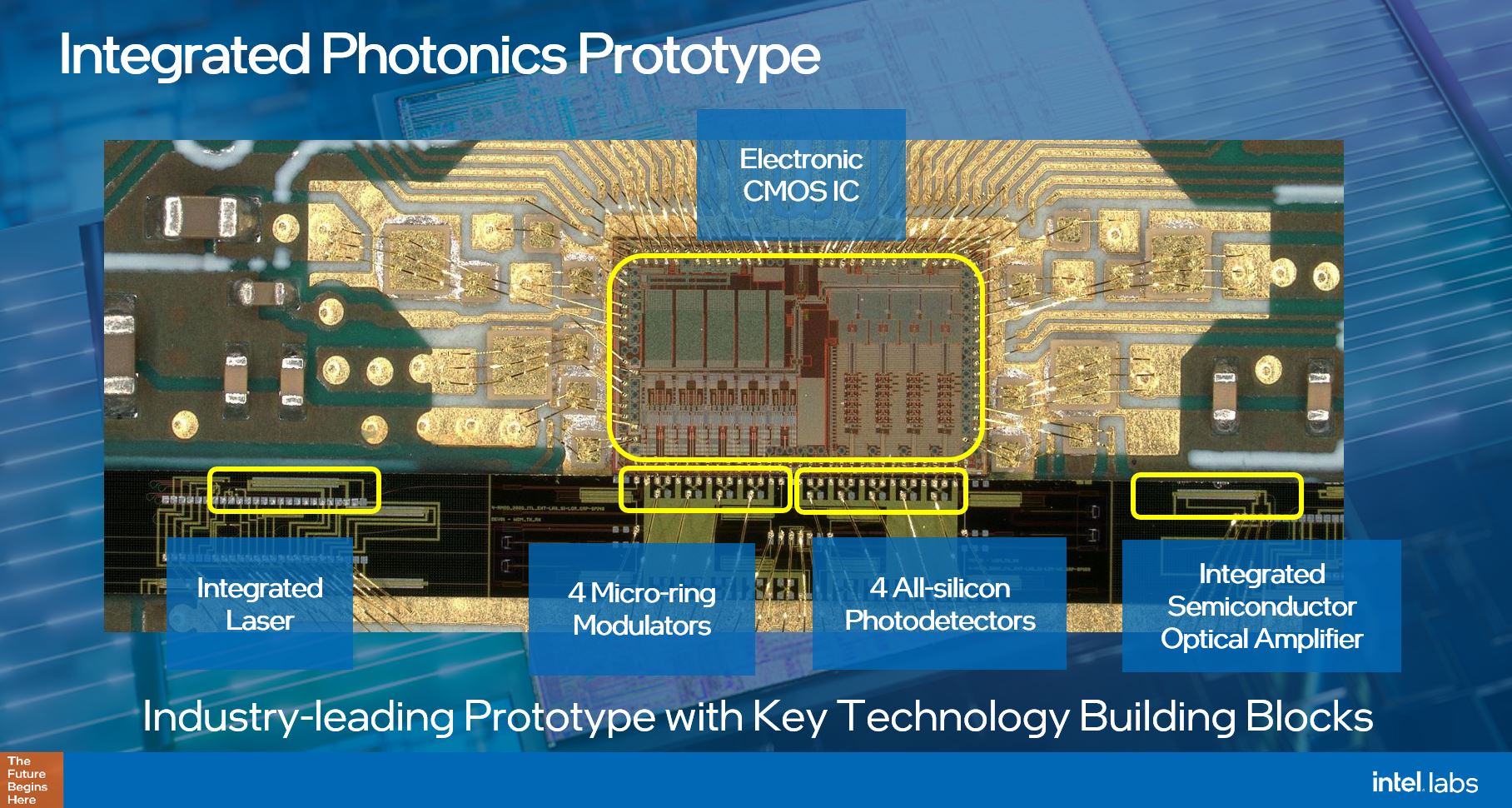

Here is a close-up of the photonics prototype with labeled components that you can find on the slides above.

At the Intel Labs Day 2020, the company showed off this prototype as a next-level integration of its photonics building blocks and packaging.

Final Words

This is a technology that has been 5 years off for 15 years. What is different today comes down to capabilities and needs. Intel is already shipping its silicon photonics transceivers and they are showing higher-reliability in the field than their traditional counterparts. While Intel does not name their biggest customer publicly, they do have a large hyperscaler. Since Intel will not say it publicly, we will, it is Facebook. The key here is that photonics packages already exist and with 4M units sold it is likely a good size revenue stream already.

Looking to the future, we have already seen co-packaged optics in switches. Data center switches are now at the point where people are discussing if it is one, two, or three generations away from where we will have co-packaged optics. That is where silicon photonics will make a big impact. We see this as the next major use case because customers, facilities, and the ecosystem already operate optical networks.

Beyond the switching market, inside servers, PCIe Gen5 will happen, albeit often with more cables and retimers than we see with PCIe Gen4. As a result, we do not think 2022-2023 is going to see widespread Xeon with co-packaged optics. As we move to PCIe Gen6, we are likely going to hear more chatter, and perhaps some edge cases where optics will be used, but many in the industry are going to push electrical transmission and there is a good chance it is still strong there. The question is whether getting beyond that generation means we need optics to deliver the required power per bit transmission rates.

If it seems like we have been covering silicon photonics a lot more since Intel Silicon Photonics Update at Interconnect Day 2019, we are. This is a technology moving from theory to shipping products in edge cases and on a path towards being a foundational building block of infrastructure.

You know what Amazon uses?

While Intel does not name their biggest customer publicly, they do have a large hyperscaler. Since Intel will not say it publicly, we will, it is Facebook

That gave me a good chuckle :D

Maybe this means that actual optical processors are going to be the “next big thing” soon now that we can do this with switching and I/O hardware. I’m curious how much longer it will be before consumer PCs will begin featuring this tech. Very cool development, and one I’m more interested in than AI accelerators. Star Trek isolinear photonic computer anyone?

Really more futuristic for me than the whole ai dystopic shit (sorry i care more for human rights than enterprise revenue) we’re living.

Stephen, get out with your trekkie things, here we praise the one and multiple doctor :p jk

@ServerGarbage LOL!! It’s okay, you’re cool! Actually, ya made my day with your matter-of-fact commentary about the “cyberpunk dystopia” that is present-day life. I’m with you, brother. Human rights and freedoms should NEVER take a back seat to monetary gains. PEACE!! :-) Also, I do praise the Great Doctor, too. Especially Tom Baker’s role as the Doctor.