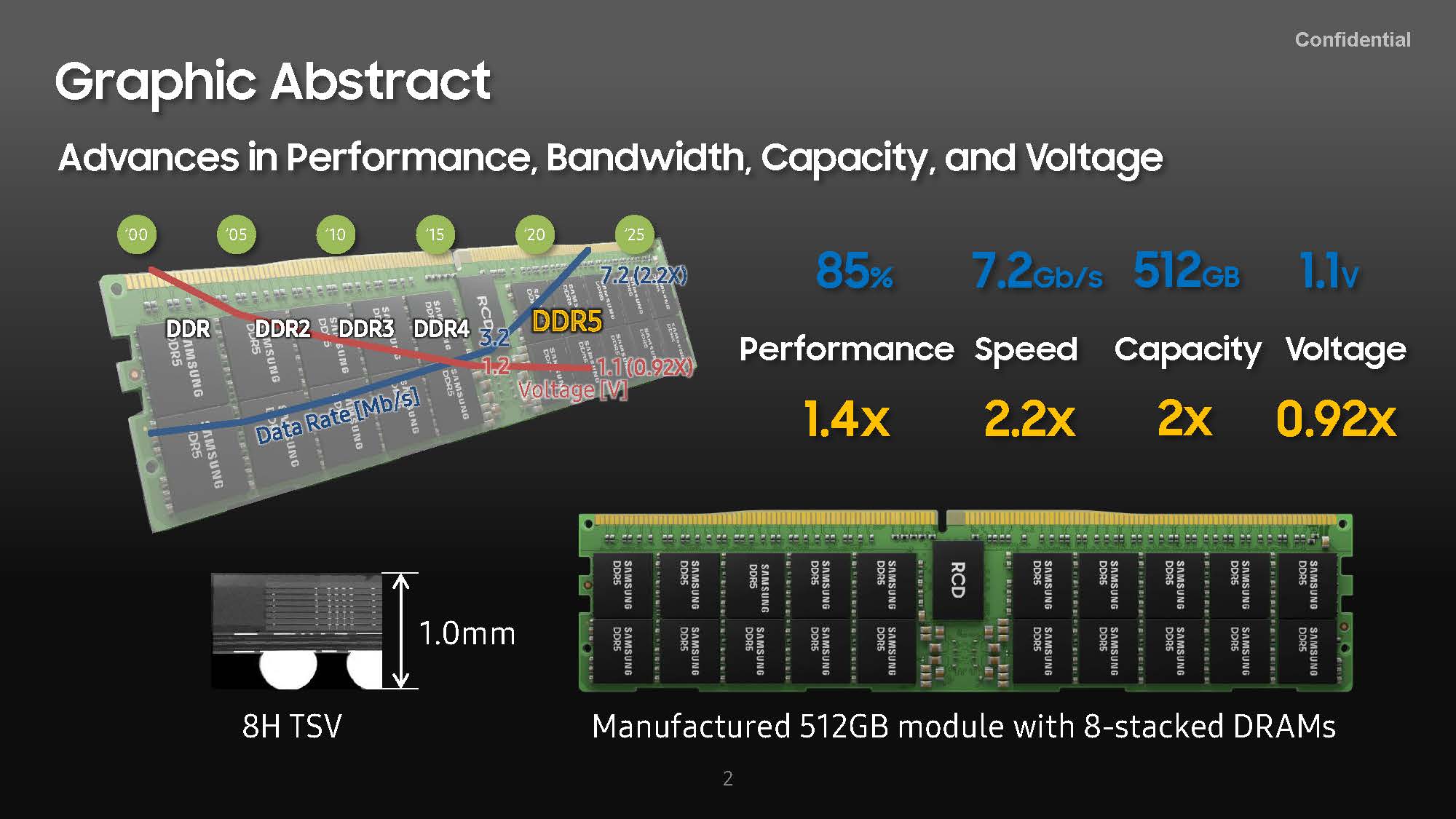

At Hot Chips 33, Samsung discussed its next-generation DDR5 memory technology that is designed to increase the performance and capacity of memory. Specifically, the company is already discussing 7.2Gbps 512GB modules and is looking to go beyond those figures in the future.

Samsung Unveils 512GB DDR5 Memory

Here is the chart showing what is happening with Samsung DDR5. Effectively Samsung says it is able to get more performance using 8-stacked DRAMs at higher speed, capacity, and at lower power.

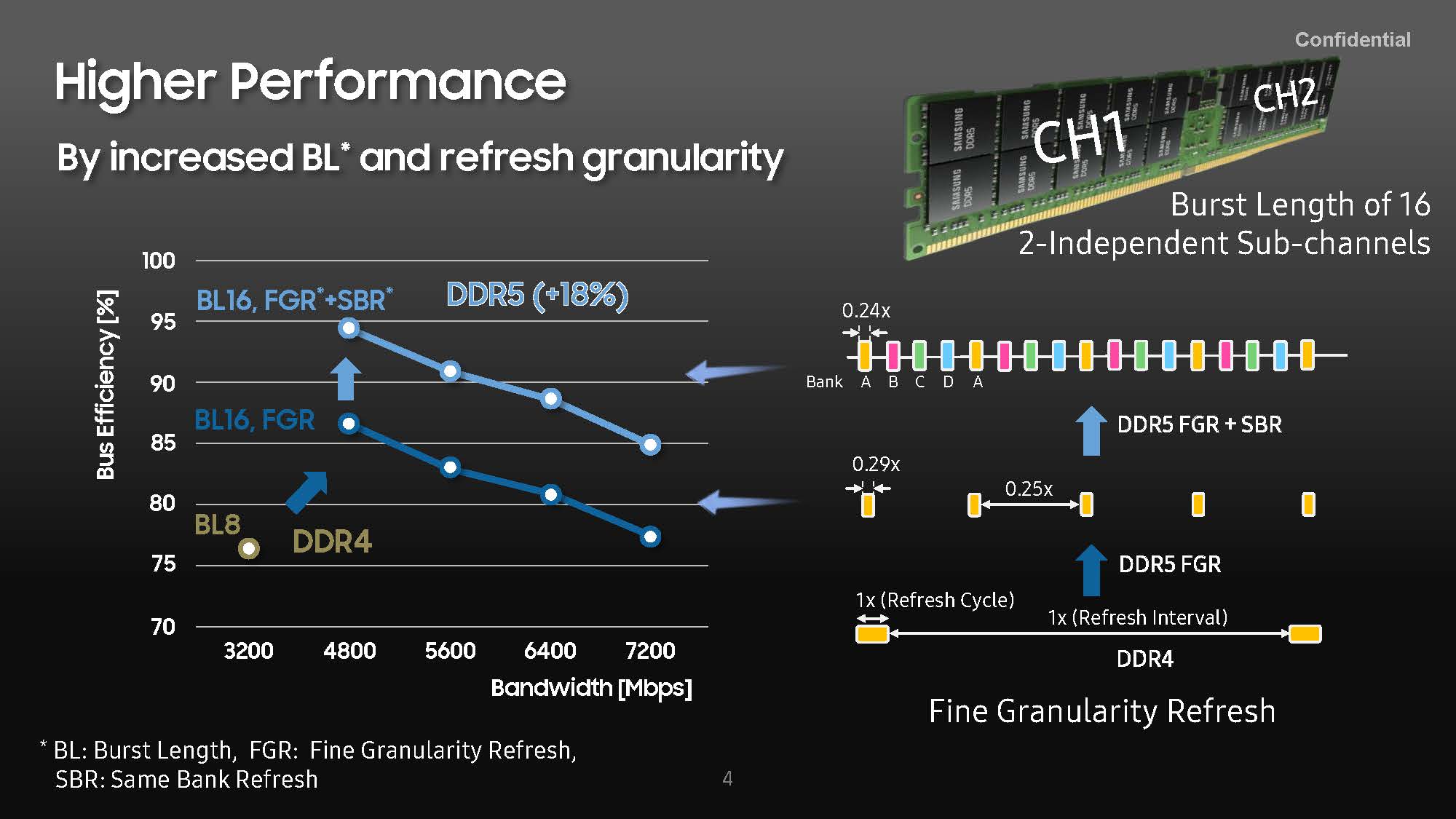

On the performance side, DDR5 has two channels on each memory module and is designed to have a higher burst length while also having better refresh characteristics that will allow higher performance.

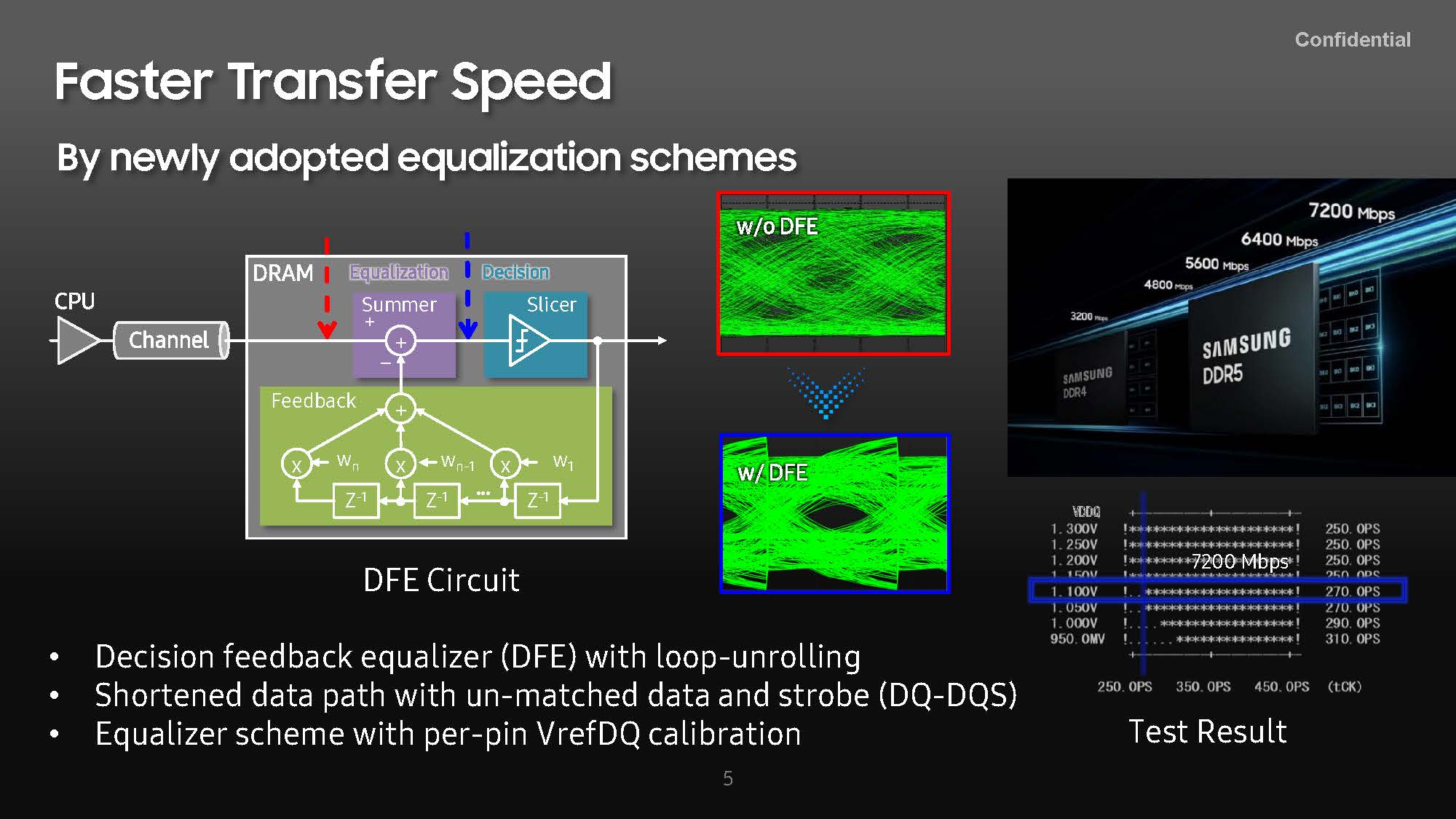

The new memory technology allows for faster transfer speeds at lower voltage due to new circuits that make signal processing cleaner.

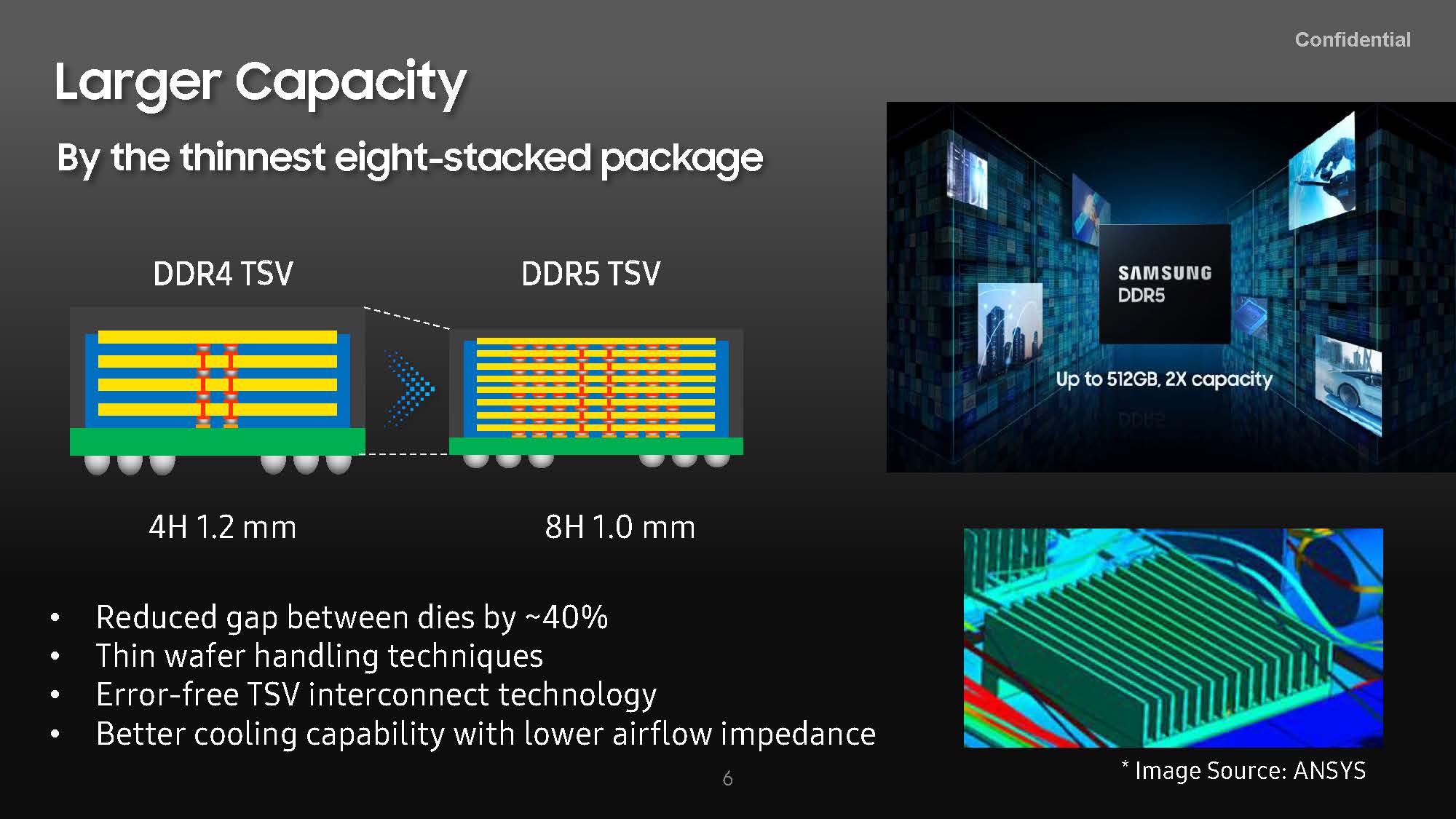

One of the cool technologies is that DDR5 allows for more Through-Silicon Via (TSV) stacks. TSVs are a way to pass data/ power through stacked dies and are used extensively in different areas of chip design already. There is certainly TSV in this current DDR4 memory era. Those who have tried TSV memory in the DDR4 generation, especially in the 2017-2018 timeframe may have noticed that some CPUs, did not support DDR4 TSV modules. With DDR5, TSV is going to become a more standard technology. Beyond becoming more widespread, better manufacturing technology will allow more TSVs and more die stacking for higher capacity DRAM modules. Samsung is already claiming doubling capacity with 512GB but is also looking to the TB era.

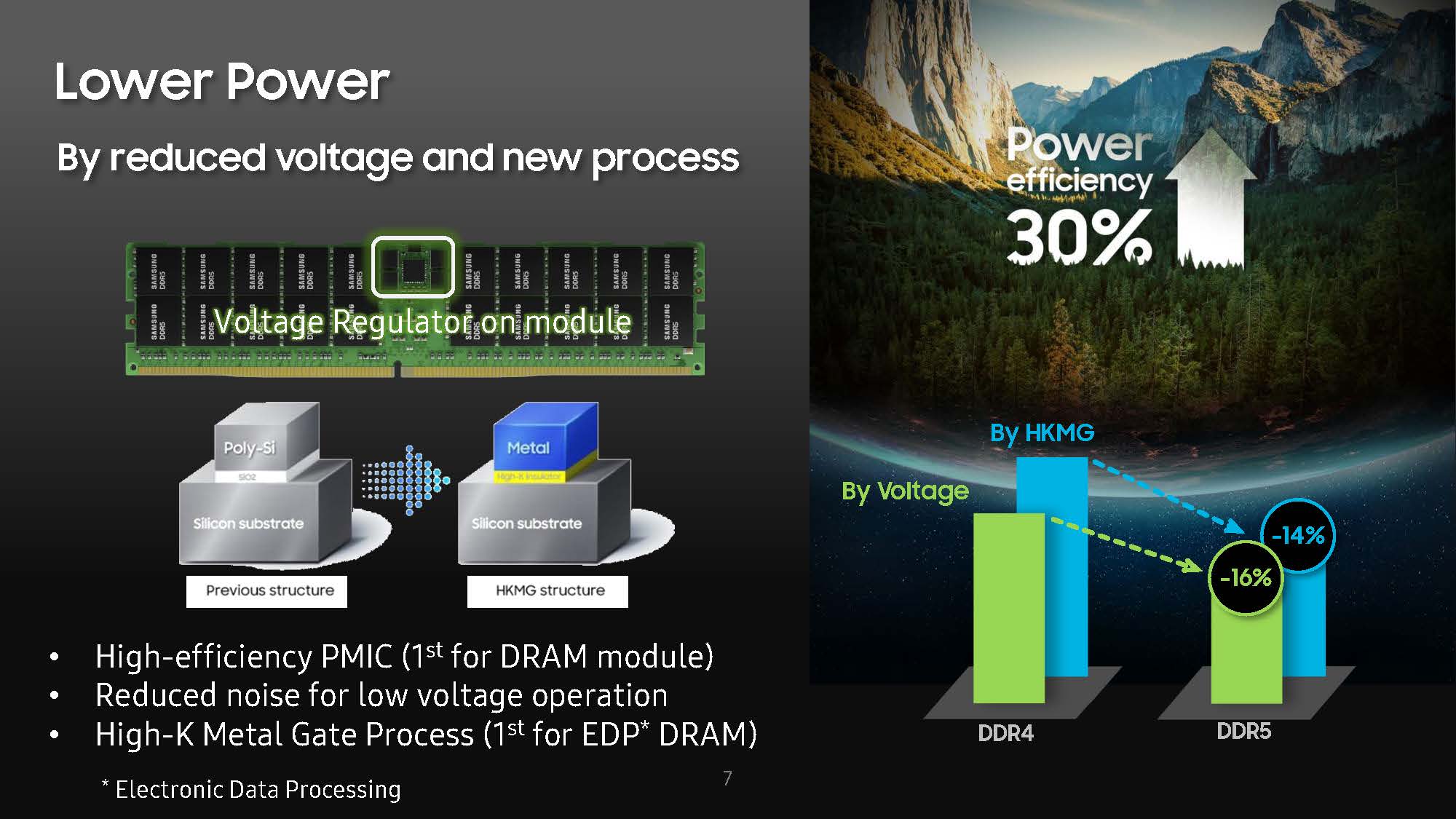

The new DDR5 modules will have a high-efficiency power management integrated circuit (PMIC) and use high-K metal gate (HKMG) process to increase power efficiency. While we often see 1.2V DDR4 modules, we will see DDR5 at 1.1V.

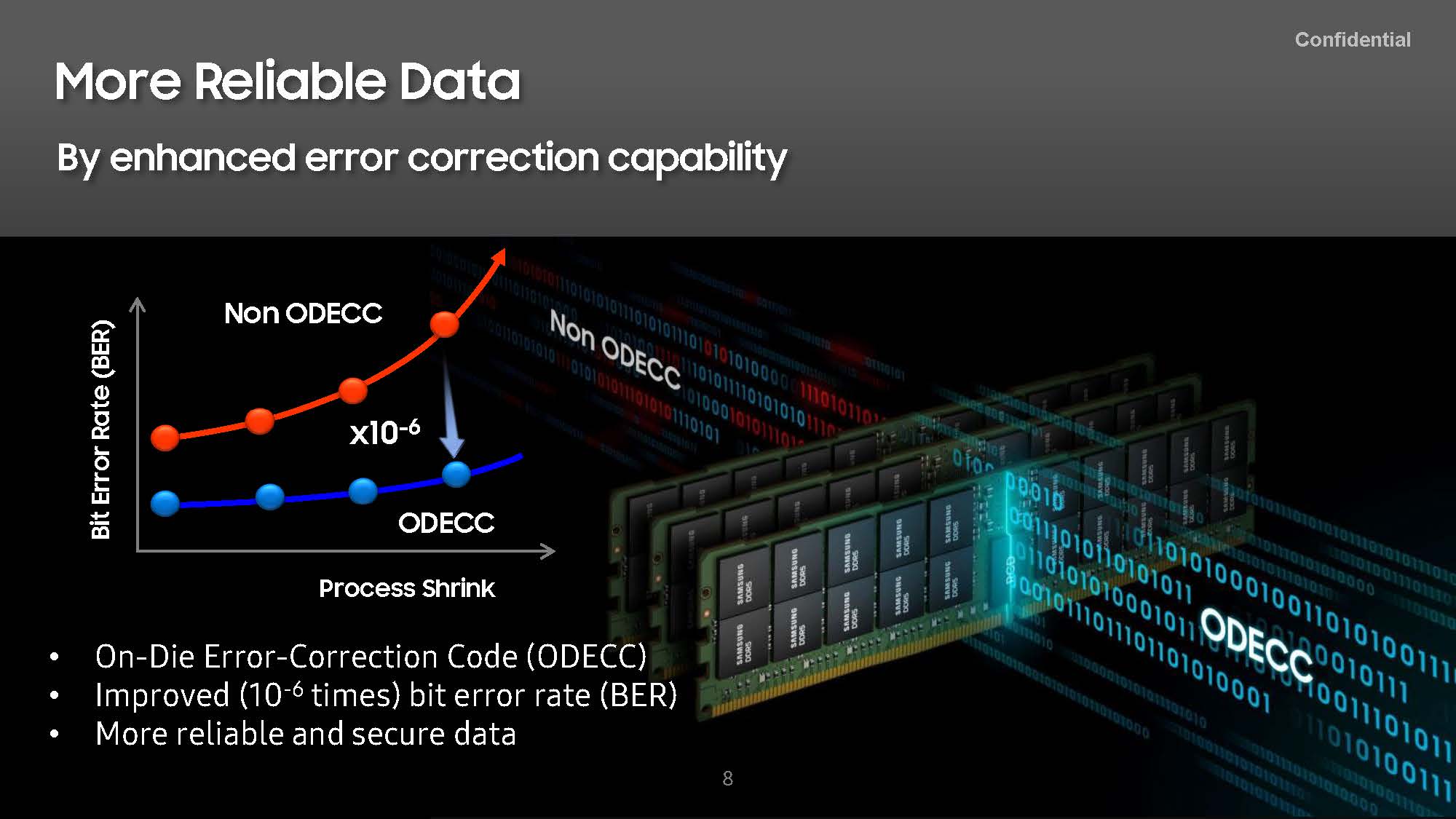

Something that is often misunderstood is the on-die error correction code (ODECC). As with NAND, the dies will need to have their own ECC before reporting up to the higher-level memory structures. The ECC we tend to see referenced in server specs is not the baseline ODECC functionality. ODECC has become standard in storing data on dies using more advanced processes whether that is NAND or DRAM.

Overall, DDR5 will be a big driver for the industry as it offers more capacity and performance at a lower power budget.

Final Words

Samsung says that this technology is not far away. Instead, it will be ready for mass production of 512GB by the end of 2021. Generally, when semiconductor companies say that a product is ready for mass production within 4 months, the technology is fairly well sorted so this seems strange. For those wondering, Samsung expects DDR5 to overtake DDR4 in 2023-2024.

Ramping KHMG and higher-end TSV enabled chip stacking are not free. As we saw with the DDR3 to DDR4 transition, early adopters often pay an outsized premium for the new technology. Expect DDR5 to be quite costly. We also expect technology such as Intel Optane to have to adapt to the higher capacity and performance modules in order to stay relevant as Intel reiterated Sapphire Rapids Xeon with Optane PMem 300. For Samsung’s part, it is interesting to think about higher-capacity DDR5 attached via the company’s Samsung CXL Memory Expander with DDR5.

On some future DRAM overview or benchmark, it might be illuminating to include a chart of latency over time, perhaps going back to the Mostek MK4096 of 1973.

And by latency, I mean actual nanoseconds for random first-byte-out, and not CAS cycle counts.

So on the sub channels, does that mean that you can get two memory channels from the CPU to a single stick of memory? I’m imaging getting DDR functionality with a single stick of ram, instead of needing two.

Dual channel DDR5 chips….maybe Epyc-Zen4 12 channel (leaked) is looking more useful than I initially thought.

@ Bob Niland

I always though the latency was offset by higher frequencies, essentially becoming a net-zero increase in latency as the module frequency increased. The desire for increased DRAM bandwidth surmounted latency where L1-L4 cache is supposed to do that job. I would be curious to see it too.