Intel Agilex FPGA Overview

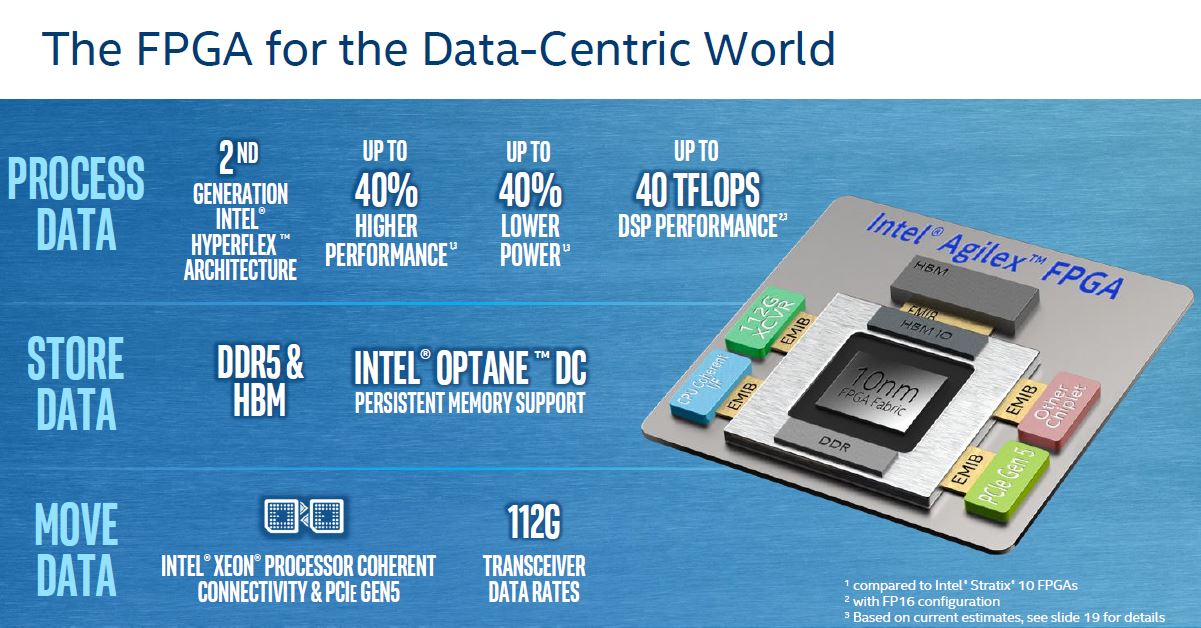

In a new 10nm FPGA generation, the Intel Agilex is designed to be a platform to provide programmable logic tied to big I/O pipes. That includes HBM and DDR5 memory subsystems as well as Intel Optane DC Persistent Memory Module (DCPMM) support.

Beyond the faster 10nm logic and memory, the new FPGA promises 112G transceivers, PCIe Gen5, and a coherent interconnect via CXL. Here is the official punch list from Intel:

- Compute Express Link: Industry’s first FPGA to support Compute Express Link, a cache and memory coherent interconnect to future Intel® Xeon® Scalable processors.

- 2nd Generation HyperFlex: Up to 40 percent higher performance, or up to 40 percent lower total power compared with Intel® Stratix® 10 FPGAs.

- DSP Innovation: Only FPGA supporting hardened BFLOAT16 and FP16, providing up to 40 teraflops of digital signal processor (DSP) performance.

- Peripheral component interconnect express (PCIe) Gen 5: Higher bandwidth compared with PCIe Gen 4.

- Transceiver Data Rates: Support up to 112 Gbps data rates.

- Advanced memory support: DDR5, HBM, Intel Optane DC persistent memory support.

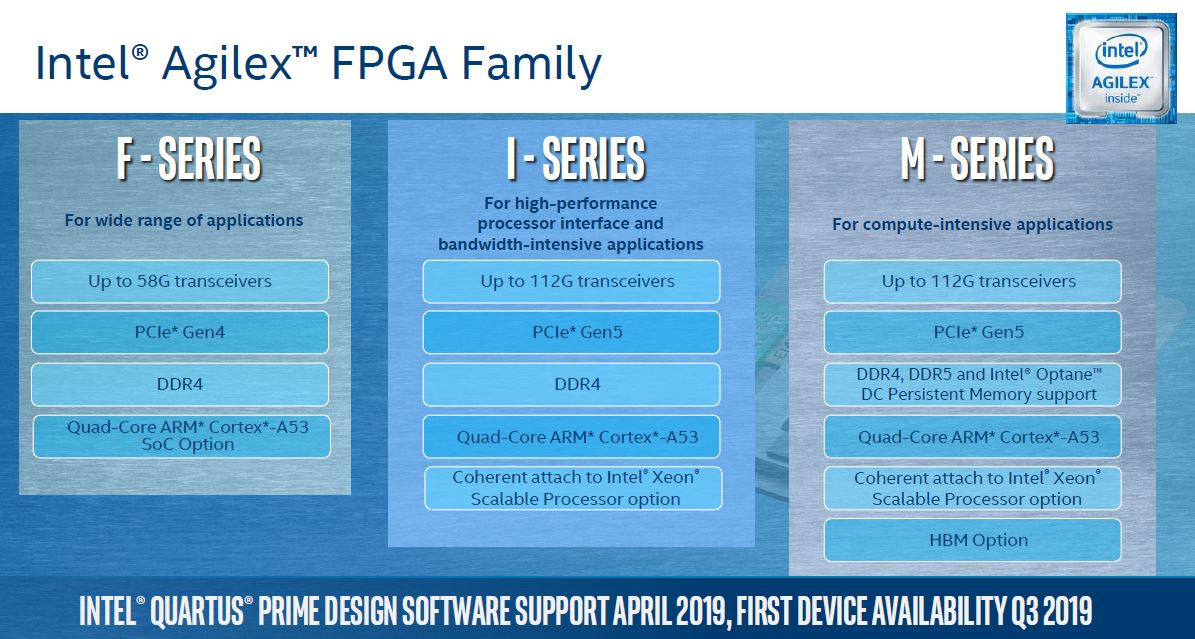

There will be at least three different Intel Agilex FPGA families, the F, I, and M series. First out of the gate will be the F series which does not support the two “5’s” of PCIe Gen5 and DDR5 along with 112G transceivers and the coherent interconnect. On 10nm Intel has PCIe Gen4 IP, and so we expect to see this come later in 2019 and into 2020 as Intel expands the use of its new process node.

The I and M series will be subsequent releases. That we expect more than a year out with the full feature set.

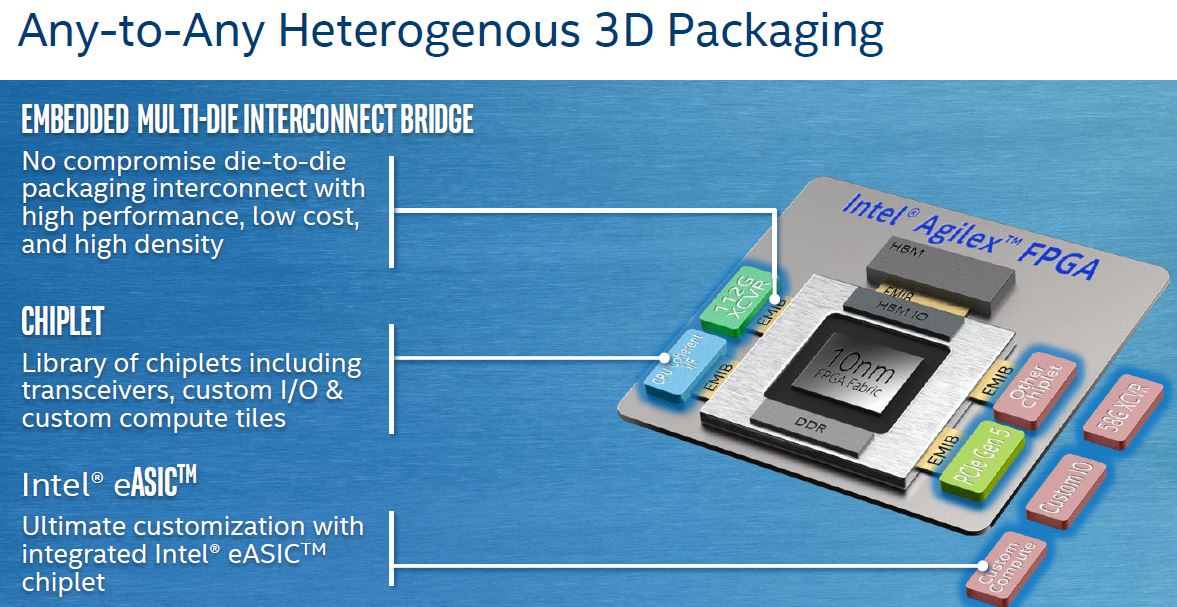

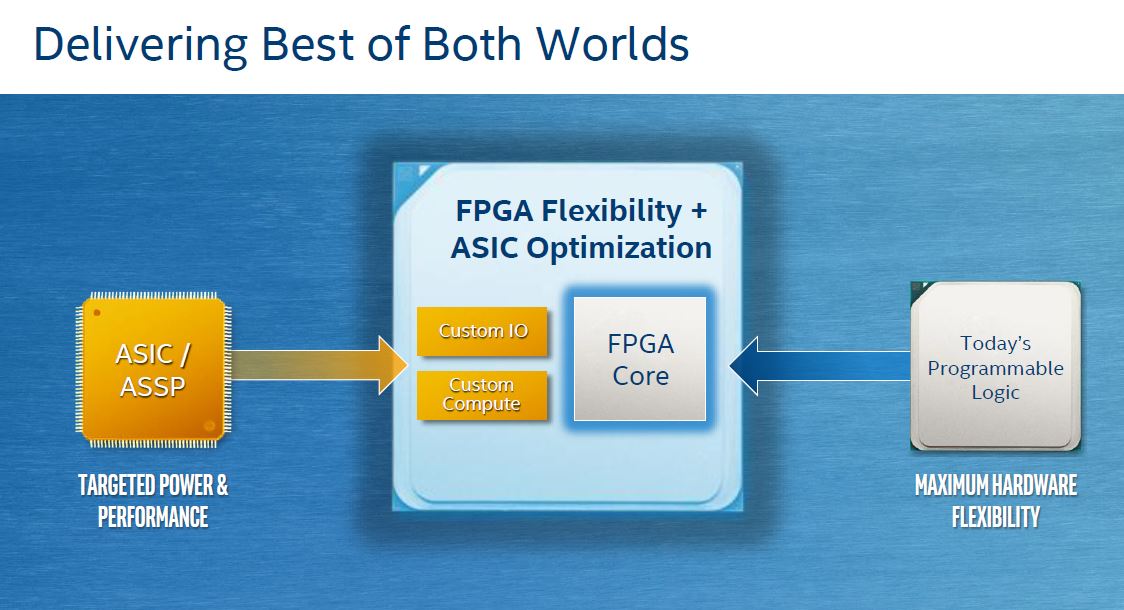

Beyond the transceivers and PCIe, Intel envisions Agilex as a platform for a diverse set of chipsets. Intel eASIC is a recent acquisition that brings the capability to quickly harden logic and get the cost benefits of ASICs for elements that need to scale at lower costs.

The other key capability is being able to incorporate silicon from different foundries. On the conference room table, there was a Stratix 10 chip on 14nm with HBM and TSMC 16nm SerDes. Intel is pushing EMIB as an integration method for heterogeneous silicon.

The transceiver leadership is important for Intel Agilex because of bandwidth in the data center and upcoming 5G networks are going to put immense pressure on simply moving data both from node to node as well as within a system.

Intel has started to talk about coherent interconnects in terms of CXL. This is key to Intel’s strategy of selling the right silicon for the job to increase TAM. Selling the right silicon means selling different types of silicon and Intel needs a better way to link all of its products. The company did not say CXL is its onramp to Gen-Z, but that certainly seems to be the trend.

With eASIC and EMIB integration, Intel Agilex can combine programmable logic for changing workloads along with ASICs for fixed logic that needs better economics.

Overall, this is about what we would expect in the FPGA space with a new generation coming out. We did get to see PCIe Gen5 and 112G demos even though they are not shipping in volume in 2019.

Agilex PCIe Gen5 Support

One area that I wanted to address was PCIe Gen5 support. When we were first briefed on Intel Agilex, seeing PCIe Gen5 when Intel is still not supporting PCIe Gen4 on their Xeon chips (yet), seemed fanciful.

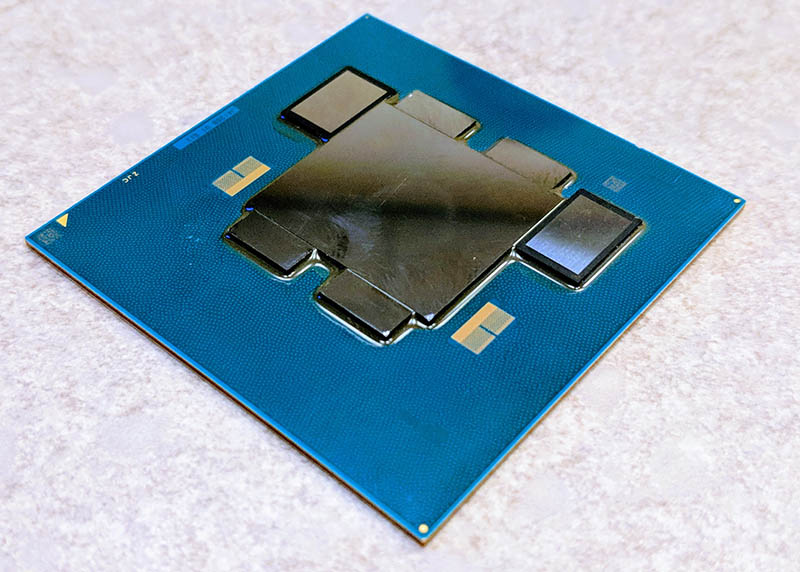

During my visit to the Intel campus that was Altera’s former headquarters, I had the opportunity to see a 10nm test chip for PCIe Gen5 both as a chip, and running a demo negotiating link speeds from PCIe Gen1 through Gen5.

Modern systems have auto-negotiation that allows backward compatibility in slots. A key mechanism is that both the host and device start speaking over PCIe 1.0 then work up to their maximum speed. If you took a current Intel Xeon Scalable second generation CPU and added an Intel Ethernet 800 series 100GbE OCP NIC, for example, you would likely see PCIe Gen1, then Gen2, then Gen3 communication being successively negotiated between the two. That was the demo I saw.

The key takeaway is that Intel has PCIe Gen5 running on a 10nm test chiplet in the lab that looks very much like what is attached to current Stratix 10 chips pictured above.

Final Words

Intel Agilex is the next-generation 10nm FPGA that is designed for the company’s customers who need to deploy high-performance programmable silicon. What the company is unveiling is a natural progression of the platform. It was great to see another 10nm test chip running PCIe Gen5.

Perhaps the biggest obstacle to expanding the TAM of Agilex is brokering those who are creating the logic IP to accelerate key workloads and getting that IP into the hands of organizations large and small. The key takeaway here is that Intel has a plan to tackle the challenge over the next few years and make FPGAs more accessible to others.