At Hot Chips 30, the CEO of Xilinx, Victor Peng, gave an awesome keynote about the company’s vision. We are going to take some notes of the live presentation here. The page will refresh every few minutes with more information.

Xilinx and Pervasive Intelligence Background

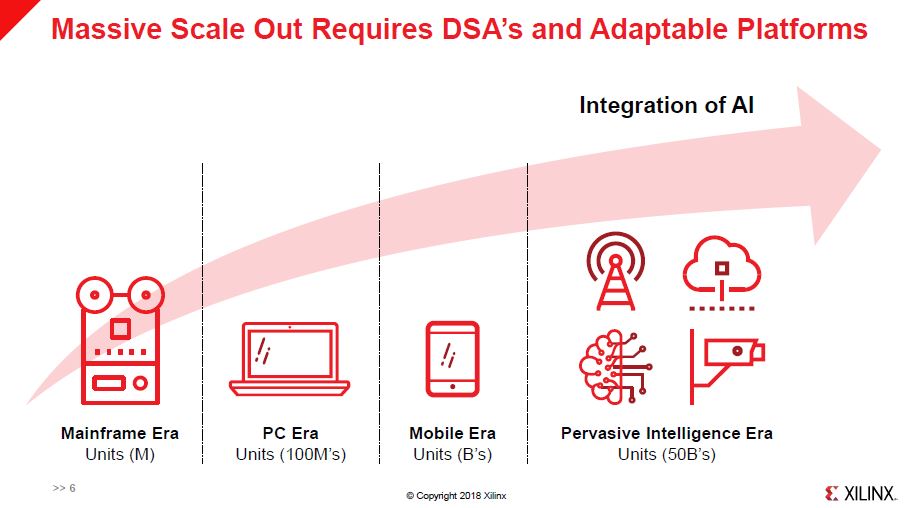

The keynote started with a nod towards the idea of pervasive intelligence. Everywhere that there are machines or sensors, we are seeing more intelligence.

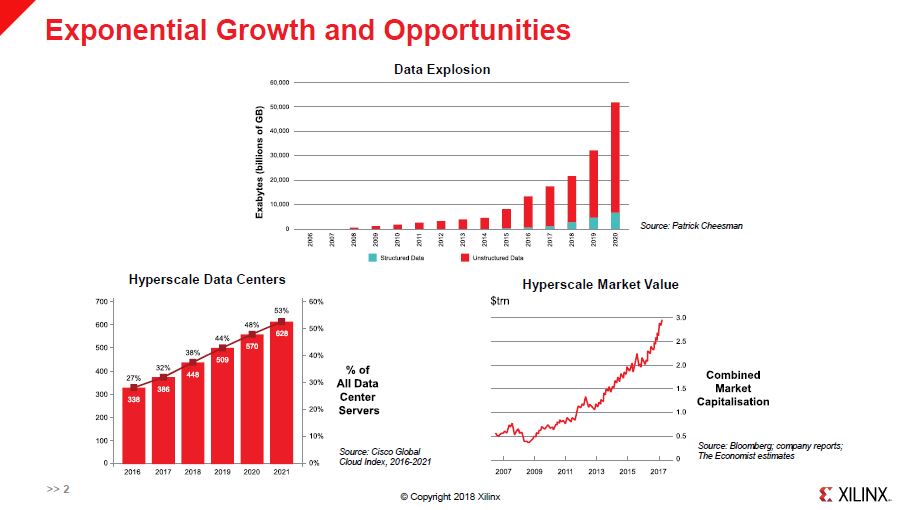

Hyperscale data centers are growing as a percentage of overall data center spend. The growth in data and market caps show that there is an opportunity.

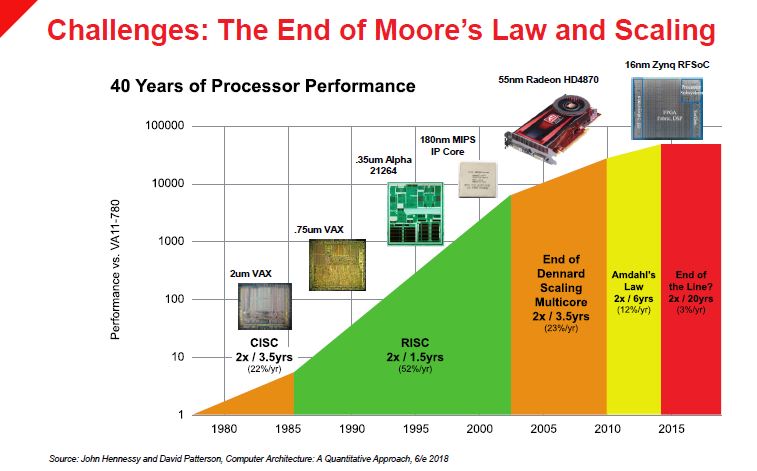

Moore’s law and Dennard scaling are slowing down, creating challenges meeting the computation needs of the data being generated and intelligence required.

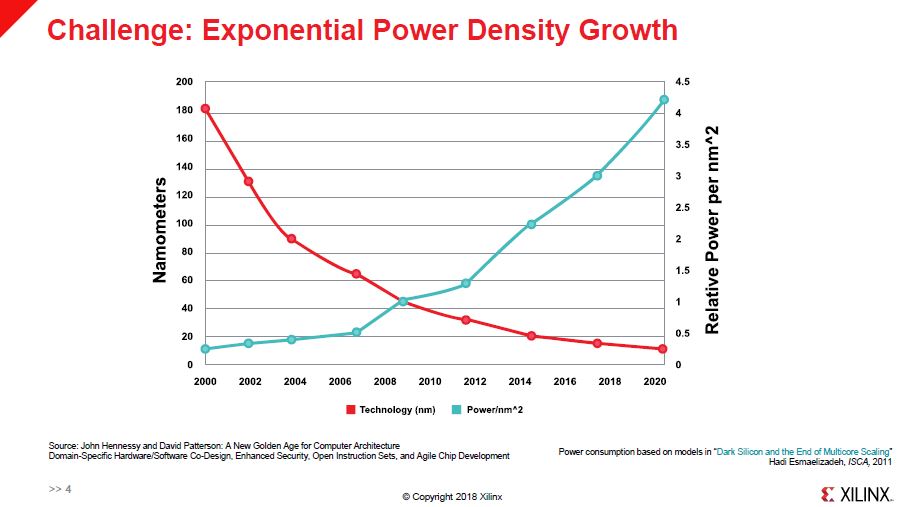

A key challenge is the power density growth. Power is seen as the main limiter toward next-generation applications. We can build more chips, but not power efficient enough.

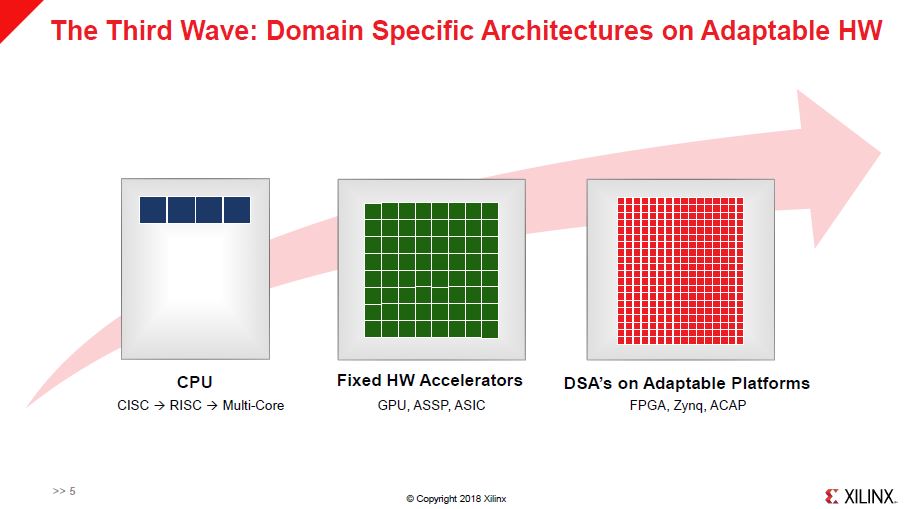

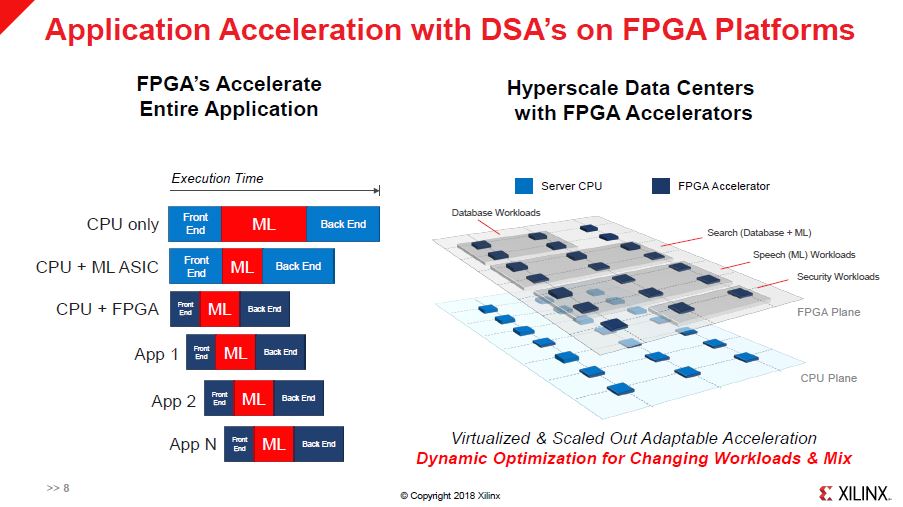

One of the new waves is domain specific architectures on hardware that can adapt to different workloads. This includes CPUs, GPUs, and FPGAs.

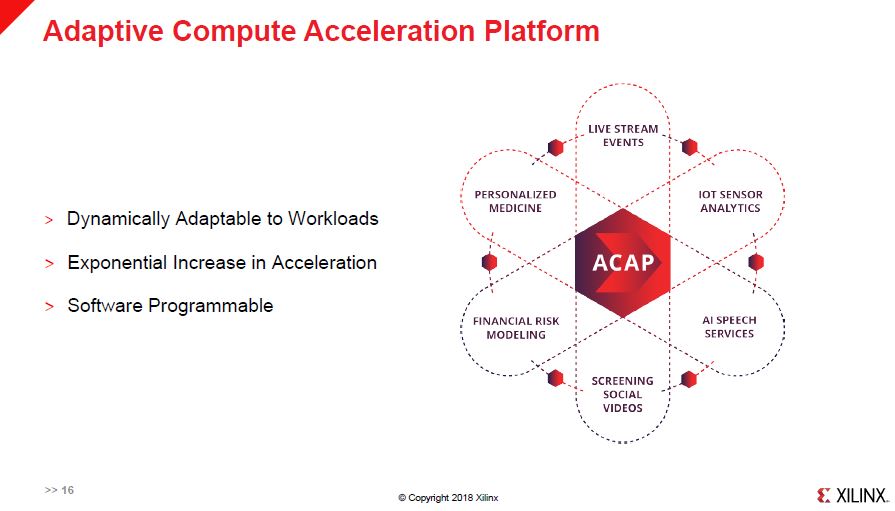

Victor Peng’s anecdote is that the most adaptable species wins in evolution. That is part of the Xilinx ACAP program.

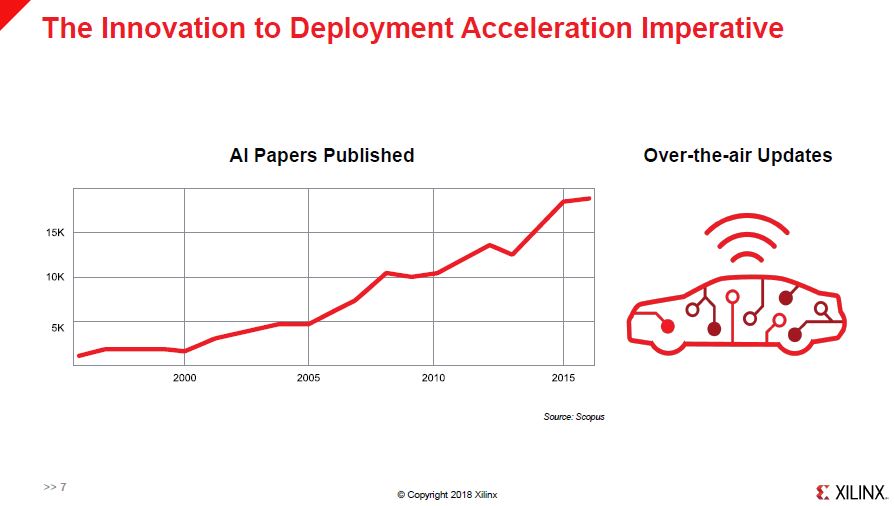

Automobiles of the future want over the air updates.

How Xilinx is Addressing the Market

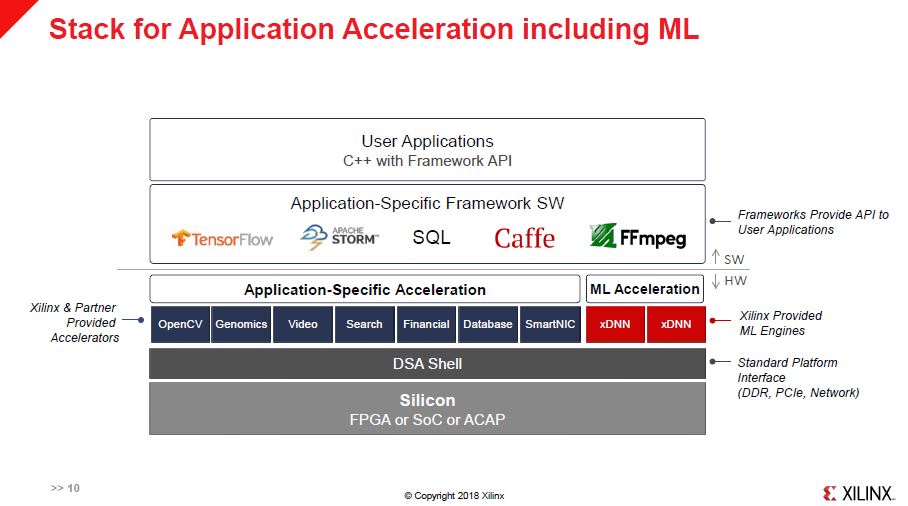

Application acceleration can happen with FPGAs at the speed of software updates, rather than hardware spins.

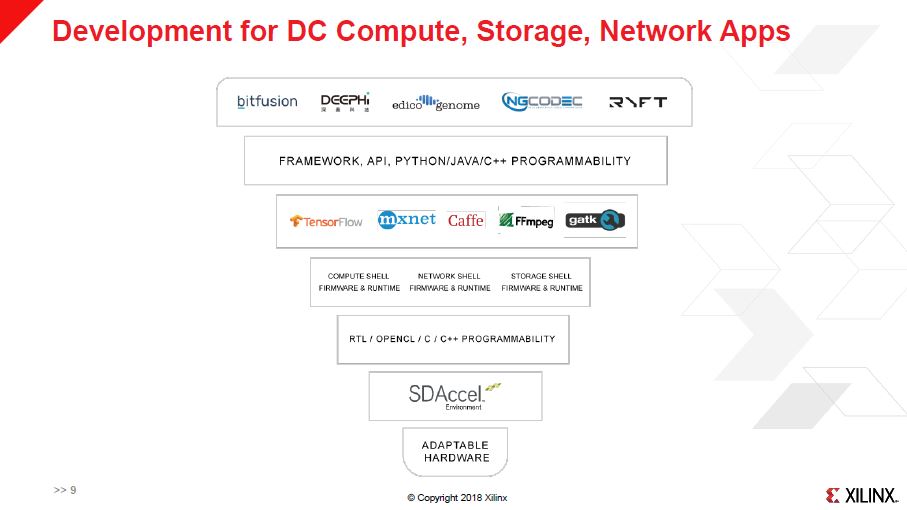

Development for data centers means that the company is part of a large ecosystem enabling the next-generation of intelligence.

The company is working with applications and machine learning developers to help software developers use FPGAs at a lower power and higher performance.

Xilinx ACAP Performance

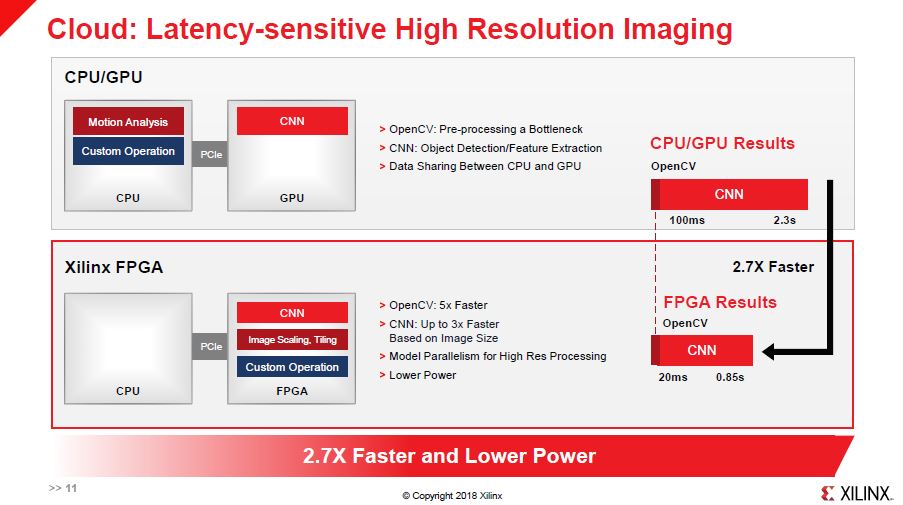

The performance of the solutions can be better than GPUs. Using AWS instances, for latency-sensitive high-resolution imaging.

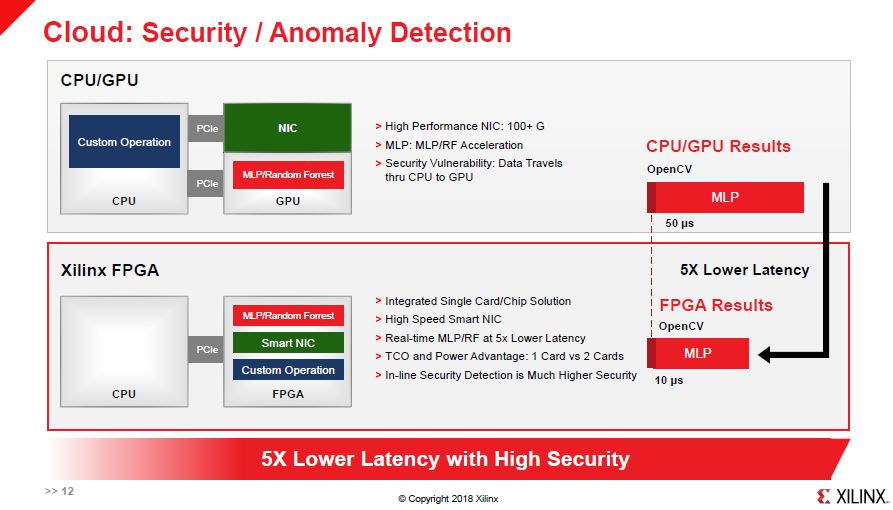

It can also help in cases of security and anomaly detection.

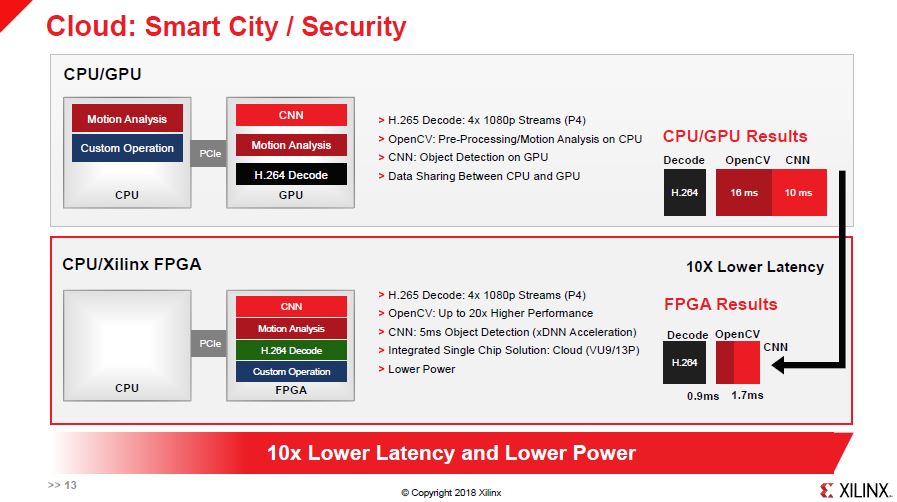

For smart cities, and security, Xilinx is showing image recognition, transcoding and tagging workloads on their architecture.

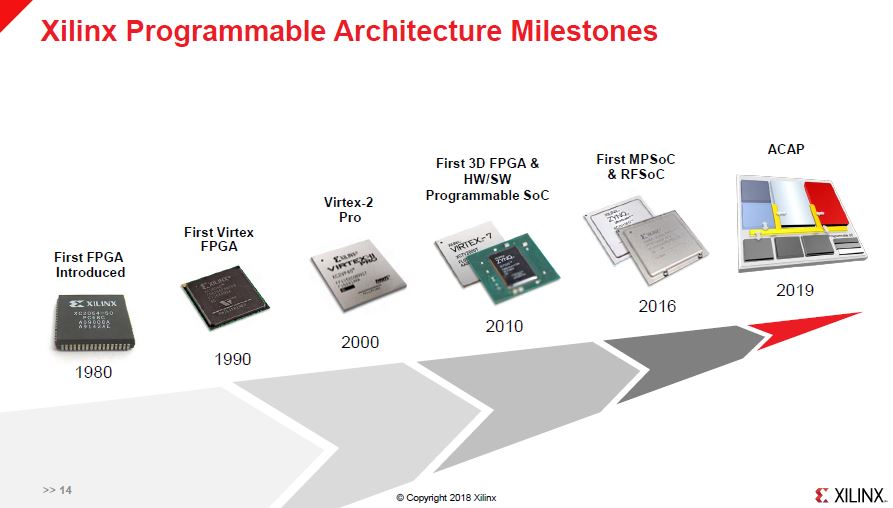

Xilinx ACAP Programmable Architecture Milestones

Now the keynote is following the progression of the FPGA. Current generations have more processors with ZYNQ FPGAs.

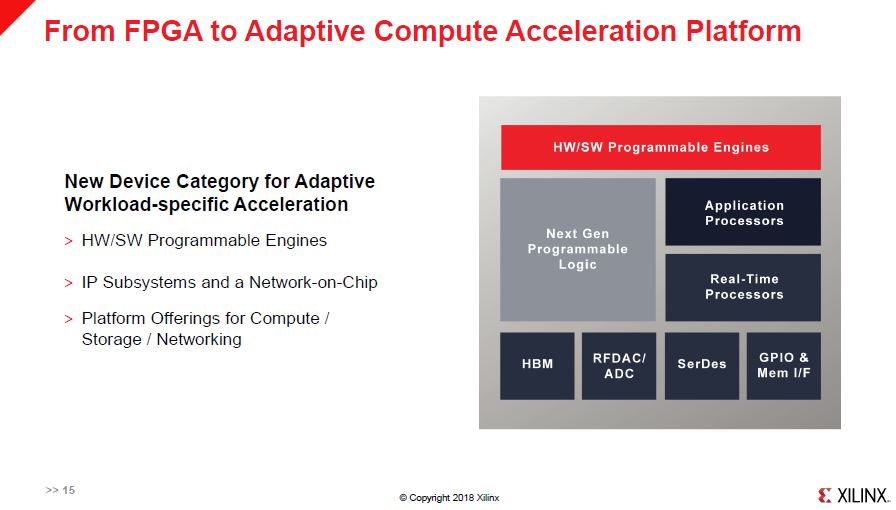

ACAP is the future. Adaptive Compute Acceleration Platform is being released next. We discussed this first in our Xilinx Project Everest and ACAP Strategy at 7nm.

ACAP is a modular architecture. Not every chip will have HBM onboard.

ACAP will be used from automotive to data center. It is not just an FPGA.

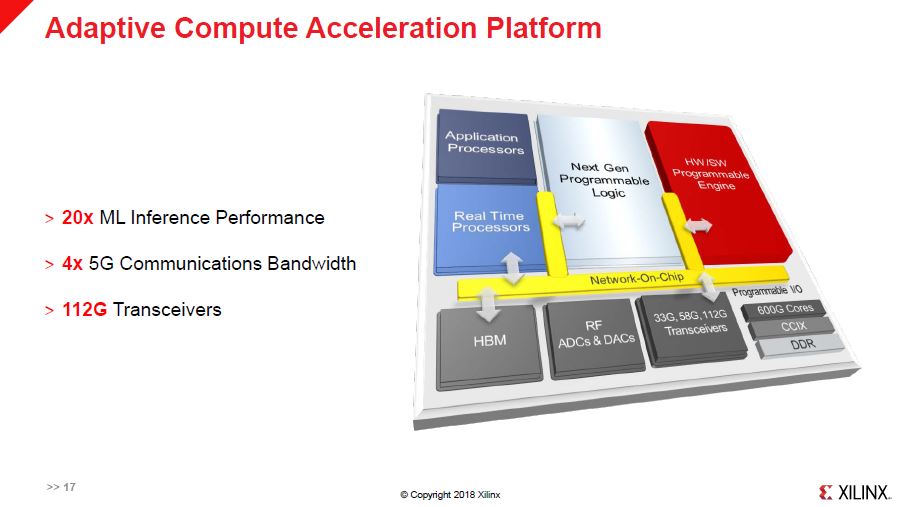

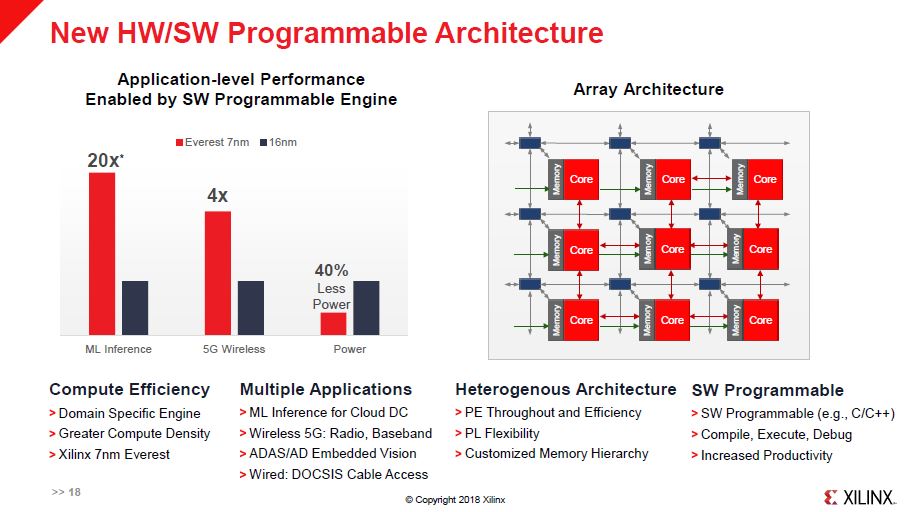

Performance gains generation on generation is significant, up to 20x.

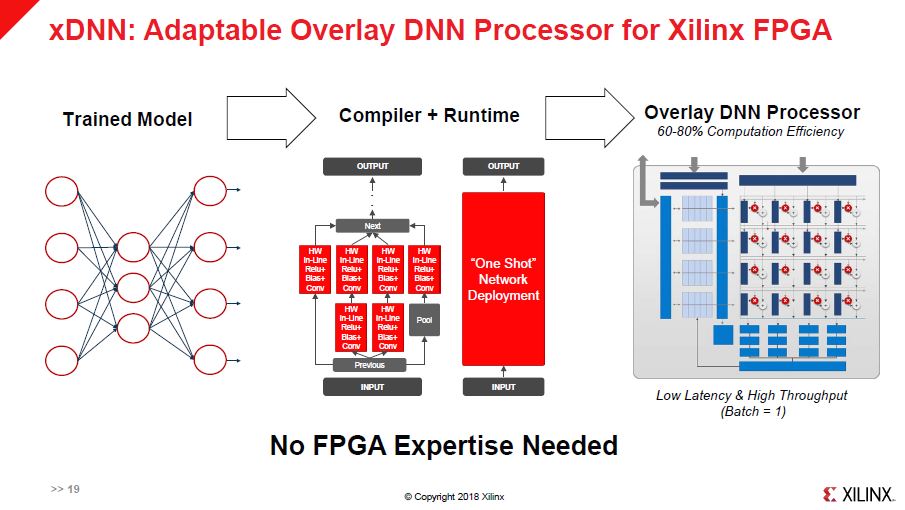

The new tool suite will do the placement and other aspects to leverage hardware so you do not have to be a FPGA programmer to use ACAP. Xilinx is making a major investment in software.

TOPS are becoming the new megahertz wars from the 1990’s. The ACAP is getting performance gains at a few hundred megahertz to a gigahertz. There is a massive amount of on-chip bandwidth.

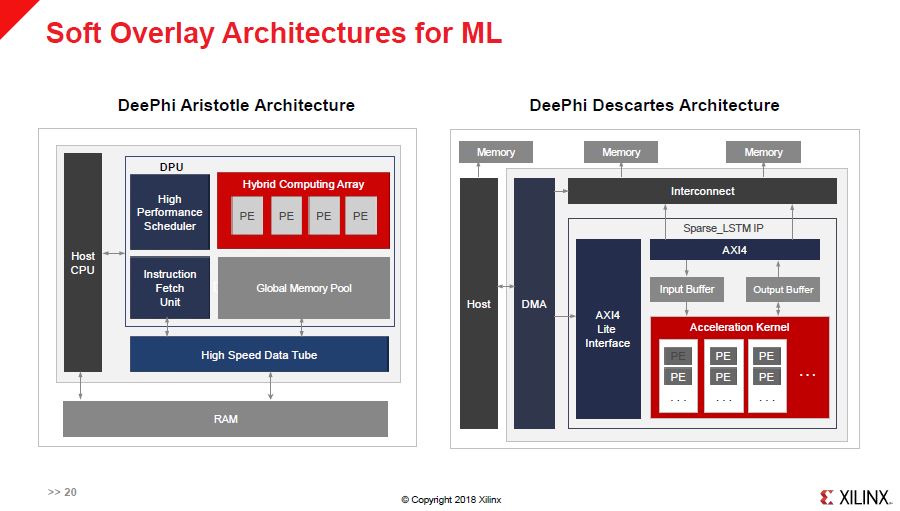

Xilinx recently announced the intent to purchase DeePhi. DeePhi has architectures for machine learning.

Final Words

At STH we will be covering the Xilinx ACAP as it is released. Stay tuned for more information. The company is heading in the right direction here. One of the biggest obstacles to adoption of FPGAs in the AI markets is programming. Building toolsets to allow the benefits of ACAP acceleration without having to know RTL is the right way to address this market.

Long time reader… I’m real excited about all the options coming, especially for EPYC… I do feel that they are overlooking HSA coherency though in APUs… But then AMD could create a DS SoC using Jaguar since it’s SW programmable arch… Then there’s the guts of shaders combined with FMAC FP in EPYC and many levels in between…