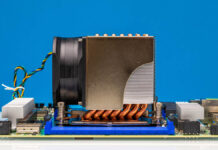

The industry is rapidly racing towards a PCIe Gen5 future in 2022. As such, we are starting to see announcements from a number of companies around PCIe Gen5 and CXL products. Astera Labs has a new line of retimers for the industry. The company is also announcing its EQUINOX product which is a PCIe Gen5 retimer add-in card. While we may not see many retimers in PCIe Gen3 which has been around for almost a decade, as we quickly transition to Gen4, then Gen5, then Gen6, these will become more common.

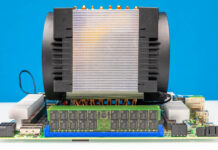

Astera Labs Aries Compute Express Link Retimers

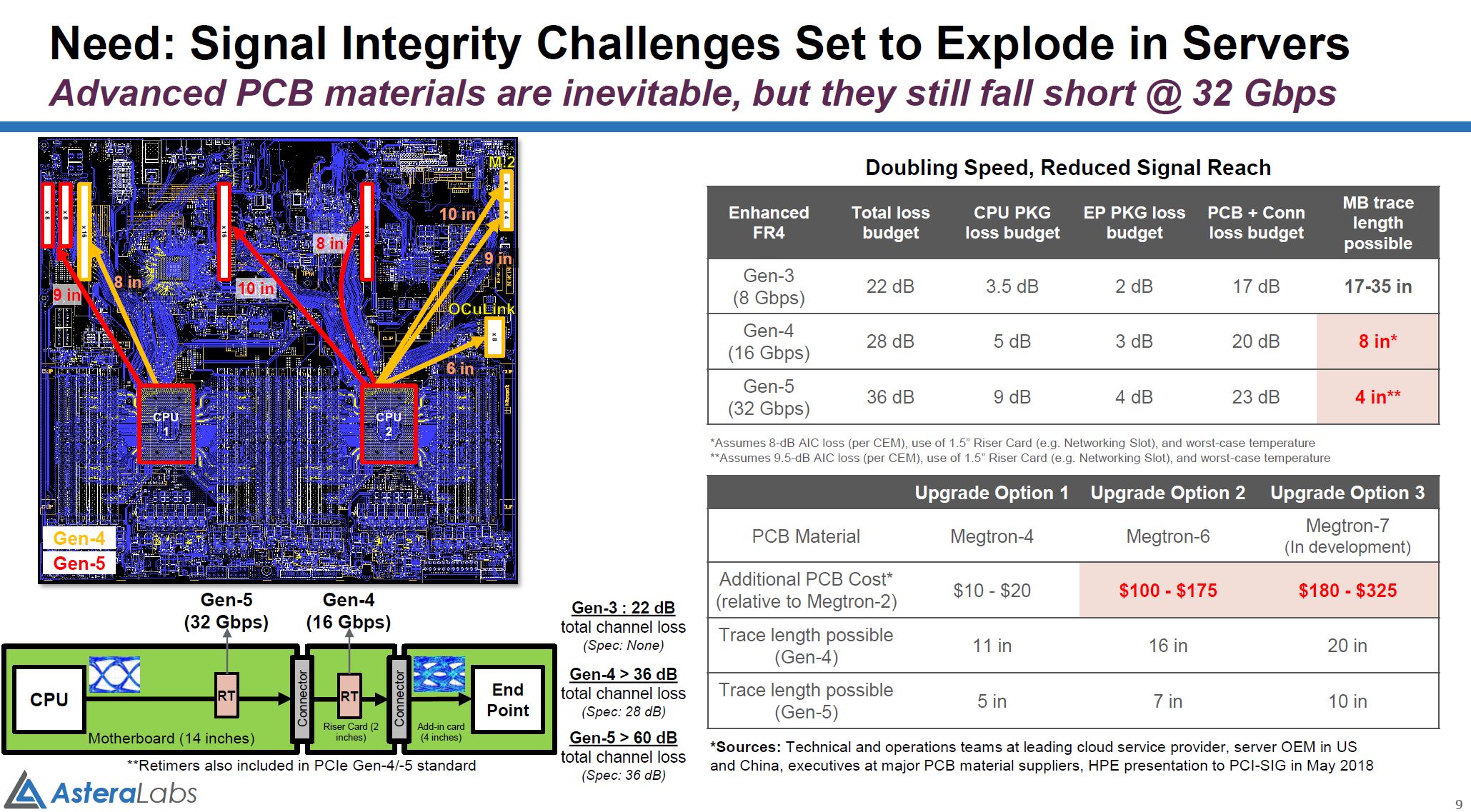

For those who are unaware, retimers are chips inside modern devices that help to extend the reach of I/O. Many are familiar with these inside servers and storage gear as they are often used on long NVMe SSD traces for example. As we move to PCIe Gen4 and Gen5, PCIe signal lengths through PCB start to fall with each generation to where it is no longer useful.

Beyond the PCB trace lengths, adding components such as connectors further shorten the practical reach of traditional straight PCB runs. The key here is that vendors will have to make choices in terms of using better motherboard materials, using more cabling, and/or using retimers and switches.

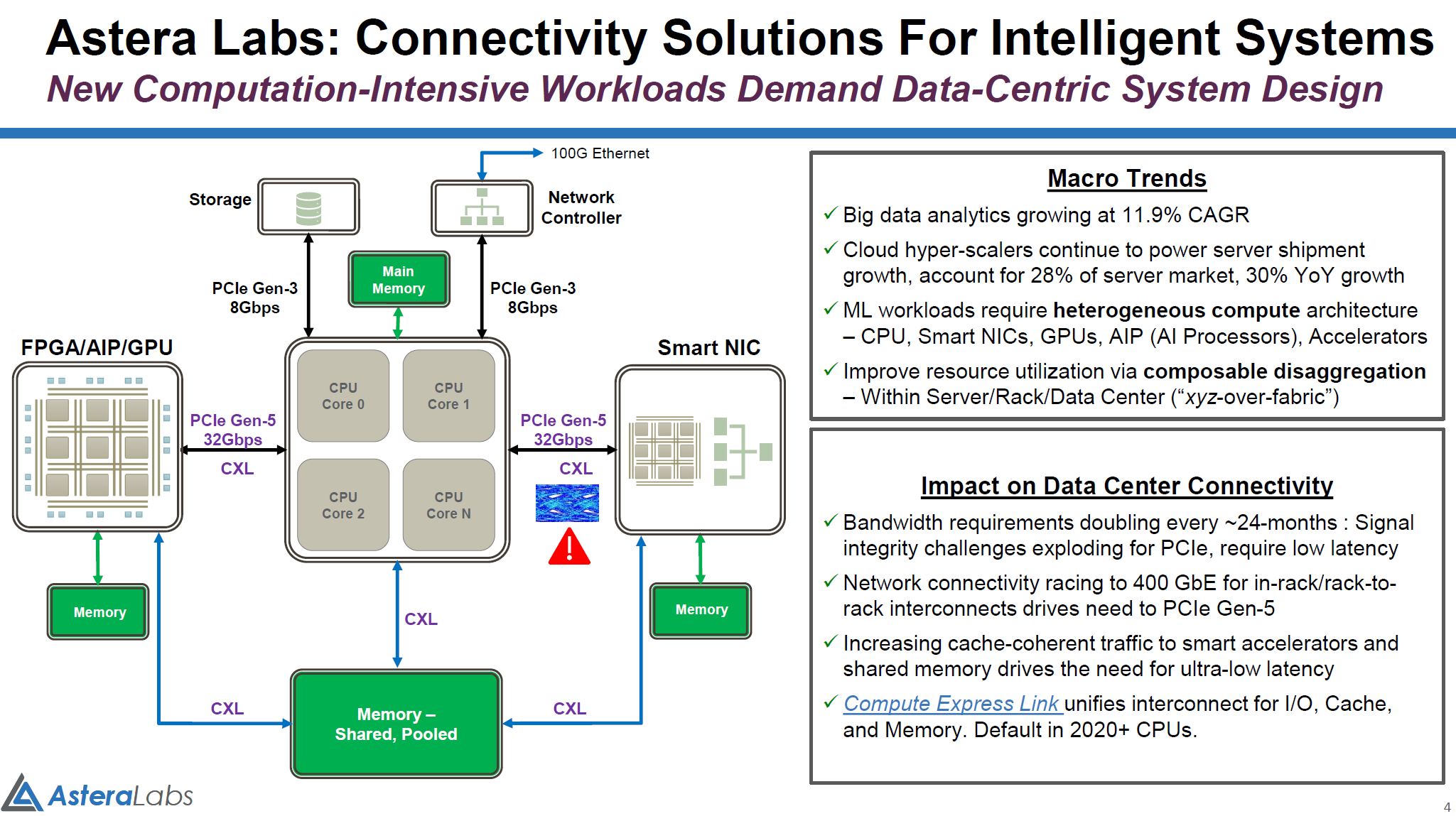

With PCIe Gen5 and CXL, we have the bandwidth to achieve new topologies such as pooling shared memory that can be used across CPUs, GPUs, FPGAs, DPUs, and other components. This is set to offer massive cost savings and will change the way servers are architected.

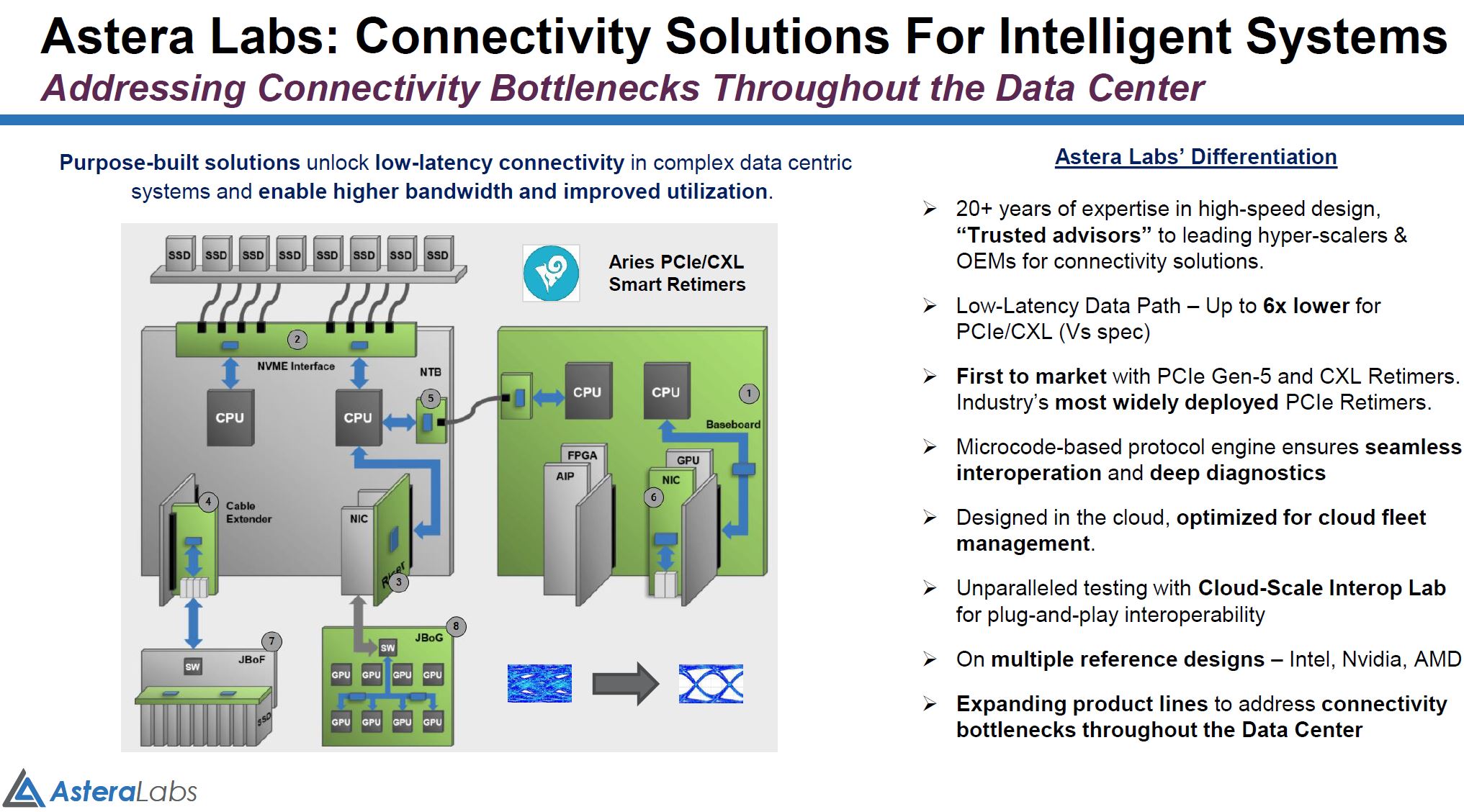

Part of Astera Labs’ solutions is to build low-latency retimers (PT5161LX, PT5081LX) for PCIe Gen5/ CXL. The company is working with Intel’s upcoming Sapphire Rapids chips along with NVIDIA, AMD, and others for next-gen designs. The importance of low-latency for retimers cannot be understated, especially when there can be multiple retimers in the path. The CXL spec is relatively loose, so we are seeing Astera Labs and companies like Microchip announce they are working on tighter timings with Intel.

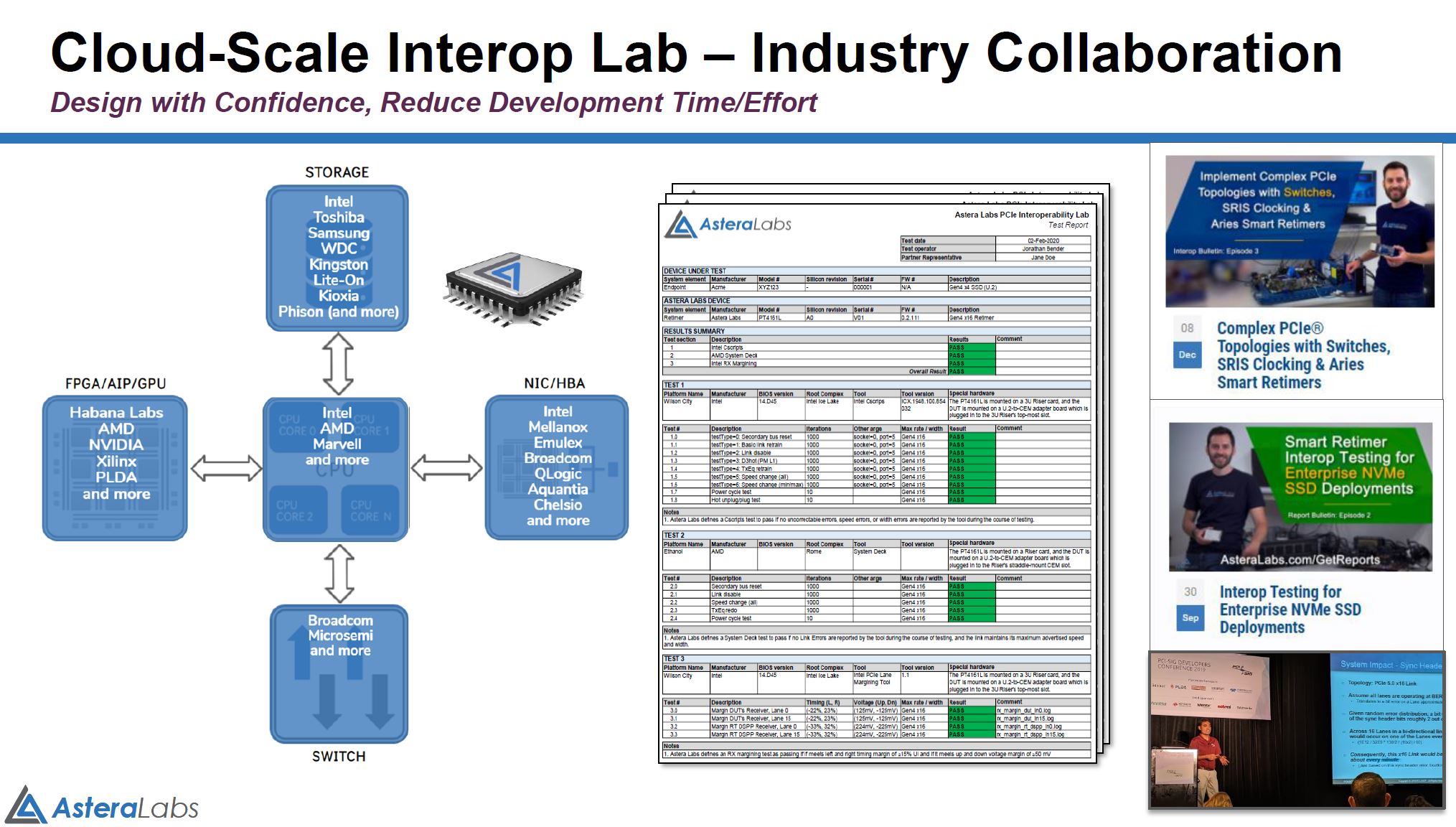

The company also has its own interoperability lab where it is working with a number of partners to ensure solid bring-up of next Gen PCIe Gen5/ CXL devices. As we move from the aging PCIe Gen3 to more rapid development cycles, this is going to be more important to ensure products come to market quickly.

Part of Astera Labs’ differentiation is that it has a built-in controller so it can feed telemetry data to cloud providers’ systems to ensure that links are working properly. The company says it can even fix some potential problems via firmware updates because it has a controller built-in.

Final Words

Overall, this may seem like a small step, but next-gen systems (or next-next-gen given where we are in the cycle) will use more retimers than we saw with PCIe Gen5. Systems will continue to get bigger and more complex which means solutions to basic problems such as trace lengths will become more pronounced.

At the same time, it is hard to come away here feeling like this is the end-game for Astera Labs. The entire CXL ecosystem will need more infrastructure such as switches, memory controllers, and more that will benefit from providing the end-to-end link solution.

Is there a sense yet of how tightly coupled CXL retimers, switches, etc. will be with other components?

Obviously the ones soldered onto the motherboard to support some in-chassis cabling arrangement or similar aren’t even going to really raise interoperability questions; they are just board components; but for things like add-in cards and interconnects between devices are we looking at a situation more like Ethernet, where there’s some SFP-locking and proprietary extensions here and there but for the most part you can connect just about anything to anything and have it work; or is this going to be a much less robustly standardized, very much consult-your-vendor’s-list-of-validated-options, sort of situation?

I found this a very interesting article. Do bus retimers that send telemetry data to cloud providers sound like a good idea to everyone? Maybe the day when a single security failure in the cloud shuts down every computer in operation will dawn sooner than expected.

Overall, this may seem like a small step, but next-gen systems (or next-next-gen given where we are in the cycle) will use more retimers than we saw with PCIe Gen5.

Think you mean PCIe Gen4?