At CES 2023, AMD announced the new AMD Ryzen 7000X3D series. This is the next generation of the AMD Ryzen 7 5800X3D with 3D V-Cache. AMD is releasing not just one but three new SKUs with this generation. As a direct result of these parts, we can extrapolate a reasonable L3 cache guess for the upcoming AMD Genoa-X.

AMD Ryzen 7950X3D Launch

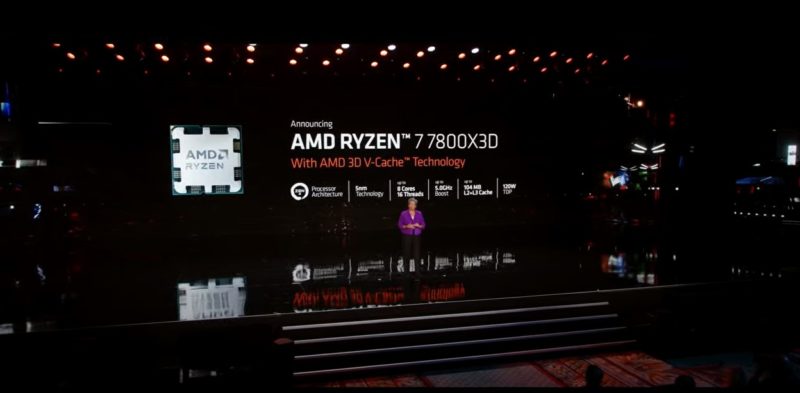

The first CPU that AMD announced was the AMD Ryzen 7 7800X3D. This is the new 8-core 3D V-Cache part that is the direct successor the the Ryzen 7 5800X3D.

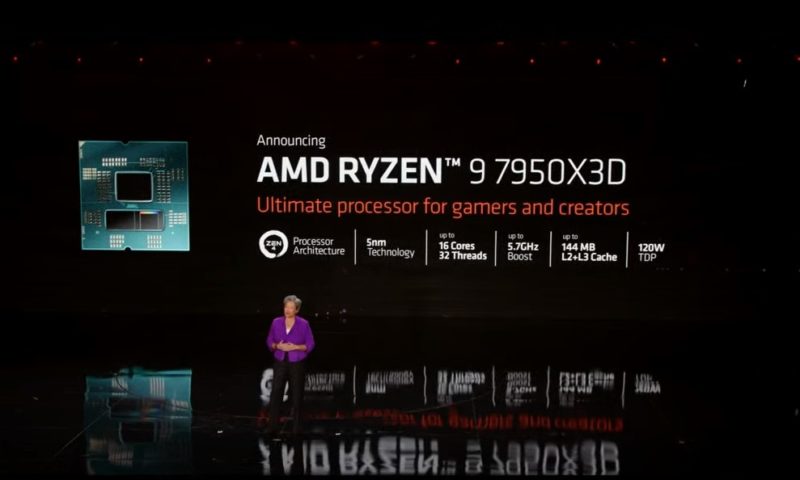

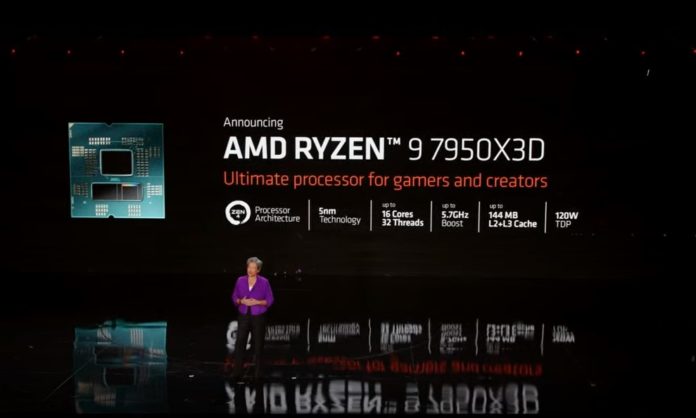

Next, the company announced the AMD Ryzen 9 7950X3D. This is not just an 8-core part, but instead is a 16-core/32-thread part with up to a 5.7GHz boost and 128MB of L3 cache.

AMD has 8, 12, and 16-core 3D V-Cache enabled variants. The 12-core model will be the AMD Ryzen 9 7900X3D. It is great to see that we are getting higher core count parts with the 3D V-Cache so we do not have to choose between cores and cache. Still, it seems like we are getting less cache per-CCD on the 12 and 16-core chips.

The company said the new chips will be available in February 2023 but did not provide pricing.

Final Words and AMD Genoa-X Implications

To us, the 3D V-Cache parts are the most interesting of the Ryzen 7000 series lineup. There are so many applications that are actually memory bandwidth sensitive that these chips with massive caches are very exciting.

So what does this all mean for the server side? AMD Milan-X tripled the L3 cache over standard AMD EPYC 7003 Milan parts, adding 64MB of L3 cache per CCD. That gave us 8 CCDs x (32MB + 64MB per CCD) = 768MB L3 cache per Milan-X part. The AMD Ryzen 7800X3D seems to follow this same trend of adding 64MB of L3 cache per CCD. For AMD EPYC Genoa with up to 12 CCDs, that would give us 12 CCDs x (32MB + 64MB per CCD) = 1152MB of L3 cache. That means Genoa-X is slated to be a GB of cache CPU, joining the Intel Xeon Max series as GB-era CPUs.

Special Mention

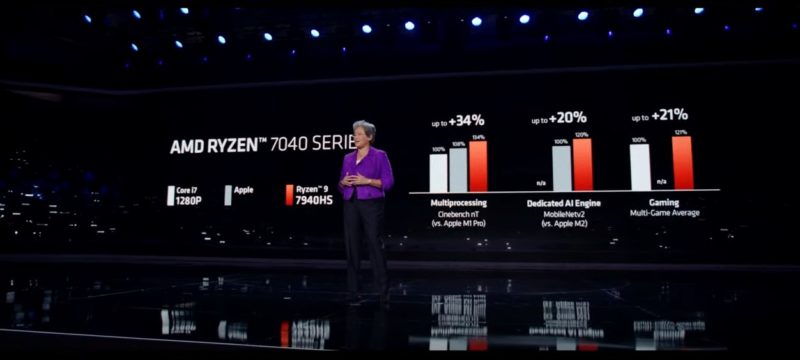

One other really interesting bit from the AMD keynote is that they are embedding Xilinx-derived XDNA AI accelerators in the company’s new mobile parts:

That new feature means that AMD is showing AI comparisons between its newest Ryzen 7040 series of mobile CPUs and the Apple M1/M2 silicon. Whereas Intel is pushing features like VNNI, AMX, and etc. as on-core accelerators, AMD seems to be looking more towards dedicated acceleration blocks like Apple.

AMD is extending XDNA to the new AMD Alveo V70 as a PCIe card AI accelerator to go after markets that GPUs like the NVIDIA T4 target. We are starting to see AMD’s AI strategy take shape.

Is it clear whether on the 12-/16-Core models there is one cache die per CCD or only one 64MB die for a single CCD?

♂️ There isn’t less cache per CCD on the Ryzen 9 parts. Only one of the CCD’s has the 3D V Cache. The other is just a standard Zen 4 CCD optimized instead for peak clock-speeds (something the X3D CCD’s really struggle with).

This lets AMD basically have their cake and eat it too in a single CPU assuming their scheduler optimizations with Microsoft work as promised. Cache & memory sensitive workloads (like gaming) go to the V Cache laden CCD while compute sensitive ones go to the higher clocking vanilla one.

I do wish AMD offered a desktop part with 192 MB total of L3 cache (32 MB + 64 MB v cache = 96 MB per CCD) even if clock speeds had to be throttled back a bit. The non-v cache parts turbo north of 5.5 Ghz which I presume a hypothetical 192 MB model would land between 5.0 Ghz and 5.5 Ghz which is still rather high on the desktop.

I do wonder if the v-cache dies are the same between Zen 3 and Zen 4. That is one of the cornerstones of AMD’s chiplet philosophy: reusing dies between product designs for quicker deployment and leveraging economies of scale.

The announcement of a Xilinx AI block was something hinted at before. Personally I’m hoping for various Epyc chips with full fledged on package FPGA or having FPGAs added to the Instinct line in-package. The flexibility in workload acceleration seems to be worth it in die space vs. hard ASIC-like accelerators for a more general use case.

I am so happy to see apple pushing the big boys into better worlds. At the sometime so happy to see green boy going after apple.

Apple was not first with any of the things You think they where, neither APU, or fast cjiplet interconnect or integrated coherent memory between CPU and GPU (its been in the PS and XBOX for years before Apple.

Think it would be interesting to see dedicated AI, FPGA and other accelerator chiplets on a Genoa CPU package, maybe replacing some CCDs….