This is one we are a bit skeptical about, but here it is. The latest claim by Intel is that its new 10nm SuperFin Agilex FPGAs are twice as good as Xilinx Versal ACAPs. For those who are not into the FGPA space, Intel Agilex is the latest FPGA design from Intel’s Programmable Solutions Group based on its leading 10nm SuperFin process. Xilinx’s Versal lines are the company’s new FPGA’s but dubbed ACAP to reflect new acceleration IP. Xilinx Versal uses TSMC 7nm. Intel is making some fairly bold claims about its new parts. We have links to where you can learn more in this paragraph.

Intel Claims Agilex FPGAs are Twice as Good as Xilinx Versal

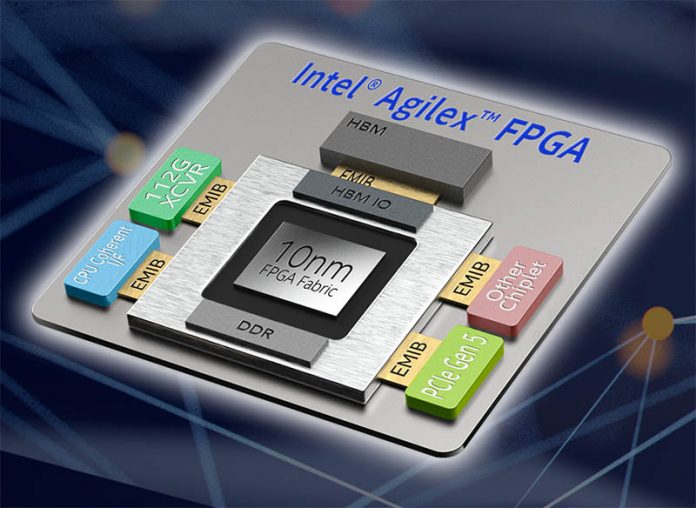

The brief notes are that the Intel Agilex FPGAs are built upon the 10nm SuperFin process which is a refined 10nm process and is shipping to customers. We previously covered that Intel Agilex Next-Gen FPGAs Shipping to Microsoft and Others.

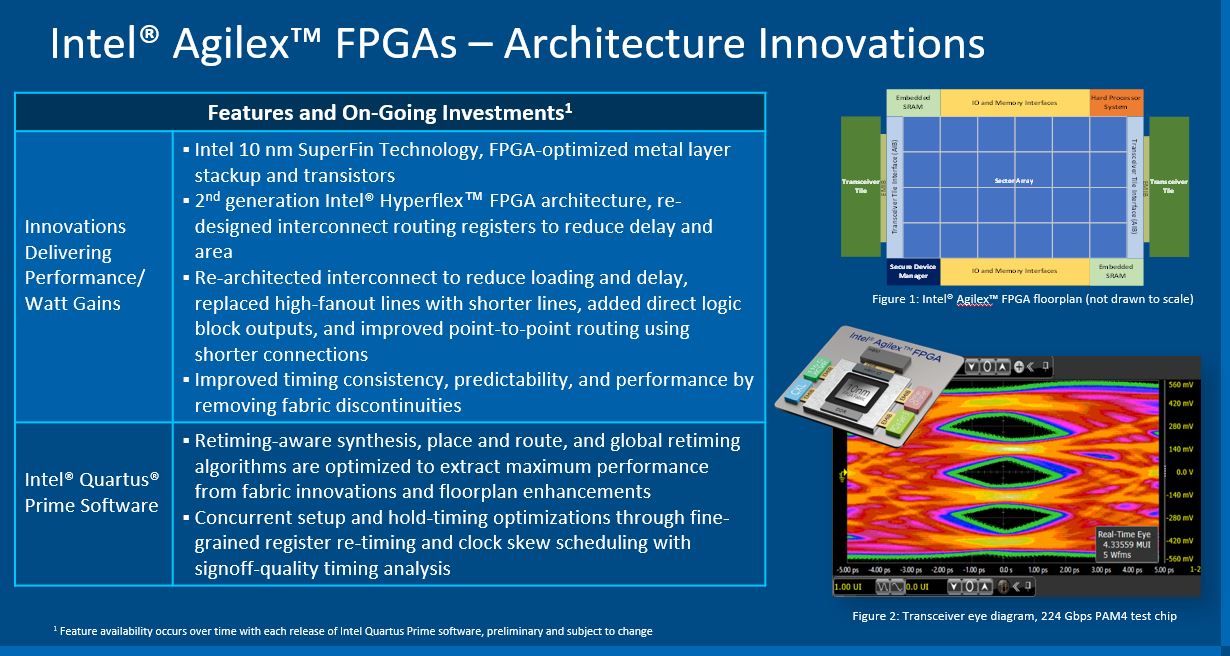

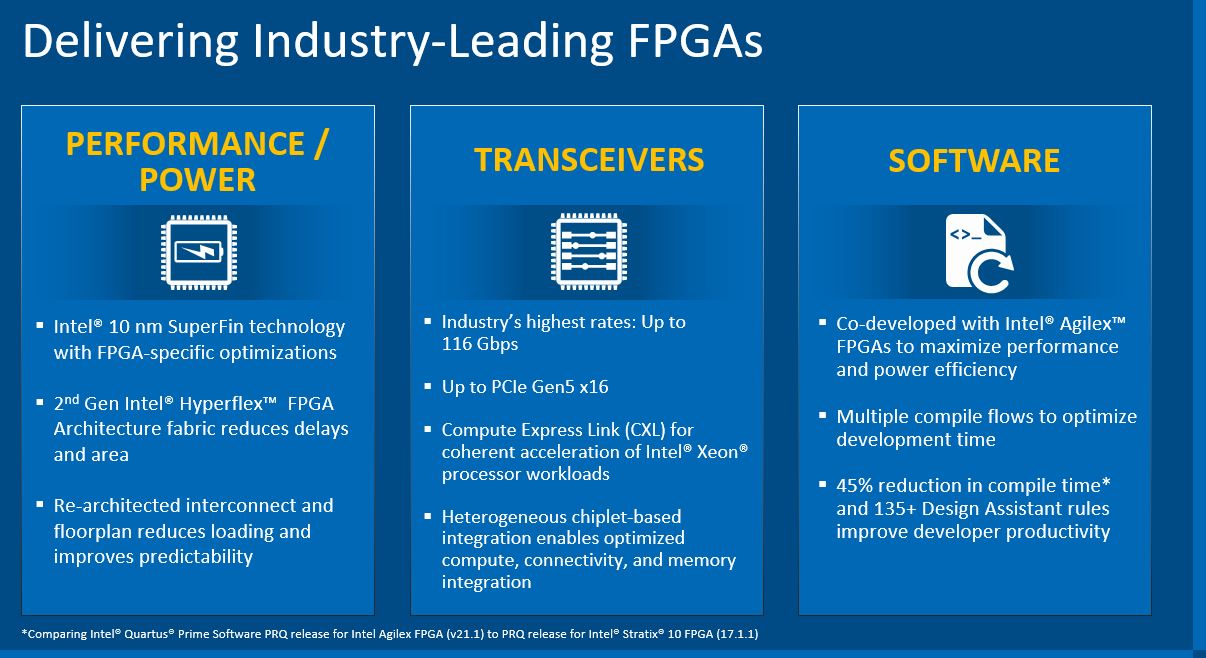

We are going to get to that ~2x claim later. Intel has a new architecture for Agilex which includes items like its 116G transceivers. It is also showing off the eye diagram for its 224G PAM4 test chip.

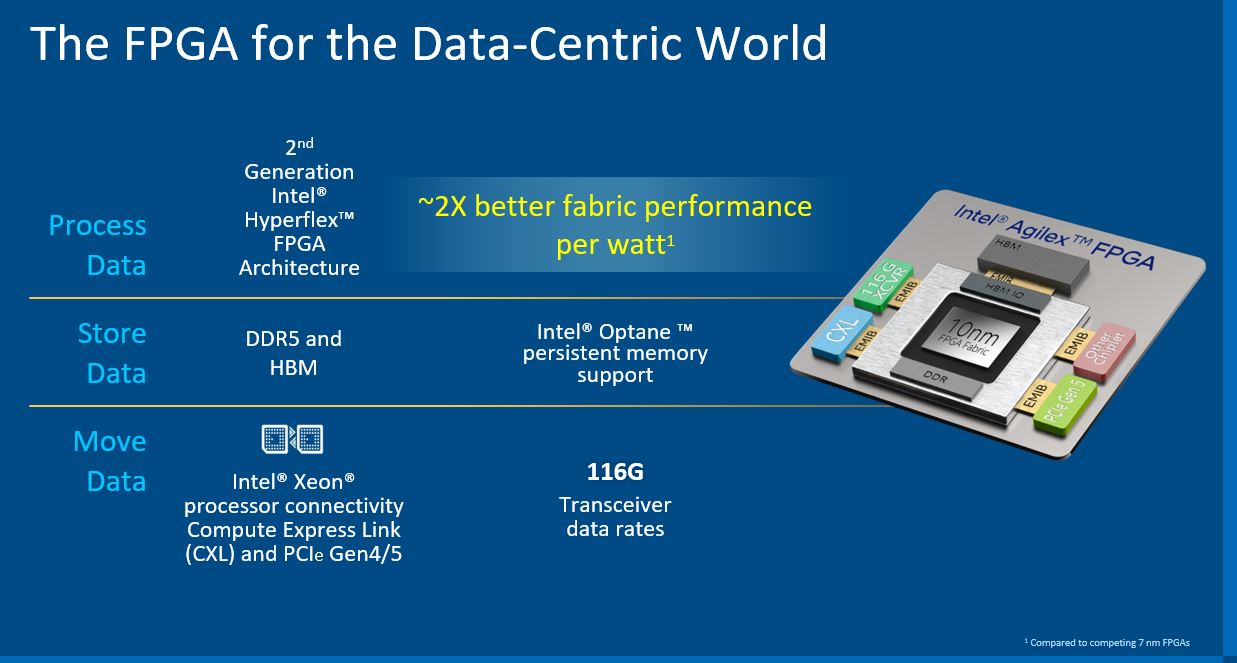

A major feature for FPGAs is connectivity both in the on-chip Hyperflex FGPA fabric as well as the interconnects. Intel also has tiles for memory controllers, PCIe Gen5, CXL, as well as its ability to use eASIC to created hardened chiplets to connect to the FPGA via EMIB to increase efficiency.

Key features include DDR5, HBM, Optane memory support (we showed the Stratix version here), PCIe Gen5/ CXL, and 116G transceivers.

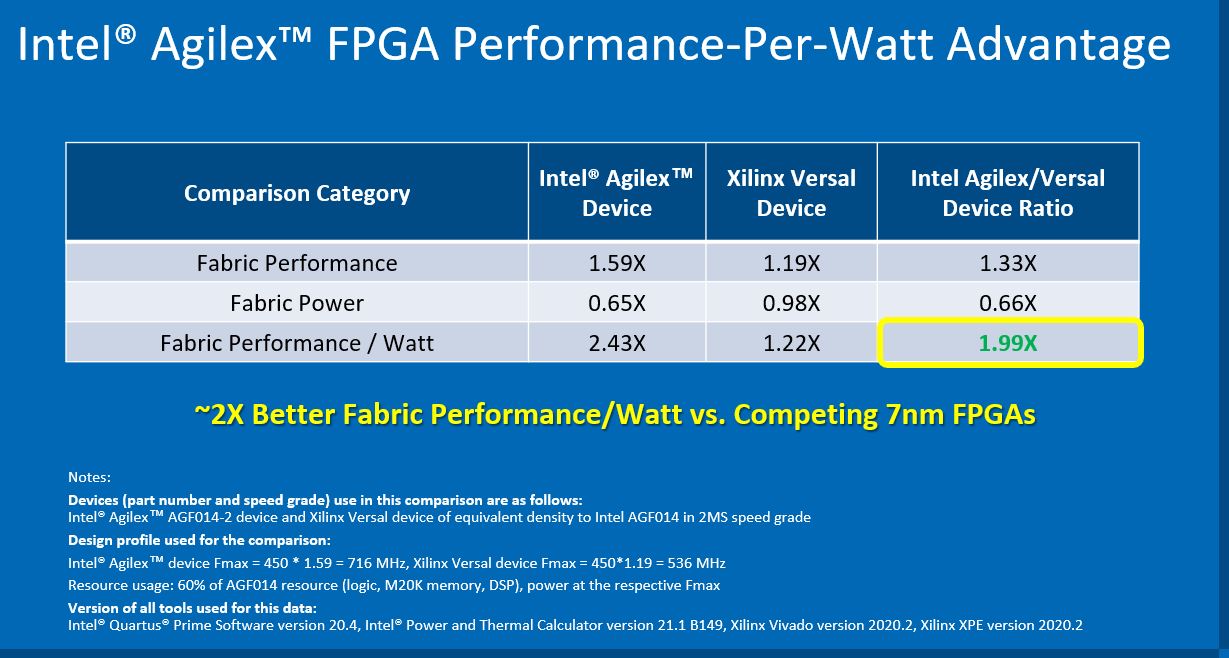

Here is the breakdown of the ~2x performance per watt advantage for Agilex over Versal.

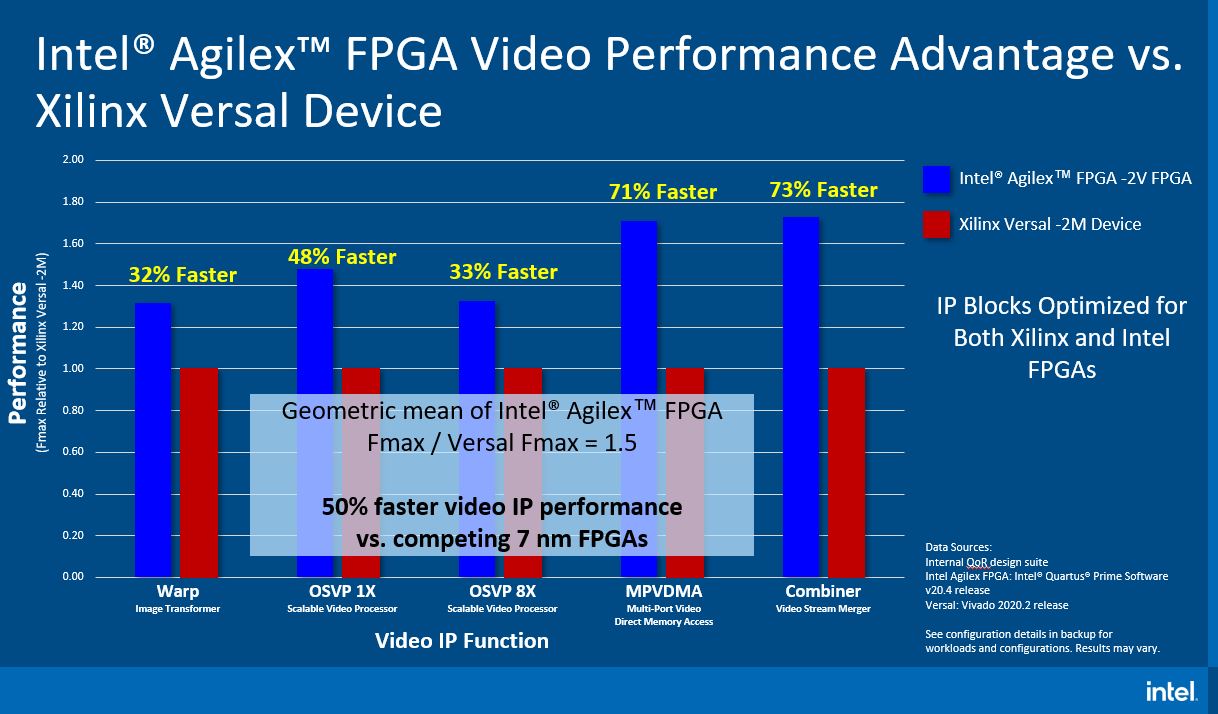

On the performance side, Intel is highlighting a number of video performance aspects. Note that these are specifically video functions.

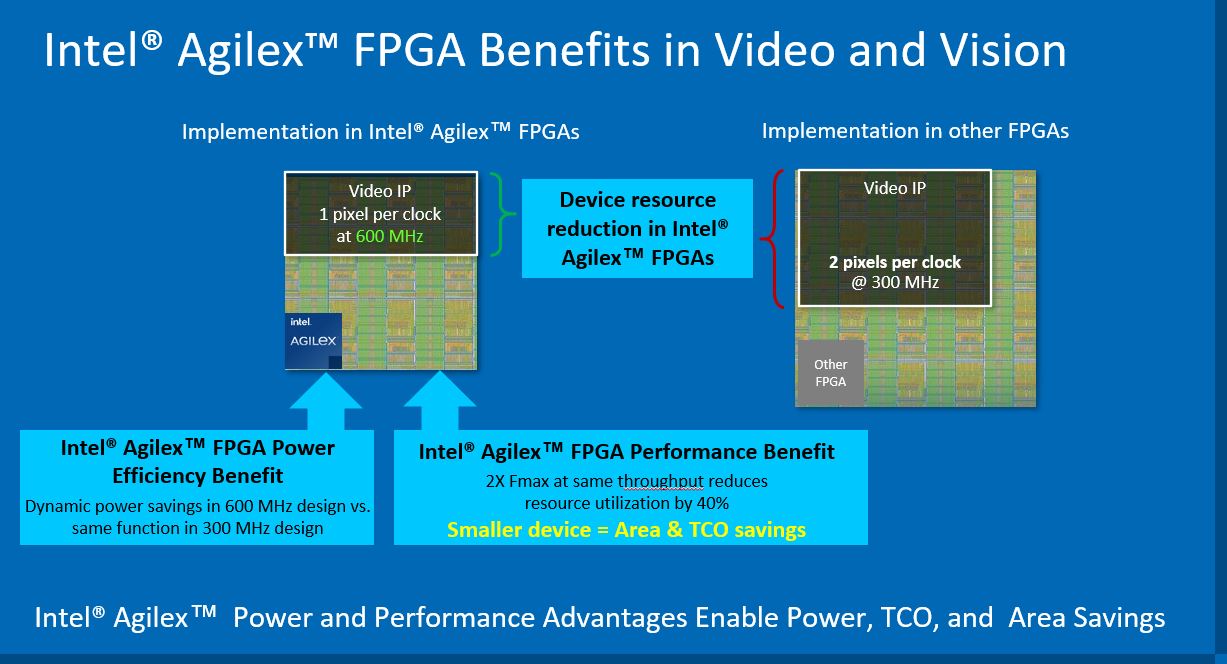

Here is another backup slide for its video and vision function performance/ efficiency.

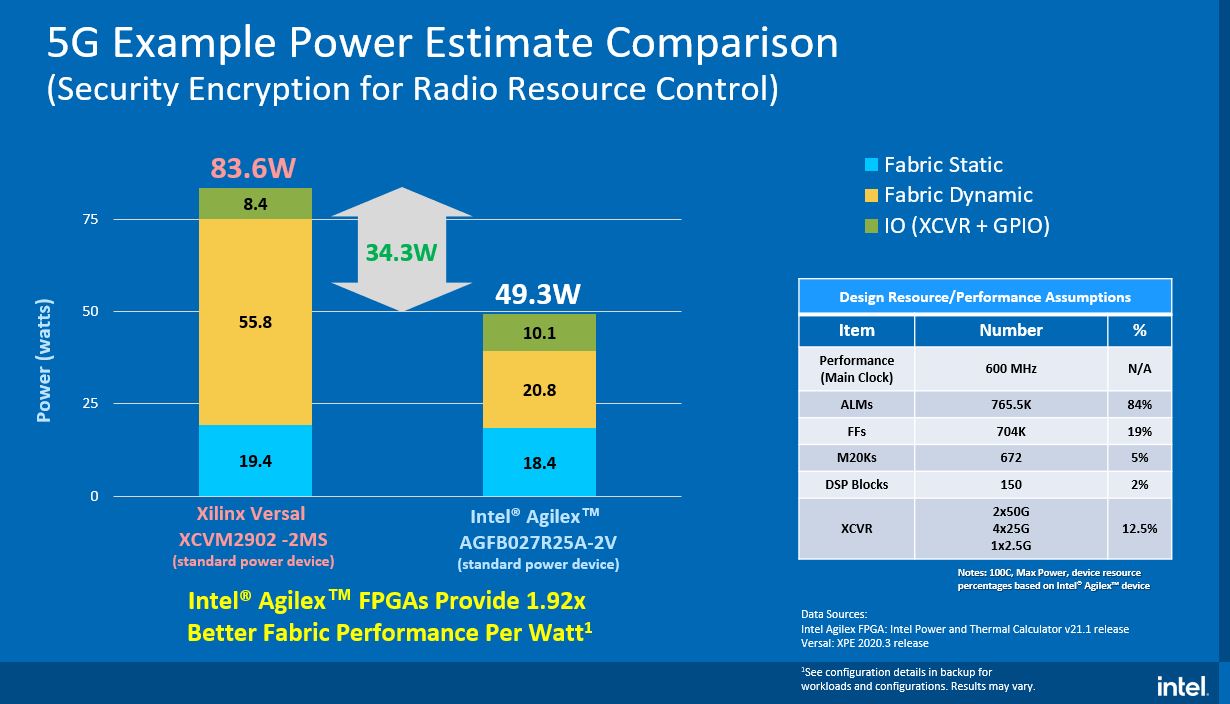

Here is Intel’s example of getting 1.92x better performance per watt for 5G.

One can see the big delta is in the Fabric Dynamic category where intel has a much lower power draw.

Final Words

I asked Patrick our Editor-in-Chief about this. A 2x improvement in power efficiency is a huge margin, especially on edge devices. He said he asked Deepali Trehan, who is a Vice President in Intel’s Programmable Solutions Group, about this. Specifically, he asked why anyone would buy a Xilinx Versal product if Intel Agilex offers 2x the performance per watt. The context was that Xilinx has a huge market share in FPGAs so one would expect Xilinx would be smaller if it offered half the performance per watt. We did not get a definitive answer, but we are a bit skeptical just based on the market share and scale of the delta. We will let our readers decide for themselves, but this seems to be a very narrow and specific claim that is being highlighted.

When a chart lists relative performance for two devices and does not normalize the scores to one device I get suspicious. I suspect some lawyer advised that it’s not lying especially if it is unclear what is being compared. Perhaps somewhere there is another company making 7nm FPGA’s?

@emerth, that’s a great point and it’s a bit sad that the FPGA world has been so dominated by Altera/Xilinx for so long that a 3rd player wouldn’t enter my mind. But there are many other players.

So who might the rival be? Lattice? MicroChip? Achronix? Netronome? Maybe NVidia has a stealth product coming?

@emerth

Achronix?

If it is an alternative fact, it’s true.

Or may be it’s a typo and they meant LPGA.

Or it’s about INTEL’s Altera vs. AMD’s Xilinx. Duh :-)

This has indeed to be taken with a Titanic’s Iceberg-size grain of salt.

A few months ago INTEL attacked AMD on its laptop mobile CPU 5000 series by saying that its 10nm mobile CPU leave AMD in the dust when running on battery, with all the tables and graphs to “prove” it. The reality is more mundane, when the laptop is powered from the wall, AMD 5000 series massacres whatever INTEL has, it’s painful to watch.

So INTEL came up with the battery only tests. INTEL time limited boost (staying on) gives the advantage to INTEL. When AMD 5000 series is on battery it throttles down the CPU in order to save the battery. So the AMD 5000 series is behind but not by much in comparison to the bloody slaughter when powered from the wall.

Last but not least, with the AMD 5000 series, your battery will last longer.

It’s just practicing the illusion of truth, but hey, it’s a “victory” for INTEL.

The “2x the performance per watt” for FPGA comparison sounds as fishy as this mobile story which has been deconstructed by many.

I’m sure INTEL will come up with something for its Xeon Scalable. If you use a Xeon at a latitude greater then 75 degree, with a Southern wind of 40 mph, seating on a chair whose legs are no longer than 20″ while facing the Mecca, then Xeon no-op is faster than any Epyc Milan.

INTEL marketing is as believable as the now historical Bagdad Bob a.k.a. Comical Ali.

@William Barath

I see Lattice FPGAs in a few embedded products but I haven’t spotted them in any enterprise grade IT box.

The main reason why Altera and Xilinx are so common place in those sectors is that they’re the ones on the cutting edge with genuinely massive FPGA and high end transceivers. Both of these companies are eyeing chiplets in some fashion to scale up to even more programmable logic and exotic transceivers while simultaneously using the most cutting edge process nodes for further density.

Other companies would require massive investments to scale into just those areas. Things get more complex as both Altera and Xilinx have been absorbed by Intel and AMD respectively as the market is shifting toward more hybrid solutions with bits of hard logic that can be provided by chiplets. The Intel and AMD side can provide not just top of the line CPU performance but graphics cores, high speed memory controllers, PCIe controllers, Ethernet, USB etc. The future is clearly going into these mixed directions in a customized fashion which would require another significant investment.

There are only a few who could challenge these two FPGA makers where the market is going (not where it is now): nVidia, Broadcom, Samsung, and MediaTek which all would have to vastly improve in a segment to become competitive with the plans the two giants have laid out.

It looks like Intel is being very specific about 2x “fabric” performance per watt.

This makes me wonder if they are using their Foveros packaging techniques to assemble these things; and trumpeting the gains realized there as industry-leading; implying but not actually stating that the entire part is OMG 2x better.

If memory serves they’ve previously stated that their multi-chip packaging tech has a lower energy cost per bit than competing options(it just hasn’t helped them too much since they picked up the cool packaging tech while virtually all of their CPU offerings were monolithic; minus some cool tech demo parts of limited real world appeal); so it wouldn’t be a huge surprise if they are exploiting that to tie together the FPGA and support chips and trumpeting the gains there. Probably not outright false; but also probably why they are hammering on ‘fabric’ gains; rather than on-die competitiveness.

There’s more to it than comparing one feature to another and the power requirements for that, on one device versus another; there’s a complicated chain of pros versus cons, and no universal answer to every problem:

https://www.eejournal.com/article/high-end-fpga-showdown-part-3/

https://www.eejournal.com/article/intels-worlds-largest-fpga/

https://www.anandtech.com/show/16001/hot-chips-2020-live-blog-intel-10nm-agilex-fpgas-830am-pt

https://www.anandtech.com/show/16002/hot-chips-2020-live-blog-xilinx-versal-acaps-900am-pt

It’s a question of what you want to do, how you’ll try to do it, how fast does it need to be, size, power, cost, implementation details, and if flexibility is required in which directions can you go.

Much like comparing one CPU (or GPU) architecture to another, and simply declaring that it’s fabric and power requirements are better; so that makes it preferable to others, that’s not universally applicable.

Cliff, this is an extremely strange article, full of logical errors. I don’t understand what the heck happened here, but this is bad.

1. You claim that Intel claimed that their new FPGAs were “twice as good” as the Xilinx parts. Twice as good? I don’t know what that means for a chip, and no one in the industry talks like that. Intel definitely did not say twice as good, and I don’t think I’ve ever read a technology news article using “x as good” as the metric. This becomes important again later in the piece.

2. You never explain or report what the 2x figure is, what it’s based on. That’s incredible given that it’s touted in your headline, and you repeatedly mention 2x, 2x, 2x… throughout the article.

The key issue here comes to light in the slide you posted, titled “Intel Agilex FPGA Performance-Per-Watt Advantage”. It seems like you didn’t look at the slide since you never talk about what it means. The slide gives performance improvement over some baseline for both the Intel and Xilinx chips. Notice that the Xilinx chips are not the reference, since their column has >1x in most cells. Both the Intel and Xilinx chips show >1x over some baseline.

The problem is that we don’t know what the baseline is, what they’re comparing these chips to. You never tell us. It’s not in the slide. There’s no explanation anywhere in this article of what exactly the central metric of the article is based on… It’s like you didn’t even read the slides or think through what you were writing about.

3. Your concluding paragraph casts doubt on Intel’s claims because… Xilinx has more market share. This is incredibly strange. This is a new product. Market share at time t is based on the performance of **past** products (assuming it’s a simple function of product performance, as you suggested, which we have lots of reasons to doubt).

You and Patrick got tripped up on the idea that if Intel’s FPGAs were this “good” compared to Xilinx, Xilinx would be smaller and Intel would have more share. You made the mistake of temporal shifting, where you think the past is defined or influenced by the present or future. And you injected a belief that market share is a simple function of performance, such that:

1. During some unspecified past period running up to the present, Xilinx had better performing chips than Intel/Altera.

2. During that same period Xilinx garnered more market share mostly because of its performance advantage.

3. Therefore, Intel’s new FPGAs can’t be 2x better than Xilinx counterparts on some unspecified comparison metric.

That makes no sense whatsoever. Point 3 is a non sequitur.

Note also that we have no idea what the 2x is based on, since you never told us. So this whole discussion is based on an unknown metric, which makes all this even more frustrating. This was a thoroughly strange article and shouldn’t have been published. It seems like you didn’t read the slides, or pay attention to the core details, and you (and Patrick) made bizarre logical errors. This was pretty bad.