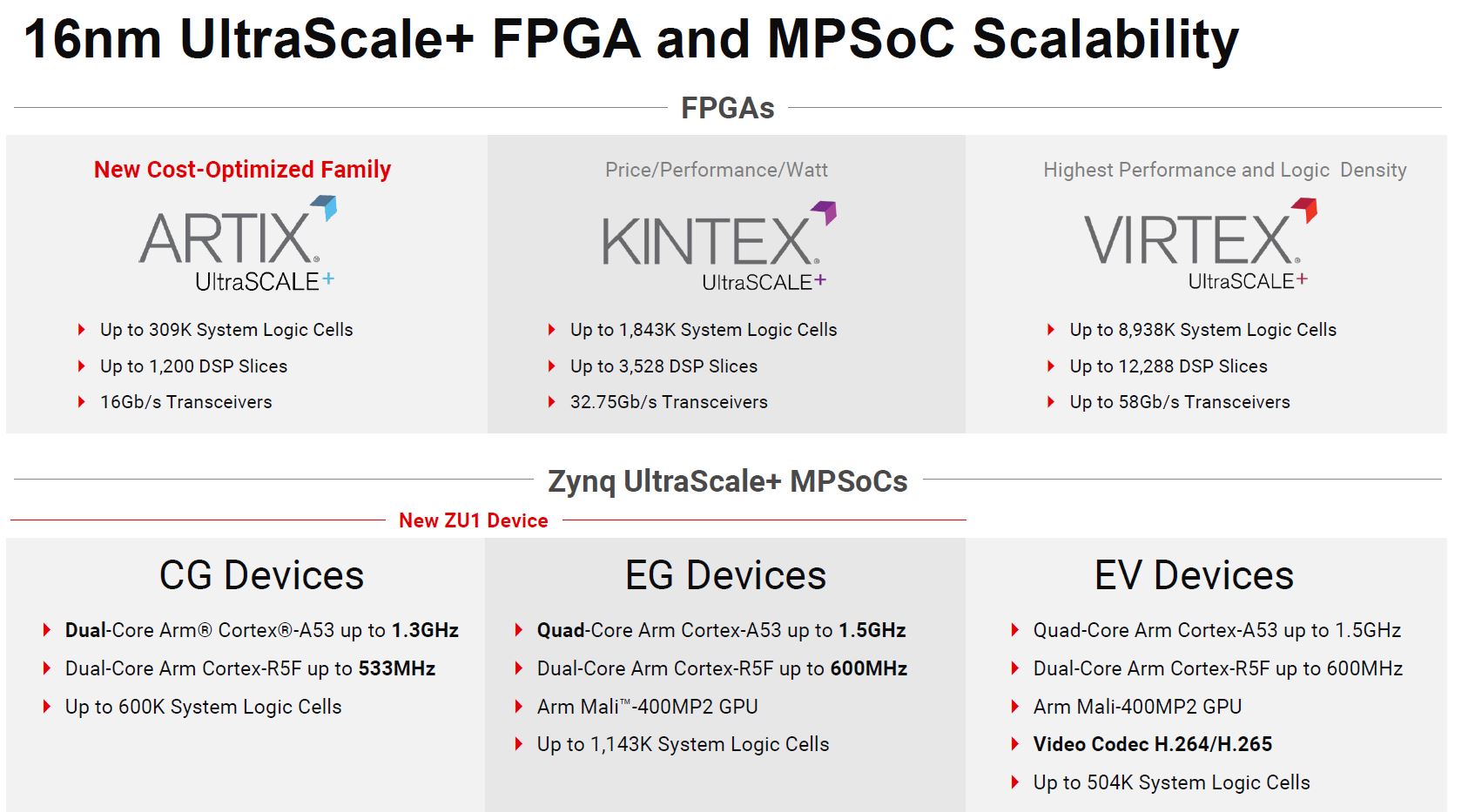

If you make FPGAs, one way to expand your share and get further into the market is to launch a new COP, or a cost-optimized portfolio. That is what Xilinx is doing with a TSMC 16nm Zynq and Artix UltraScale+ line that brings more performance, lower power, and smaller packaging to the cost-optimized market.

Xilinx Zynq and Artix UltraScale+ COP

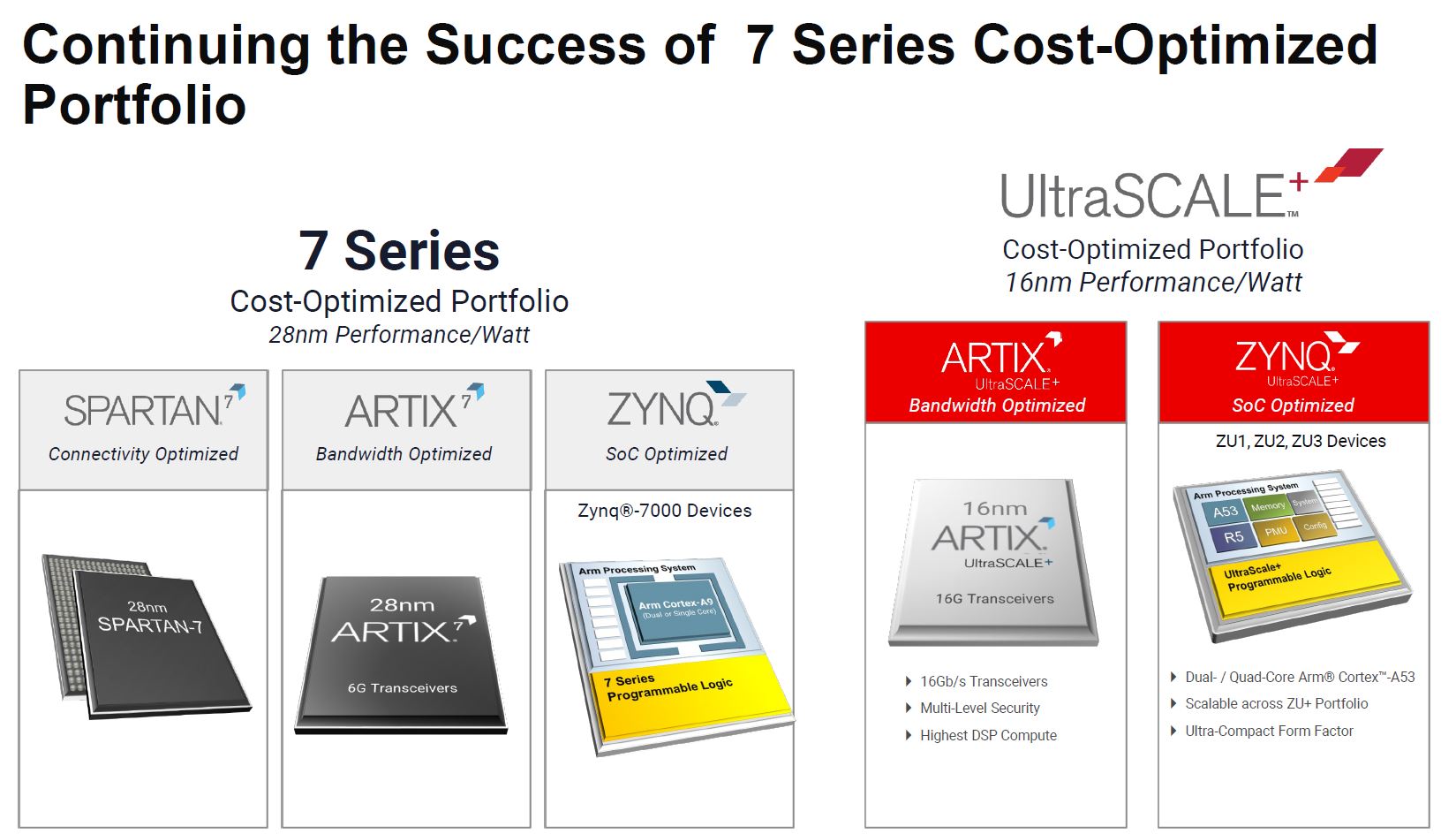

Today Xilinx has the new Zynq and Artix UltraScale+ portfolios which are 16nm UltraScale+ parts (not the new Xilinx Versal ACAPs) but are designed for cost and low-power applications.

As one may imagine, being the largest FPGA player, Xilinx has had low-cost devices before, but it now has an update to the Artix 7 and Zynq 7000 series.

We are going to quickly cover both offerings.

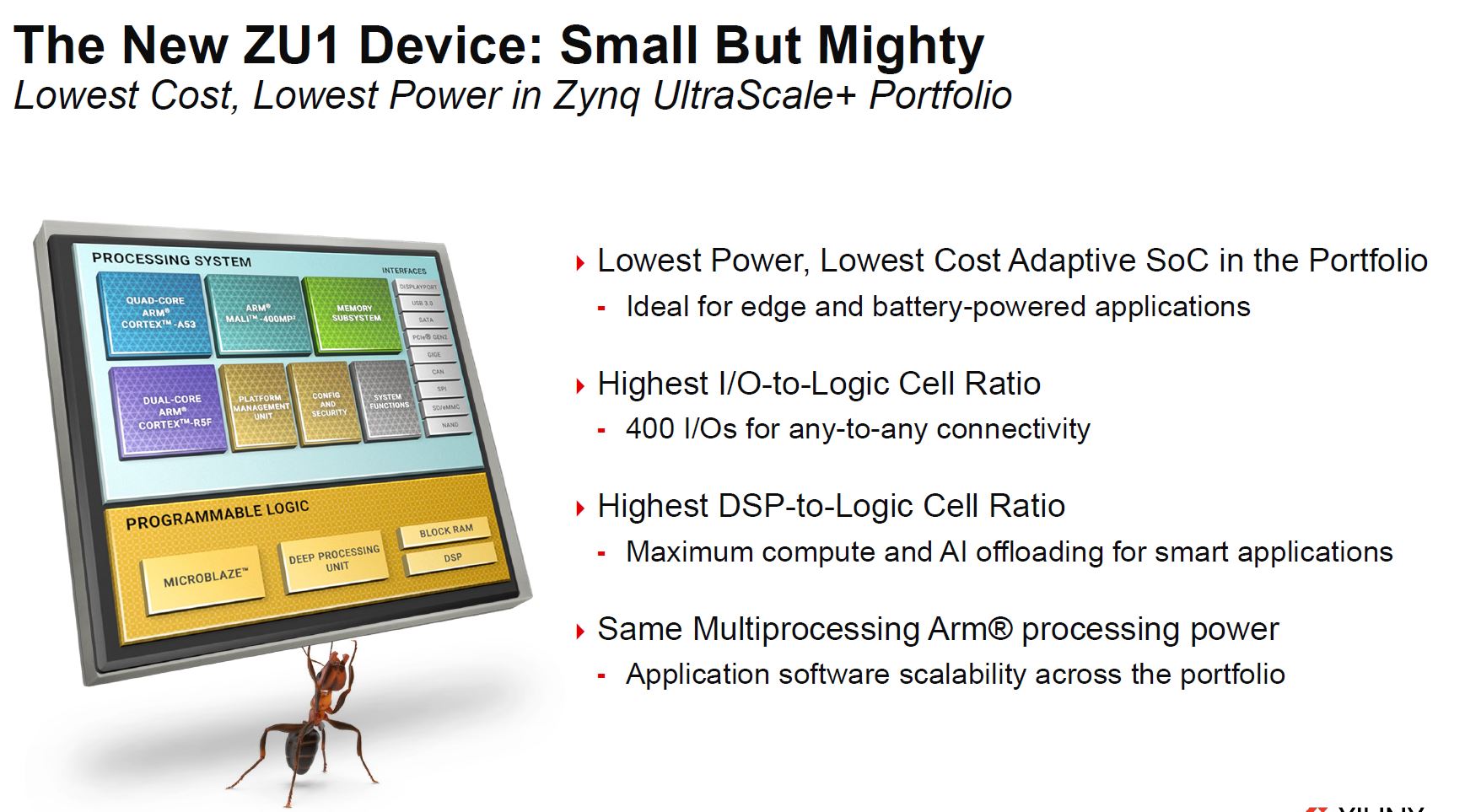

Xilinx Zynq UltraScale+ ZU1

The Xilinx Zynq UltraScale+ ZU1 combines a multi-core Arm processor for general purpose processing along with FPGA for fabric, I/O, logic, and DSP functionalities.

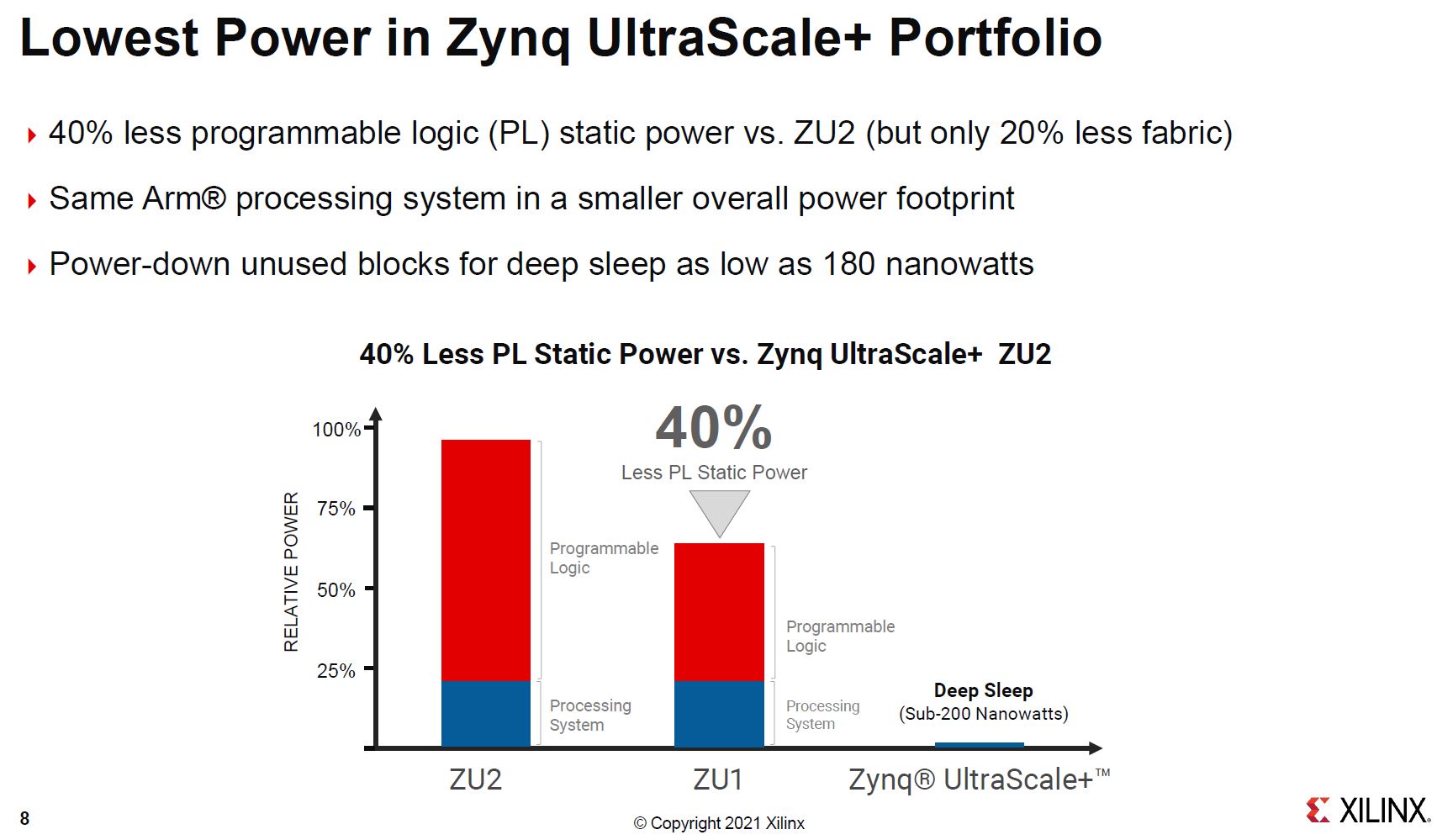

With the new series and Having 40% less static power in the programmable logic but only 20% less fabric, the new ZU1 is a new lower cost/power design. These chips also have a sub 200 nanowatt deep sleep capability.

One of the interesting bits here is that this is a way to deliver Arm + FPGA with I/O to a low-power market. We often focus on the data center and 5G FPGAs, but these are used in many devices.

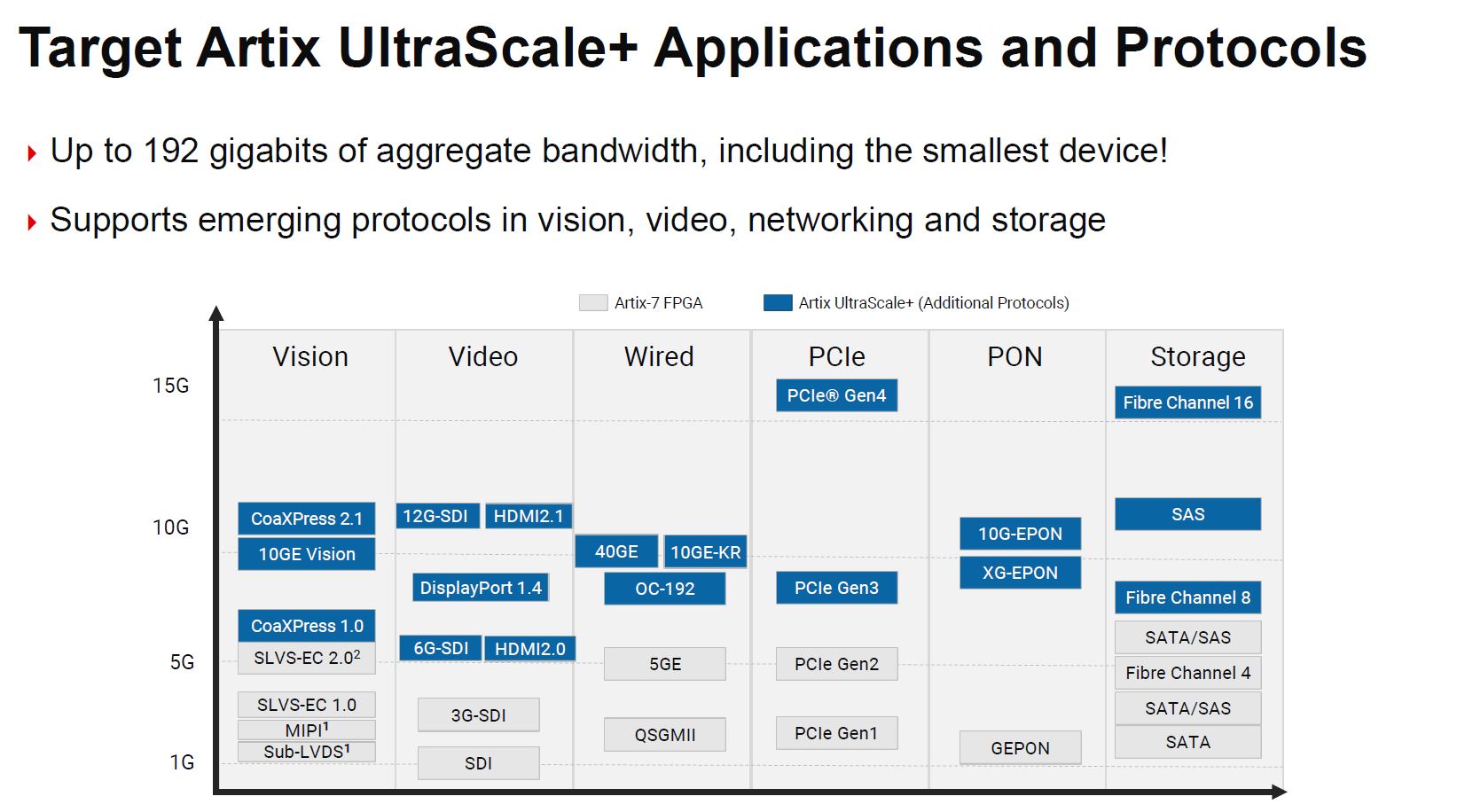

Xilinx Artix UltraScale+

The other side of this is the smaller Xilinx Artix UltraScale+ family.

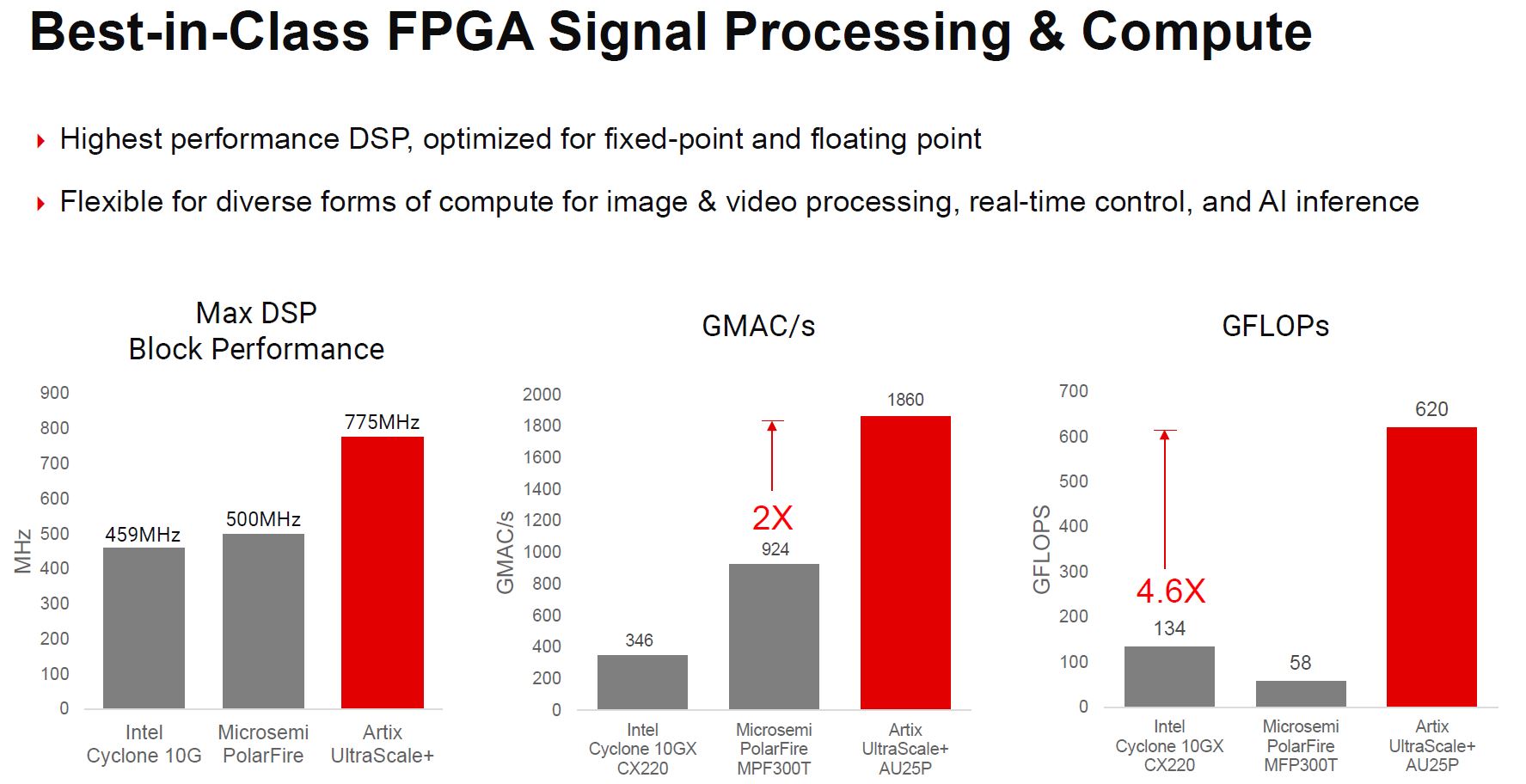

Here the focus is on I/O and DSP functionality. Even though this is a small low power chip, it has high-speed I/O.

One of the fun parts about the launch is that we get competitive low-cost FPGA benchmarks.

For some context, we often do not get this kind of competitive feature breakdown on FPGA launches.

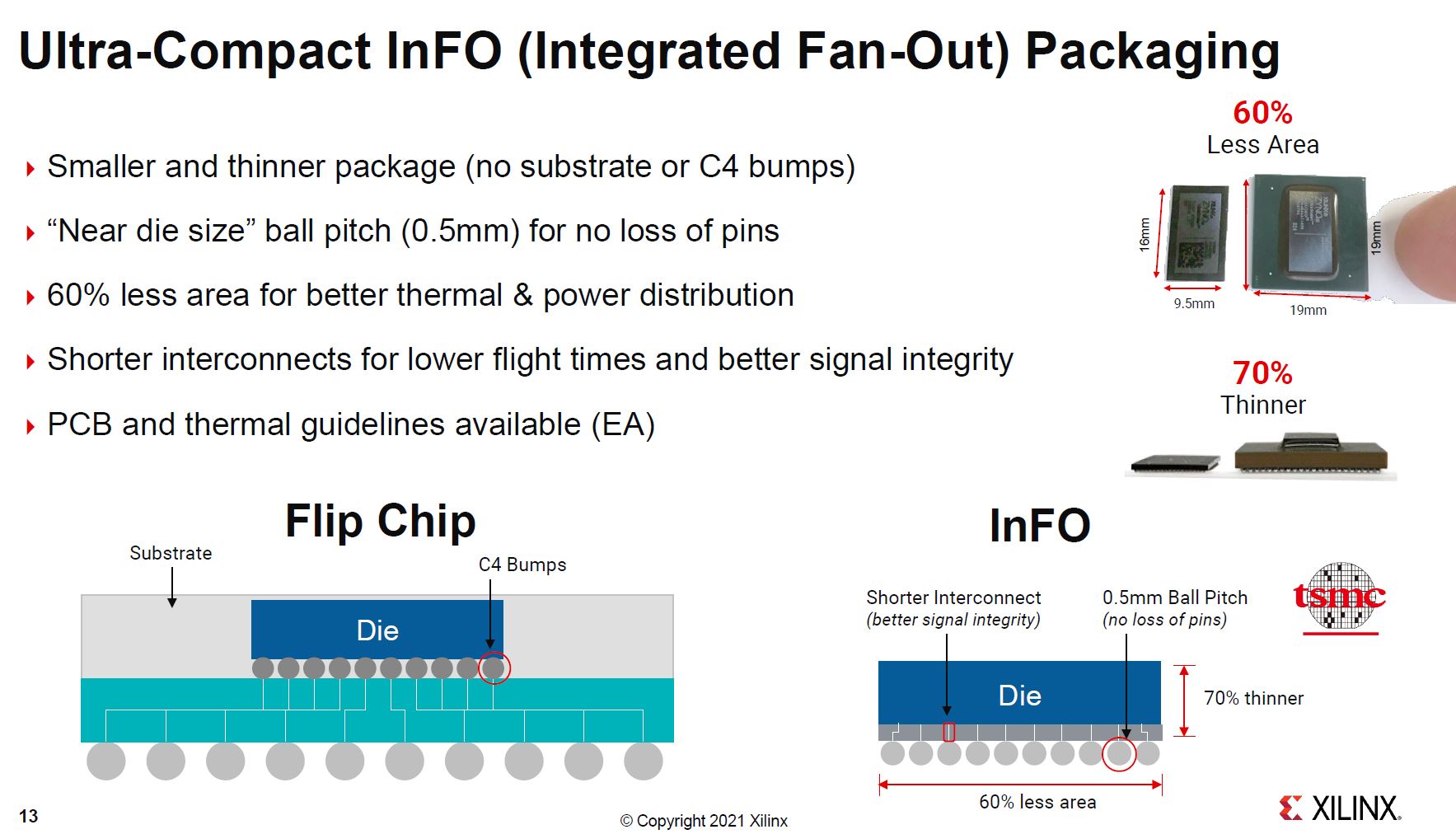

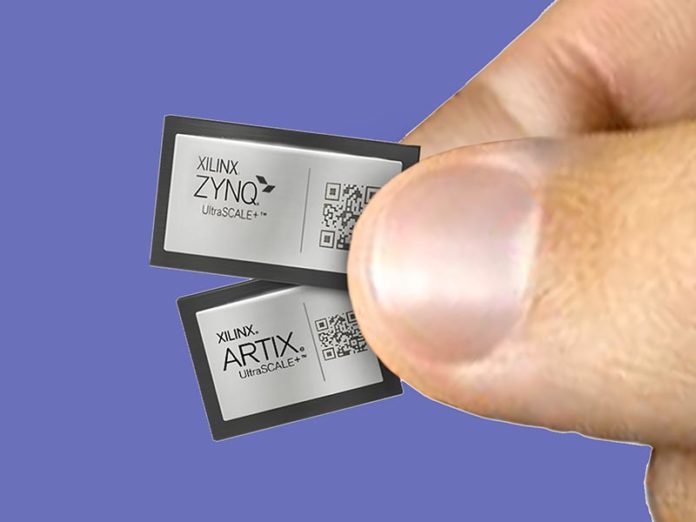

Ultra-Compact InFO Packaging and Family

One other change with this generation is the Ultra-Compact InFO packaging. This greatly reduces the chip size. In some systems, this will not necessarily matter. In devices with size and weight constraints such as handheld tools, the packaging is a key differentiator.

In terms of 16nm UltraScale+, Artix brings new low-end capabilities.

The ZU1 device beings Arm cores plus the FPGA logic to the lower cost and power segments.

Final Words

While these may not be the big FPGAs that are pushing terabits per second of data, they are still important. We call out every time we see Cyclone FPGAs, as an example, in high-end 100GbE/400GbE switches where they are used for features such as making status lights blink and control fans. By adding more capabilities in the low-end segment, Xilinx is offering another option for those applications where ASICs or general-purpose CPUs are not optimal. That simply gives more choice and capability in the market which is a good thing.

One obvious place these chips may find themselves: SFP modules. I already know of a couple of products that throw similar programmable logic and some hard logic into a SFP form factor to do SDI video to IP conversion. Interesting stuff seeing BNC connectors on a networking switch again.

Other applications that come to mind are various USB and video adapters Think DisplayPort 1.3/1.4 to HDMI 2.1 at high data rates. ASICs for those are coming but these FPGAs are a quick time-to-market and can enable features those future ASICs may not support.

Fascinating chips. I thought they already migrated to 16/14nm and below. I’m surprised about those Arm A53s, but I guess they don’t need major compute. Arm has stalled on their low power cores with the A55 sitting there for years now with no successor, so the A53 seems like an especially weak part. Apple’s low power cores have far surpassed the A55 for several generations now, so I wonder what night be possible there with smaller nodes.

> in high-end 100GbE/400GbE switches where they are used for features such as making status lights blink and control fans.

I’ve never really understood the need for FPGAs here. Wouldn’t a relatively low power and cheap microcontroller or ARM processor be just as good at generating a couple of PWM signals and monitor some tach signals, but have the benefit of being easy to program and flexible?

I assume there is something obvious I’m missing.

Parts like these are why the merger with AMD will be accretive… XIlinx is the 400 lb gorilla in FPGA…