The AMD EPYC 9004 is a massive CPU. The line codenamed AMD “Genoa” brings not just 50% more core count to the market but also 50% more memory channels. Getting full memory bandwidth from Genoa requires populating all twelve memory channels and using dual-rank DDR5 DIMMs. Still, for many, especially with smaller core count and lower-end servers, the cost of 12x DDR5 DIMMs, even 16GB will be too much. We expect those markets, as well as many markets where space is a constraint to use less than 12x DIMM configurations. For that, here is the handy memory population guide.

AMD EPYC 9004 Genoa Memory Population Guidelines for 1 2 4 8 10 12 DIMMs Per Socket

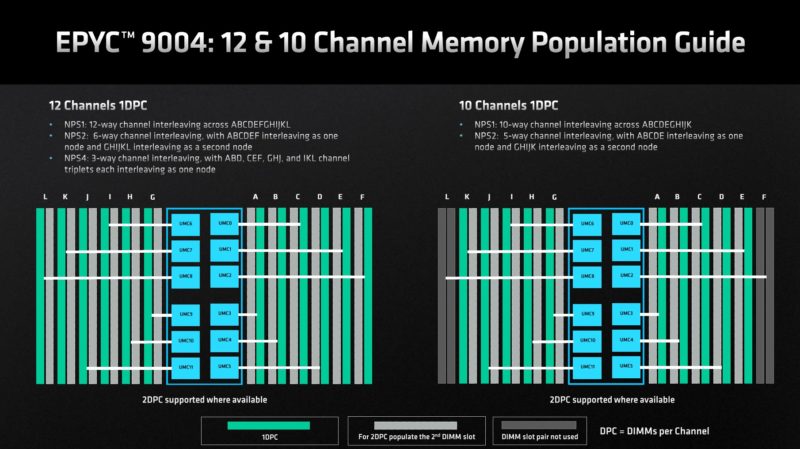

Populating all 12 channels is relatively simple, put a single DIMM in each channel. If there are two slots per channel, start with the ones furthest from the CPU in each channel. This has been the general guidance for years. In the 10-channel memory configuration, leave the two outer channels unoccupied. This may seem different for some of our readers.

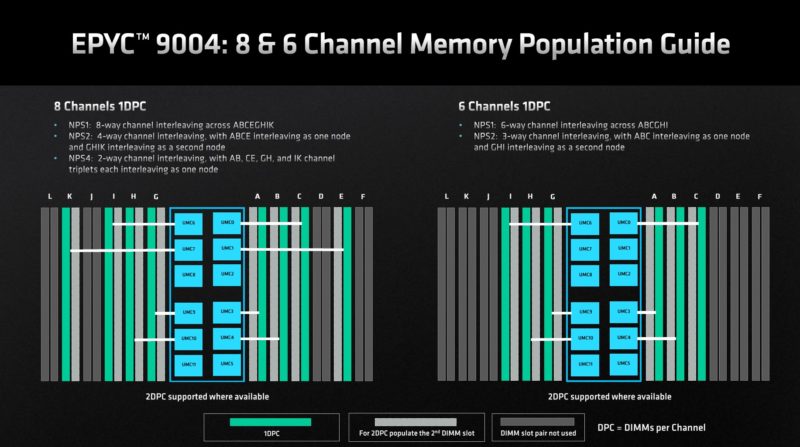

AMD’s Genoa memory population guide seems to require an even number of DIMM channels down to one, however, where things get really interesting is at 8 and 4 DIMMs per channel. Here, for 10 channels of memory occupied, one skips the outermost and the fourth channels from the socket, but the fifth channels from the socket should be occupied.

For six channels, it is simply the three closest to the CPU on each side.

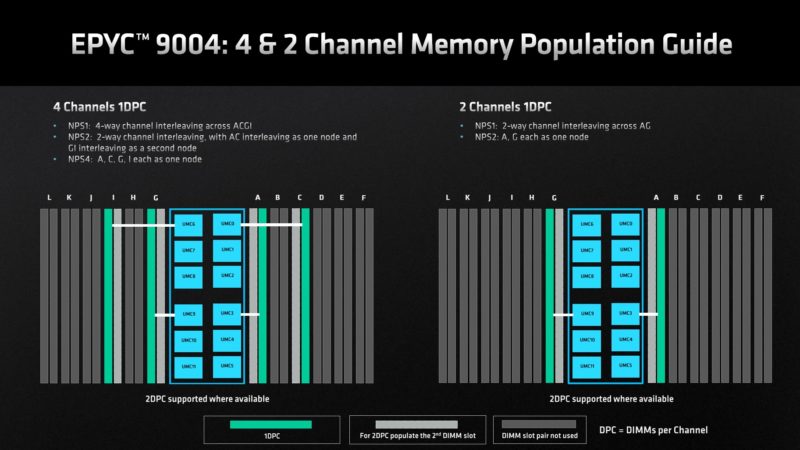

With four-channel memory, one populates the closest channels to the CPU, then the channels that are three from the CPU.

Two channels simply use the two closest channels to the processor.

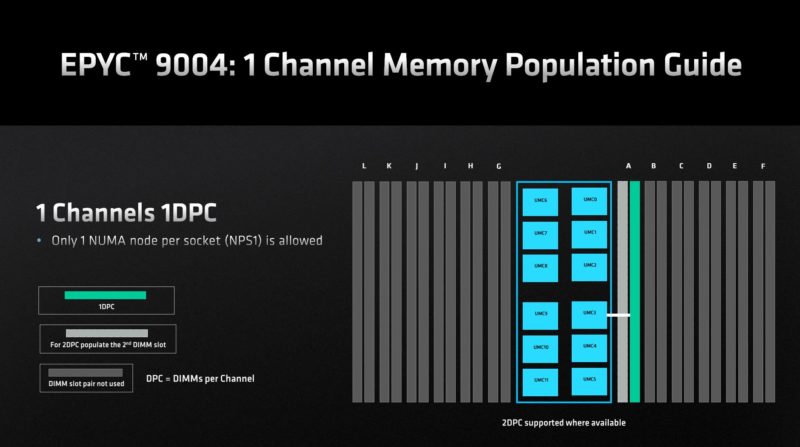

One channel memory should be the A or first memory channel. AMD shows 2 DIMMs per channel here, but we would expect if one has two DIMMs they would be placed in the 2 channel mode instead. Until 12 channels are populated, it seems wise to continue populating channels instead of running 2 DIMMs per channel (2DPC) modes.

Final Words

This was just a fun piece to help us explain the new memory population guidance for AMD EPYC 9004 “Genoa” servers. Many of the systems we have seen have seas of DIMM slots so this is bound to be a bigger question in the future. This felt a little bit too much like a “how to populate AMD EPYC 9004 Genoa memory” so we decided to pull it out of the main AMD EPYC Genoa launch piece. If you want to learn more about Genoa, check out that piece or the video that you can find here:

We have very in-depth content on the new processors.

Nice. Now we need similar Plumbing guidelines. :-)

I mean Liquid Cooling !!!. Say You have Liquid manifold capable of 24 servers, now populate from 1 server to 24. Which hose to connect which nozzle.

So dual socket, twelve channels per socket, two DIMMs per channel, 48 DIMMs?!

Makes sense if you have 128GB DIMMs, 48 will get you to the 6TB. But surely there is not enough physical space in a 1U or 2U server for that many DIMM slots, especially with the gargantuan SP5 socket. Will we see riser cards again or are we realistically only going to see single DIMM per channel for dual socket boards and 256GB DIMMs as the only way to 6TB?

I don’t see riser cards as becoming a thing again with how tight everything needs to be with signalling and trace length these days. I’m very curious to see what designs come up.

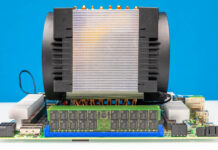

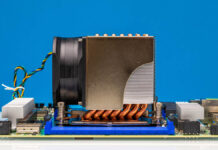

Are you going to do an “Installing the CPU & Heatsink” guide for EPYC 9004 like has been done with the previous CPU releases?

I would be very interested in how these different memory configurations would perform in real life. It is obvious 12channel 1DPC would perform best, but just how much performance would we leave on the table when going for configurations with less dimms. Where is the price versus performance sweet spot with a certain amount of memory?

Some boards might end up with 1 dimm slot per channel (12 DIMMs slots per socket) where others have 2 dimm slots per channel 24 DIMMs per socket? Fewer DIMMs per channel for physical space constraints in multi socket nodes?

@Rosse, Mcihael Larabel from Phoronix has some benchmarks here: https://www.phoronix.com/review/ddr5-epyc-9004-genoa

do you have to use identical sized dimms? i read the last gen you could mix and match as long as groups were the same size. has this changed?