Nantero NRAM Scaling

Being able to build a single circuit is one thing. Being able to build a useful device is another. As we noted in the introduction, Fujitsu is planning to do this in 2019. Making larger devices means integrating with existing technologies.

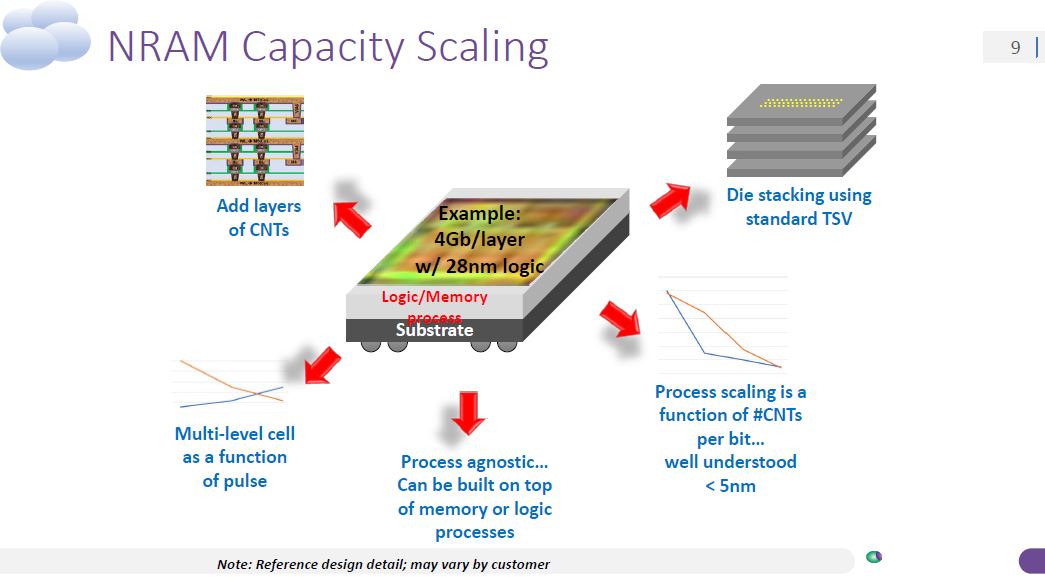

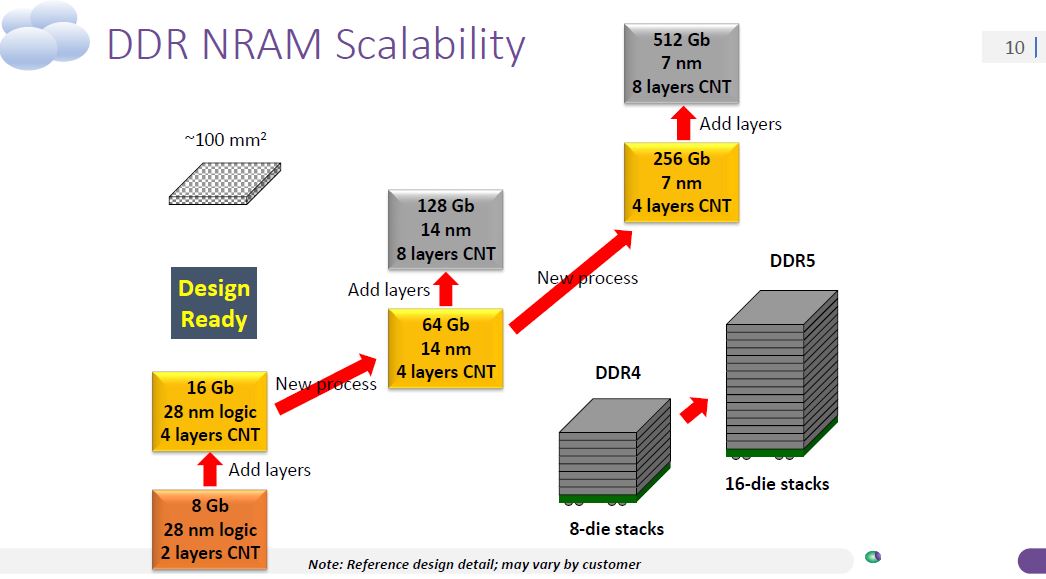

The basics of this are that the company thinks it can use new process technologies and stacking layers of carbon nanotubes to scale capacity. Natero says it can hit 8Gb on 4 layers, and 16Gb on 4 layers at 28nm. It is worth noting that the 2019 Fujitsu NRAM will be built on a 55nm process so we expect smaller modules.

By adding stacks to 8, and shrinking the process, the company thinks it can hit 128Gb devices. As the industry transitions from DDR4 to DDR5, the spec allows for up to 16 die stacks so the company thinks it can again get gains and very large devices.

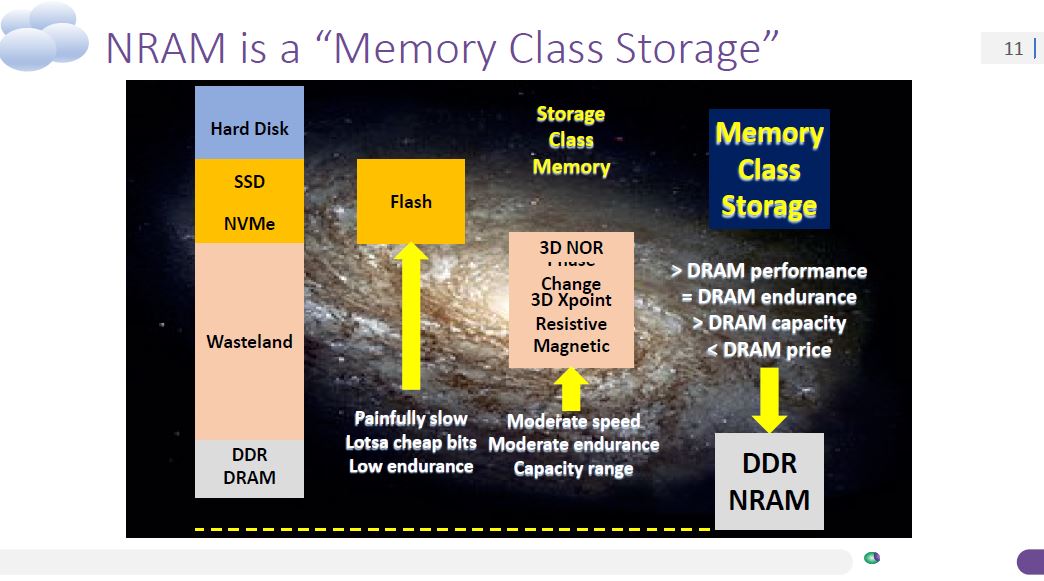

With DRAM like speeds, no write endurance issues, higher capacity than DRAM and potentially lower pricing (assuming volume production), Natero calls this memory class storage. That compares to Intel 3D Xpoint which is somewhere between NAND and DRAM. Nantero sees NRAM as essentially occupying the DRAM space but adding persistence.

Nantero NRAM Speeds and Efficiency

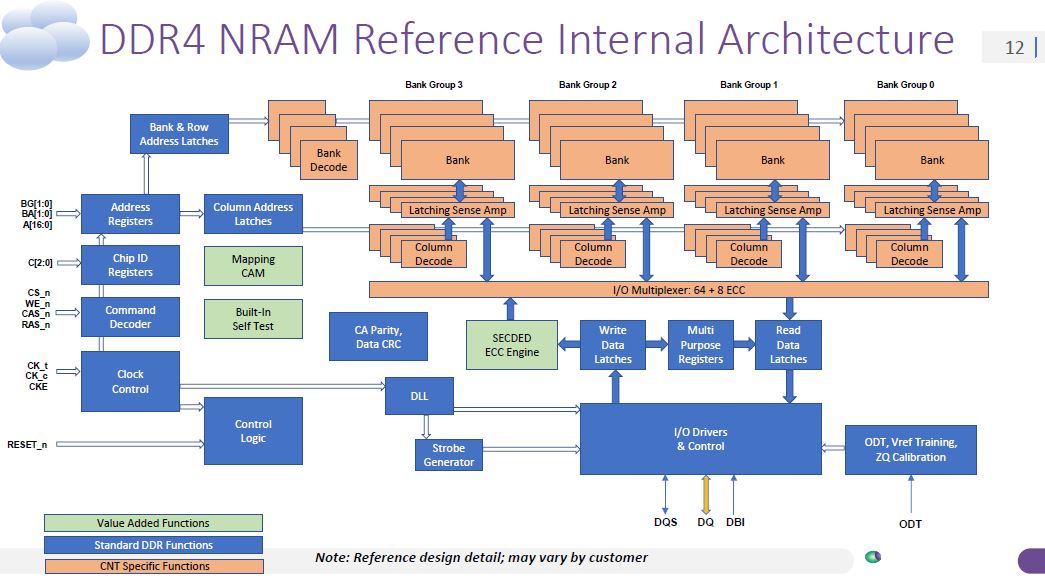

At STH, we know many people care about how the technology will impact them rather than how to build devices themselves. Since most of our readers to not fab their own DRAM or NAND chips, we are going to present the slides on how NRAM can be a DDR4 DRAM replacement, but not offer too much commentary. Skip to the next page if you want to skip this section.

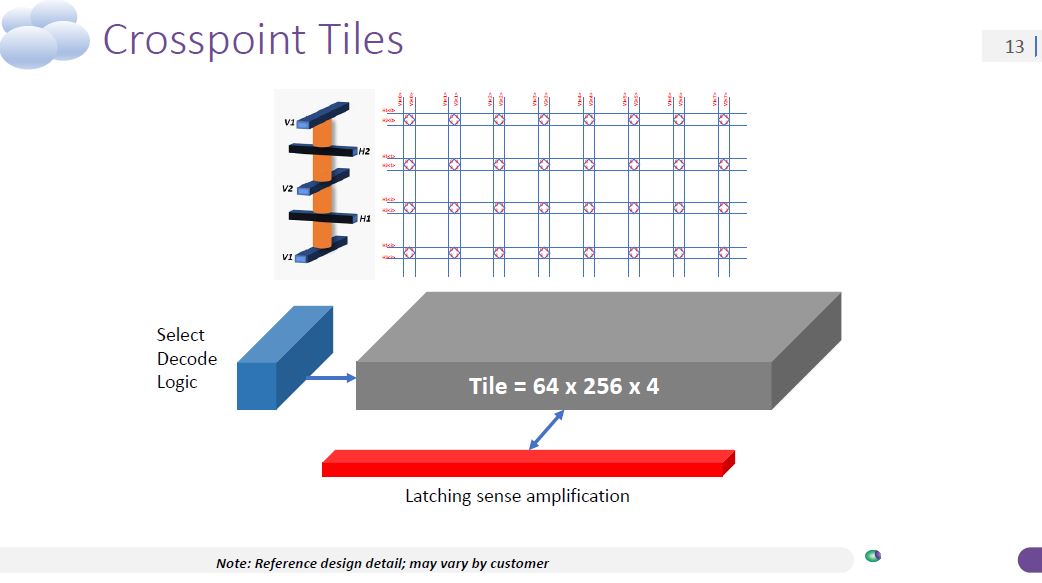

Nantero has a reference architecture. The company hopes to license its technology but not create its products itself. During the talk, the company specifically said it was pursuing an Arm-like model.

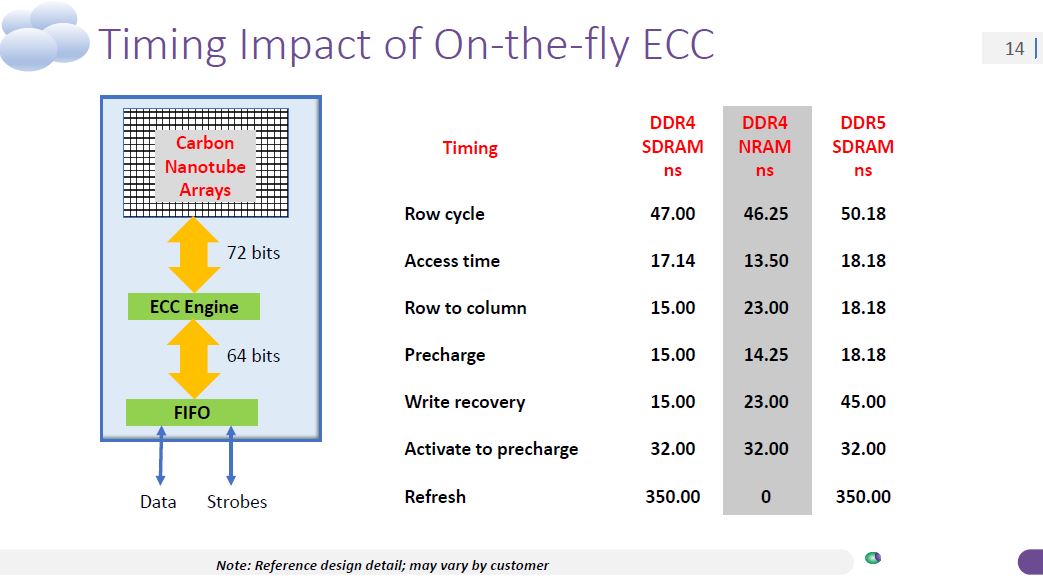

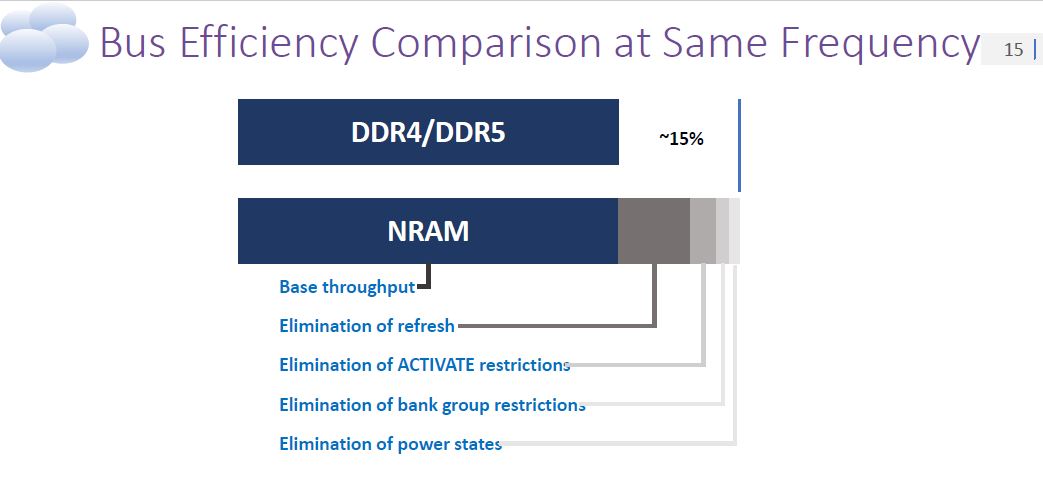

Questions were raised about performance. The company thinks that the performance is relatively on-par with DRAM.

Part of that comes from not having to do a refresh.

The audience was a bit skeptical to say the least, so we will have to see how actual devices perform.

While this might seem like everything is too good to be true, this was something that has been a long time coming. A few years ago UW Madison created carbon nanotube transistors that out performed silicon. https://news.wisc.edu/for-first-time-carbon-nanotube-transistors-outperform-silicon/ With a couple more years of R&D and process refinements it isn’t out of the question that nanotubes are getting to the point of being ready for RAM and eventually will probably replace silicon inside GPUs and CPUs.

A couple interesting questions pop to mind then:

– How well does a cell hold up under varying environmental conditions: Temperature, humidity, shock (Both physical and thermal shock), vibration?

– Do to the mechanical deformation involved, does the cell wear out?

– Due to a vibration or shock (physical or thermal again), can the gap necessary be created or destroyed creating a false bit flip?

Hi, guys, thanks for following up on this. We’re pretty excited for obvious reasons. To Don’s questions, we haven’t yet seen any tendencies for wear-out. The carbon nanotubes move in a void but once the contact is made between tubes via injection of electrostatic force, the bonding is atomic inside the van der Waals region. To separate the tube connections, a phononic disruption is needed to jump back over the vdW barrier. Macro effects like shock and vibe don’t impact the cells which are molecular level effects. Also, we use hundreds of switching tubes per cell so anything that would have that kind of impact would have other more catastrophic effects. One of the things carbon nanotubes are known for is lack of sensitivity to thermals, so temperature extremes don’t seem to have any effect on the cells; the limit would be the underlying CMOS.