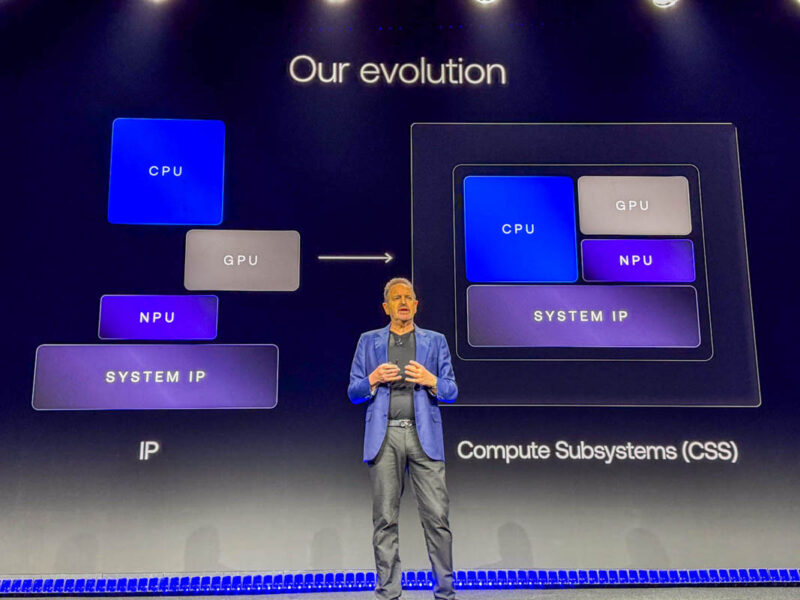

Today was perhaps one of the biggest days for evolving Arm’s business. Traditionally, Arm has sold its IP to other companies to integrate into their designs. With the Arm AGI CPU, Arm is evolving to sell full chips. For the industry, this is an enormous move as the Arm ISA continues to grow in the AI space.

Arm AGI CPU Launched

When we first saw Arm in the data center, the company was selling IP to customers to integrate into their own chips. Over the years, this evolved with Neoverse cores and Neoverse CSS.

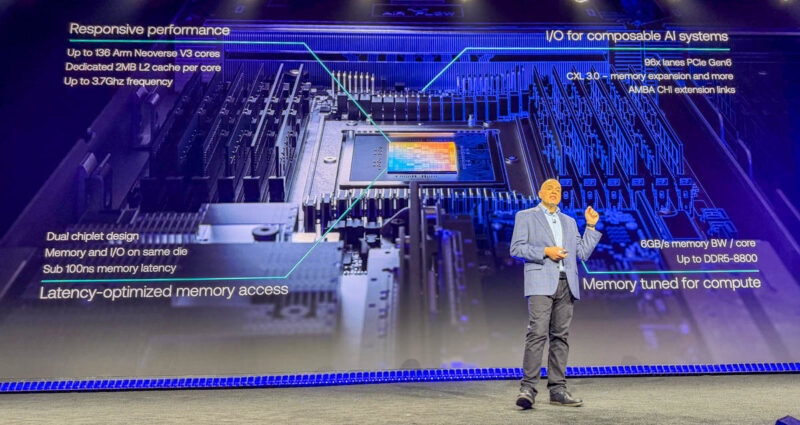

The new design will bring up to 136 Arm Neoverse V3 cores into a single socket. That is just a bit more than the Microsoft Azure Cobalt 200 with 132 Arm Neoverse V3 Cores. Arm is targeting those cores with 2MB of L2 cache per core. On the I/O side there are 96 PCIe Gen6 lanes and CXL support for memory expansion. With the DRAM supply challenges, the CXL Memory Expansion devices, as we highlighted, are becoming extremely popular.

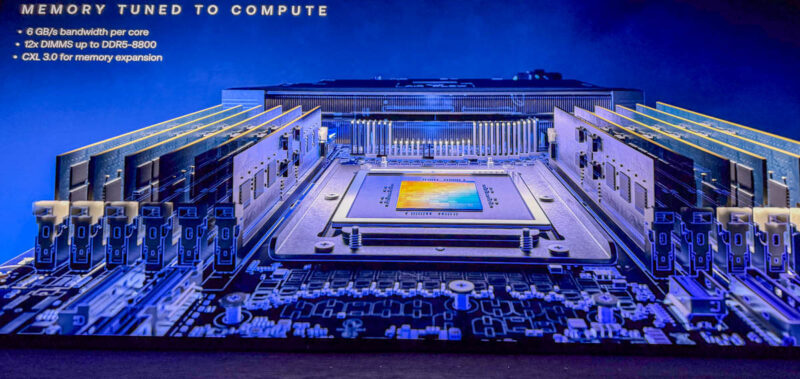

Arm is using a dual-chiplet design with the PCIe and memory controllers on the two dies that are the same. This is more like 5th Gen Intel Xeon Processors Emerald Rapids in terms of using two integrated dies. Arm says that its new CPUs have 12-channel memory at up to DDR5-8800. As a reference, we expect both Intel and AMD to have 16-channel DDR5 platforms with higher speed MRDIMM support later this year.

Arm says that 4-6GB/s is the sweet spot for per core memory bandwidth.

That is what Arm is saying that will drive performance over other solutions in agentic workflows.

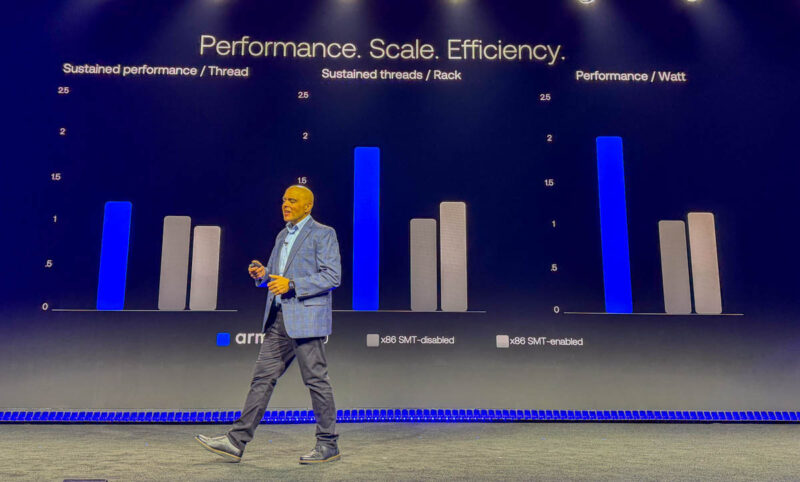

Something really interesting is that Arm is showing its x86 competition as an AMD EPYC processor, not an Intel Xeon. Times have changed.

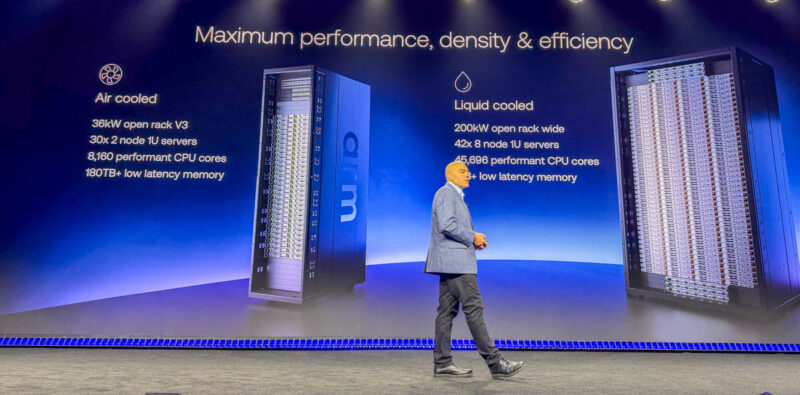

The key idea of this design with many single socket nodes is that it will allow for over 8,000 cores per ORv3 36kW air-cooled rack, and much more on the liquid-cooled double-wide form factors. Arm showed a 200kW liquid-cooled rack, but it said that the actual power density is closer to 100kW.

On the topic of competing with customers, Arm actually highlighted that the market is enormous. Meta is perhaps the headline customer for the line.

OpenAI was on stage, so we might expect them to be a big customer. Others, like Cloudflare, SAP, and others, were noted as well.

Arm is not doing this as a one-off. Instead, Arm has a multi-year roadmap for future chips.

Arm also has partners like Lenovo, ASRock Rack, QCT, and Supermicro lined up to sell systems based on the design.

Final Words

Arm says it will be in production later in 2026. That is exciting. Hopefully, we will get these systems to test out soon. This is a huge deal for Arm, and we will be diving into it more in the coming months. An advantage of a rapidly growing data center market is that we get more competition and more server CPUs. 2026 is shaping up to be completely different than 2026 in that regard.

Since a lot of folks at the event were talking about competitive aspects of this, and I got asked a lot for my thoughts, I took some notes for our Substack:

Looks like it has the potential to be an interesting part, especially if the amount ARM is handling means that non-hyperscalers can potentially actually get a look at one outside of a cloud VM instance; but whoever in marketing decided that ‘bunch of neoverse cores’ = ‘AGI CPU’ should maybe set the kool-aide down on the nearest stable flat surface and take a little break.

LOL @ the slide criticizing x86 competitors’ “legacy support” and “technical debt.” Brave of ARM to come straight out of the gate with “here’s what our competition does well, and what we plan to do poorly.”

If I see another CEO holding up yet another piece of plastic with the company logo on it……cute and cool at the beginning, now its become a photo op……nearly a meme.

Waiting for a Dilbert showing him holding up a piece of plastic that says “Kilroy”.

No product? Just an announcement of one? and the stock did what today???

So a V3 product that likely will see actual availability in 2027. Yawn. And the platform/board is being made and maintained by whom? Clearly there is a market gap with Ampere being on a no-buy list for obvious reasons, but this feels very lackluster and halfhearted, reminds me of first Epyc iteration. Pushing the efficiency malarkey due to non-legacy instruction set might fly with consumers but it doesn’t make sense here.