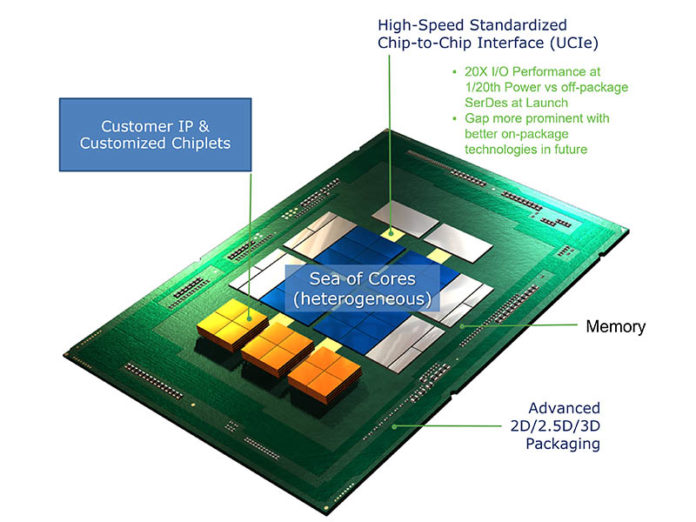

The UCIe 3.0 spec is out with a big speed up for future generations of chiplets. For those who need to catch up, UCIe is the leading consortium for chiplet interoperability. When we talk about future generations of packages, the idea that IP from different companies can be fabricated at different foundries and then assembled into working packages is a driving force behind this design.

UCIe 3.0 Spec Released with Big Speed Up for Chiplets

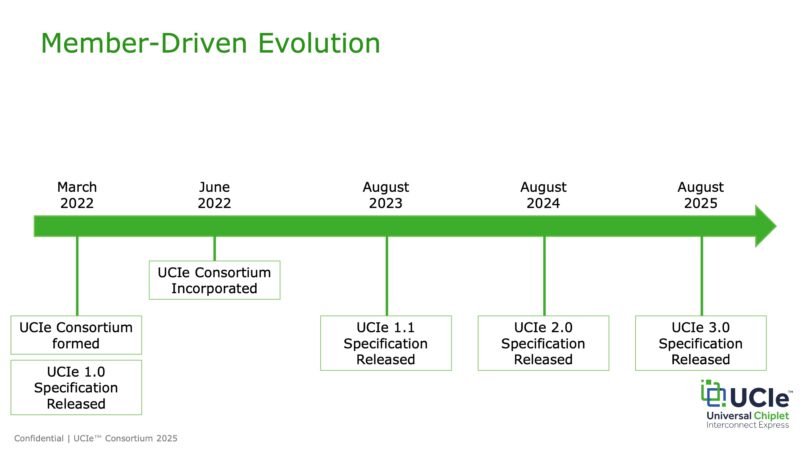

It feels like yesterday we were covering the Universal Chiplet Interconnect Express UCIe 1.0 Launch. That was actually back in 2022. Since then, we have been getting annual updates in the August timeframe. This year, we are on UCIe 3.0.

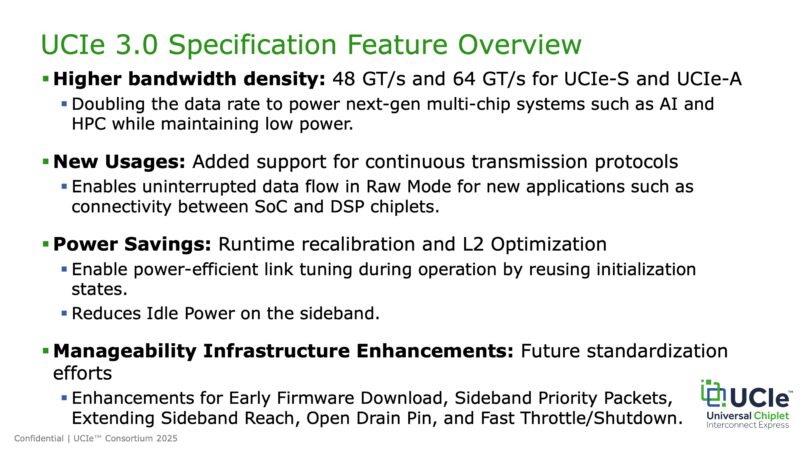

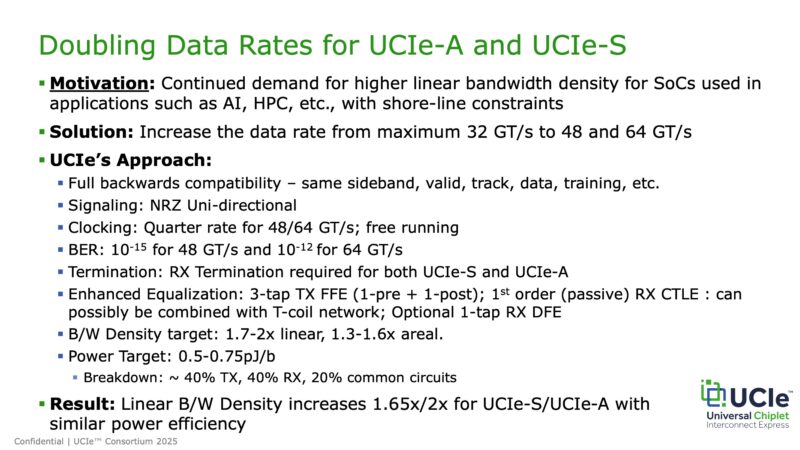

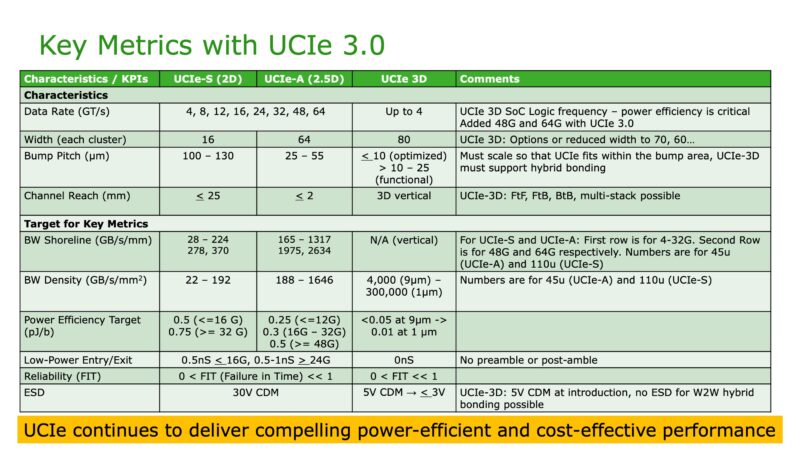

UCIe 3.0’s headline feature is higher bandwidth density for UCIe-S and UCIe for 2D and 2.5D designs. Doubling the data rate yields more throughput per pin and that matters when chip-to-chip communication is often gated by the number of connections that can fit into an area of a chip.

The new data rates move from 32GT/s to 48GT/s and 64GT/s.

The UCIe 3D has fewer challenges with bandwidth, but for the UCIe-S 2D and UCIe-A 2.5D the higher data rates are the big headline feature.

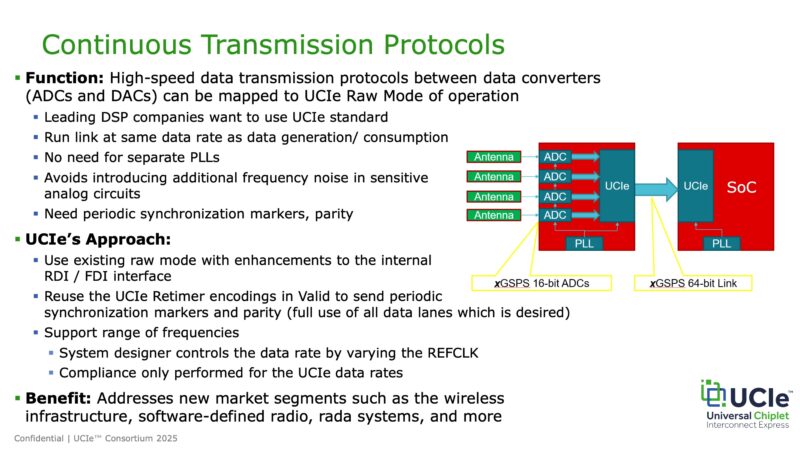

There are other improvements like continuous trasmission protocols for companies that are making IP around data converters which are then mapped to UCIe Raw Mode.

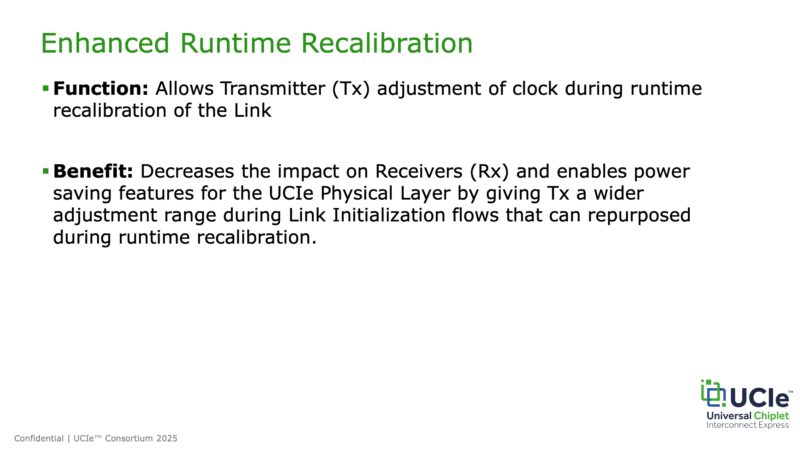

There is another feature called enhanced runtime recalibration to lower the power of links and chiplets. We will let you read this one.

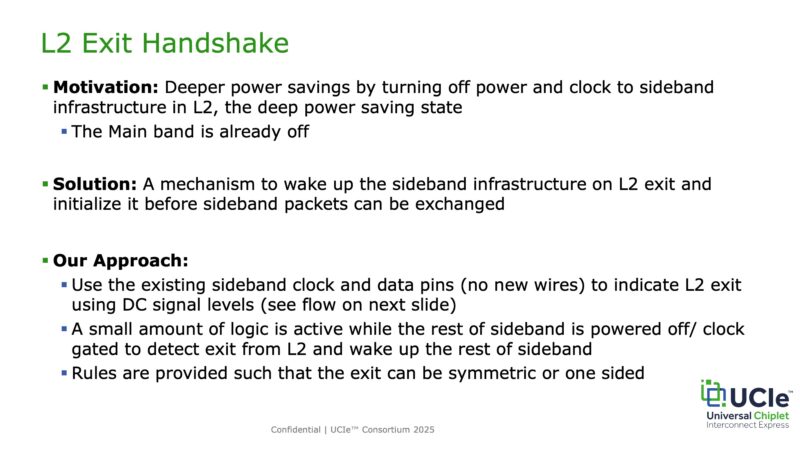

The L2 Exit Handshake is also one that allows additional power savings.

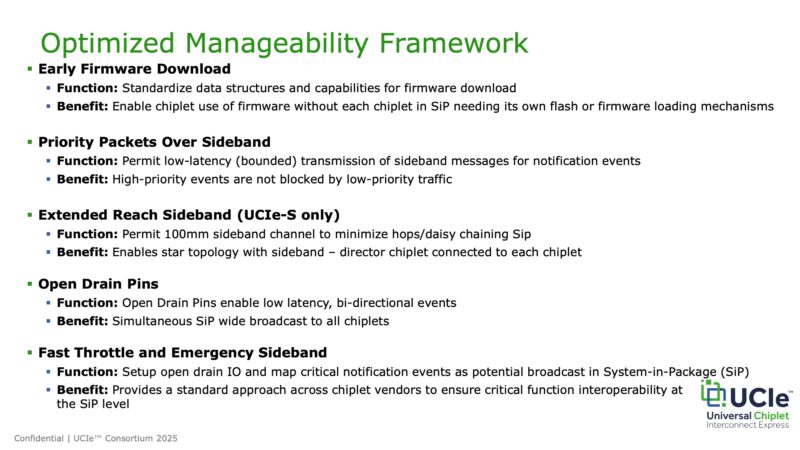

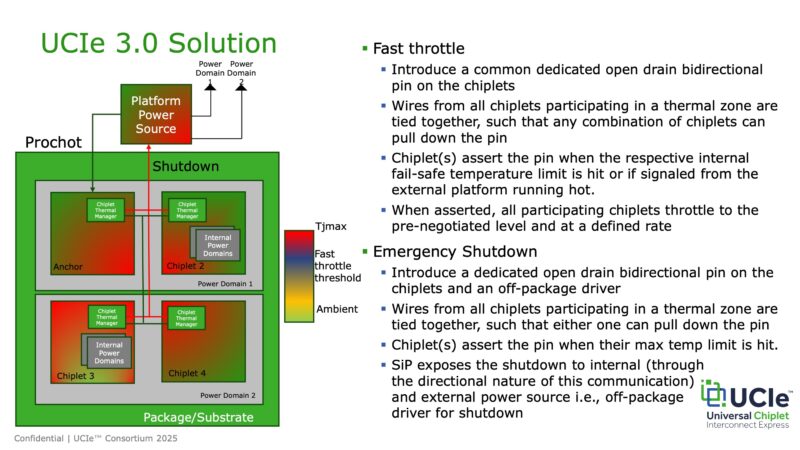

The manageability framework helps when you have a complex package and have to update firmware and manage the chiplets. The open drain pins are used for things like emergency power events where the server loses power it can help quickly let chiplets know what is happening.

Here is the UCIe 3.0 solution diagram slide with the emergency shutdown example.

There are plenty of new features in the spec.

Final Words

There are plenty of companies that are both board members as well as member companies. This is the big chiplet ecosystem.

Since you are probably interested, I asked when we would start seeing chips. Usually it is 3-4 years for a chip to go through design, so if UCIe 1.0 came out in 2022, it should be fairly soon. I suspect in 2026 we are going to see designs, but that is just a guess. That also means that UCIe 3.0 is likely a chip feature in 2028-2029.