At the Marvell Analyst Day 2025, the company announced its new ultra-power-optimized memory. This is interesting because it is not the only SRAM optimization that Marvell has discussed this year. For those who do not know, Marvell makes a lot of connectivity IP solutions, from the AQC113C NICs you may have running 10GbE NICs in your PC to designing XPUs with hyper-scalers.

Marvell has a 2nm Ultra-Power-Optimized Memory

This was a bit of a surprise announcement this week. Previously, Marvell has discussed its Custom HBM solutions that help lower the area required on the compute tile to implement HBM.

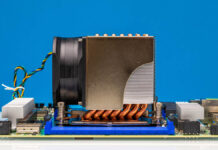

The company also showed off its Dense SRAM at Hot Chips 2025. By changing the clocks and ports in SRAM, the company is able to get more bandwidth from on-chip SRAM than a 3rd party licensed SRAM.

A product announcement at the analyst day was that Marvell has a 2nm memory that is denser and lower power. Memory scaling has been an industry issue. New process nodes that have successfully reduced the footprint of other features have recently struggled to deliver meaningful memory benefits.

Marvell is comparing its memory to what you can get off the shelf to integrate into 2nm class systems. It says that its memory uses lower power and takes less area while also being more rectangular for easier placement.

Final Words

Scaling memory in newer process nodes is a challenge, and this looks like one answer. Notably, Marvell is using a comparison point of memory that one can license from the big IP providers, not what other chipmakers have in terms of IP. Still, three custom memory products have been announced over the last year, making this a clear direction. Usually, these types of products do not get developed if there is no demand, raising the question of whether we will ever get to learn which chips these technologies were developed for.

So… another datacenter-only type of memory that will never reach consumers because they’ll stop producing it before it gets into low-margin profit territory?

Modern computing is overrated. Just get a Commodore 64 Ultimate and enjoy the rest of the time outside growing vegetables.