Hot Chips, the semiconductor industry’s leading conferences on high-performance microprocessors and related integrated circuits is taking place this week. Living up to its name, the show offers a rather deep look at some of the latest and hottest chips in the industry, from smaller vendors specializing in RISC-V all the way up to the big names like Intel, IBM, and NVIDIA – many with their big chips in tow. Spanning everything from CPUs and GPUs to security and silicon photonics, the conference offers a wide breadth of talks across multiple subjects.

The full schedule can be found here. This morning’s sessions are dedicated to talks on CPU architectures, with the first out of the gate being Condor Computing and their Cuzco RISC-V architecture. So without further ado, let’s dive in.

A subsidiary of Andes Technology, Condor Computing is focused on developing high-performance RISC-V cores. The Cuzco is their first design, coming from a relatively small team of just 50 engineers.

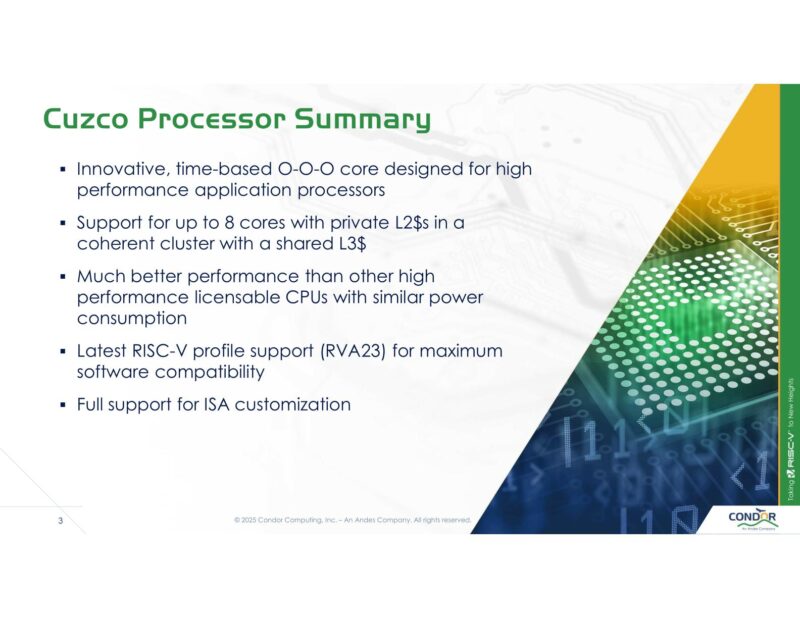

There are several firms developing high-performance RISC-V cores. Condor wants to be the best, delivering the highest performance within a similar power envelope. The RISC-V ecosystem is still maturing, so we’re in the portion of its development where there’s room for lots of players, before there is eventually a shake-out that winnows things down to fewer players.

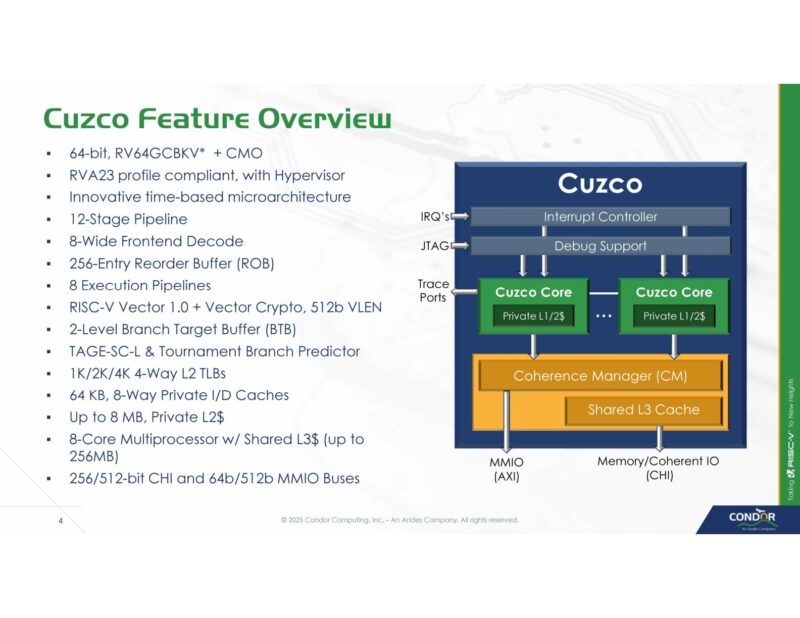

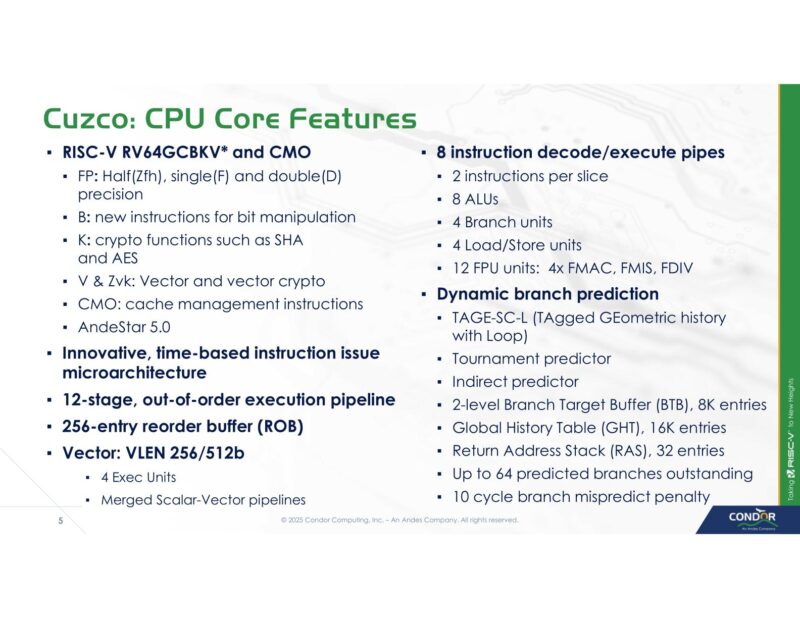

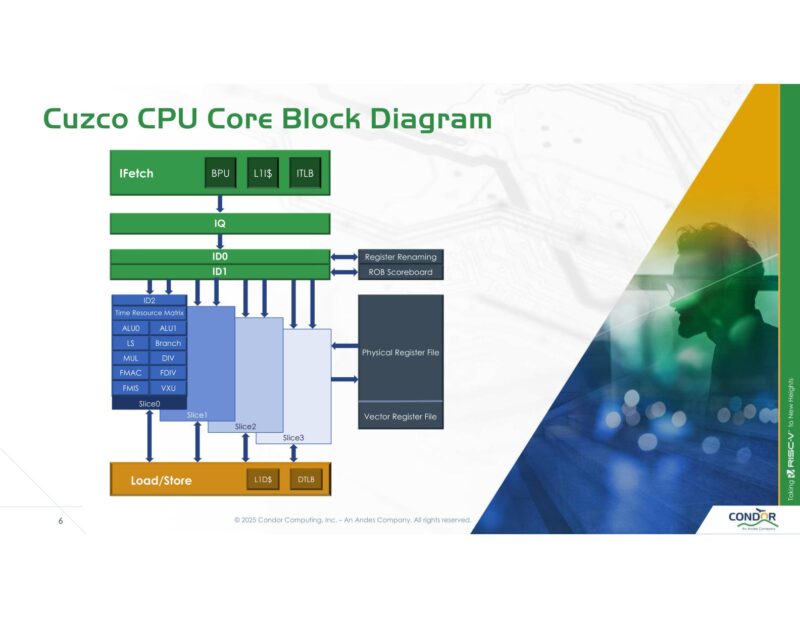

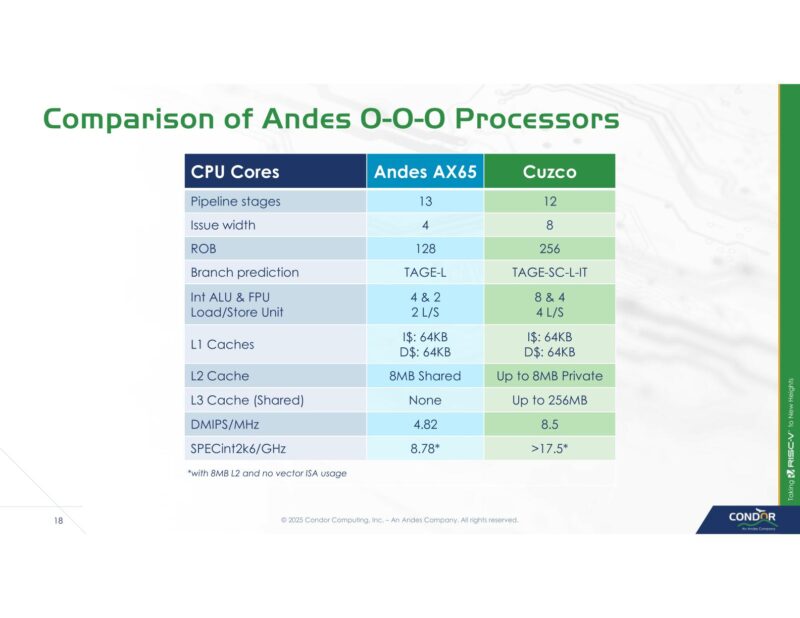

At a very high level, the Cuzco is designed a lot like other high performance processors. This means a wide front-end, a fairly deep 256 entry reorder buffer, 8 execution pipelines, etc. Condor isn’t looking to reinvent the wheel here; they’re looking to make a better optimized wheel than the other parties in the RISC-V ecosystem.

Cuzco is a complete IP design. That is, it’s not just a CPU core, but also has cache and coherency management; it is essentially ready to be plugged into memory and I/O buses. But it goes without saying that the CPU core is going to be the highlight here – and it’s what Condor focuses on the most.

Cuzco is compliant with the RVA23 profile for RISC-V, which is the first major profile for high-performance RISC-V computing. Of particular note is the profile’s inclusion of support for vector instructions, which is incredibly important for high-performance computing – not to mention manipulating large amounts of data in an energy-efficient manner.

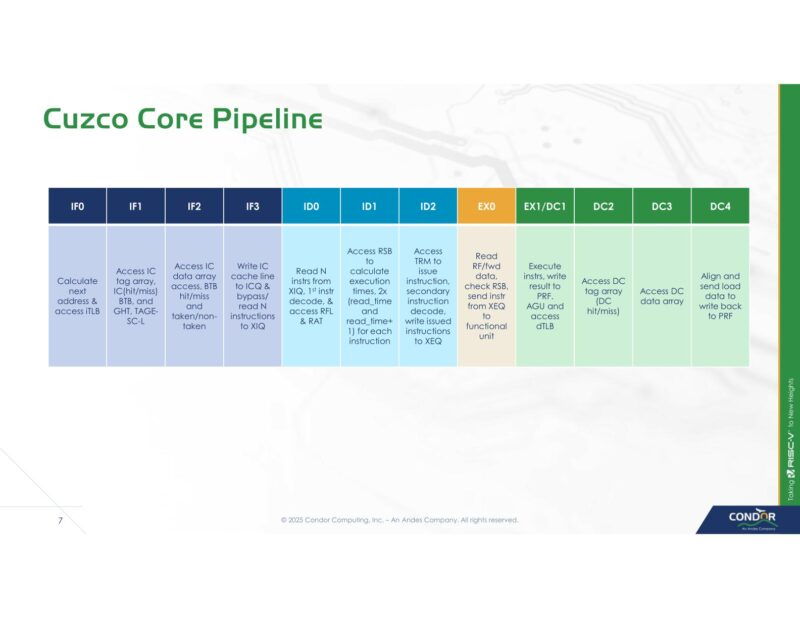

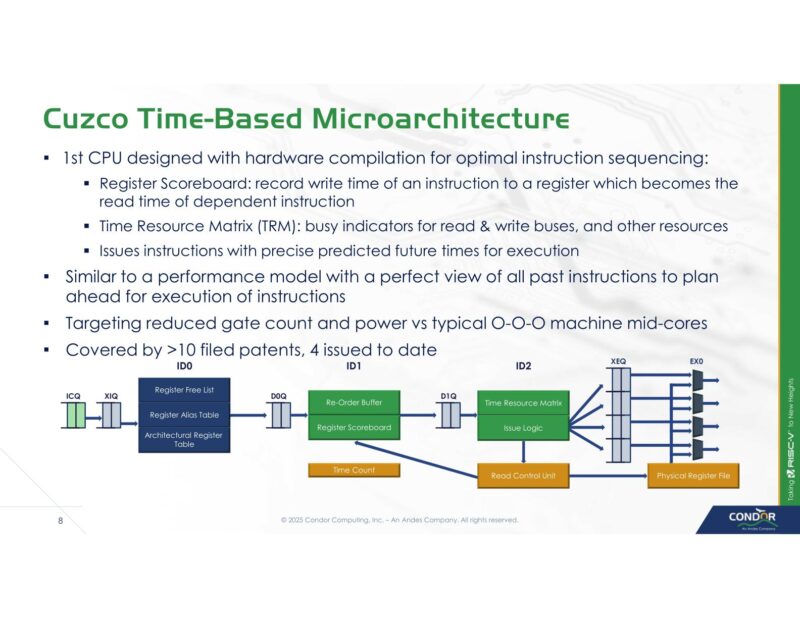

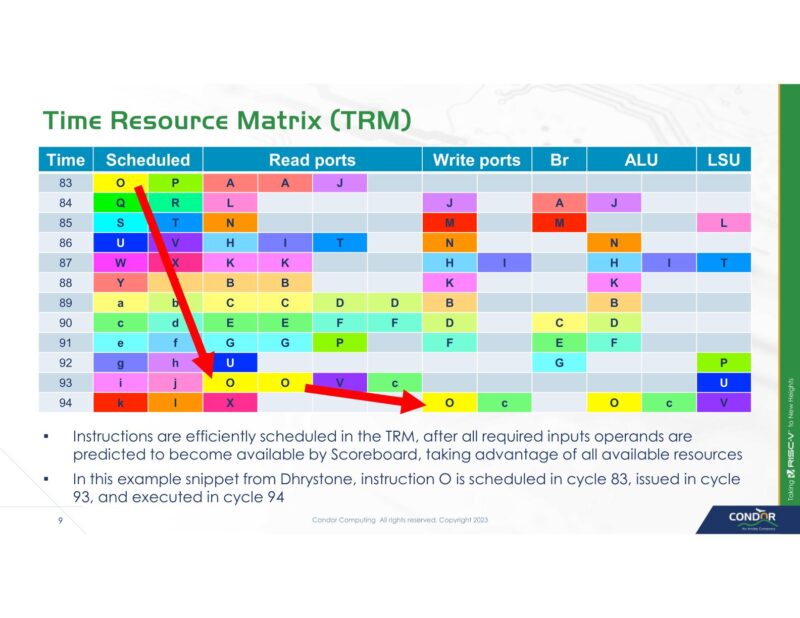

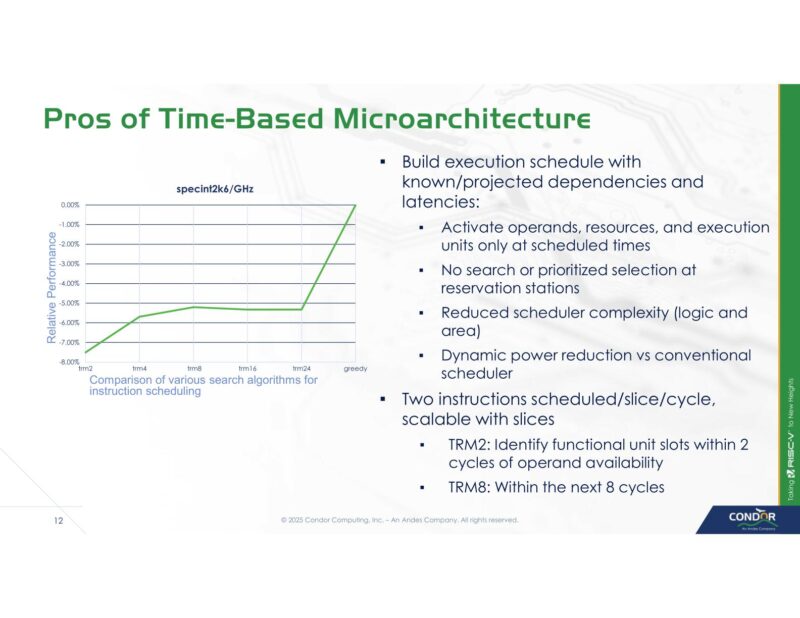

Condor employs a time-based micharchitecture for Cuzco. This quickly gets more advanced than can be explained entirely in a live blog, but they are essentially using hardware compilation for instruction sequencing. In short, they are attempting to improve on out-of-order execution by designing a method that requires fewer transistors and is more energy efficient as a result. In some respects this sounds like a variation on traditional methods of static instruction scheduling in advance in software (via the compiler), but with some of that work moved into hardware without voiding the idea entirely.

Ultimately, Condor believes that their hardware scheduling system can achieve better results than traditional OoO scheduling at a fraction of the power and complexity. And with power being the critical bottleneck to overall performance, optimizations here will pay off with more performance.

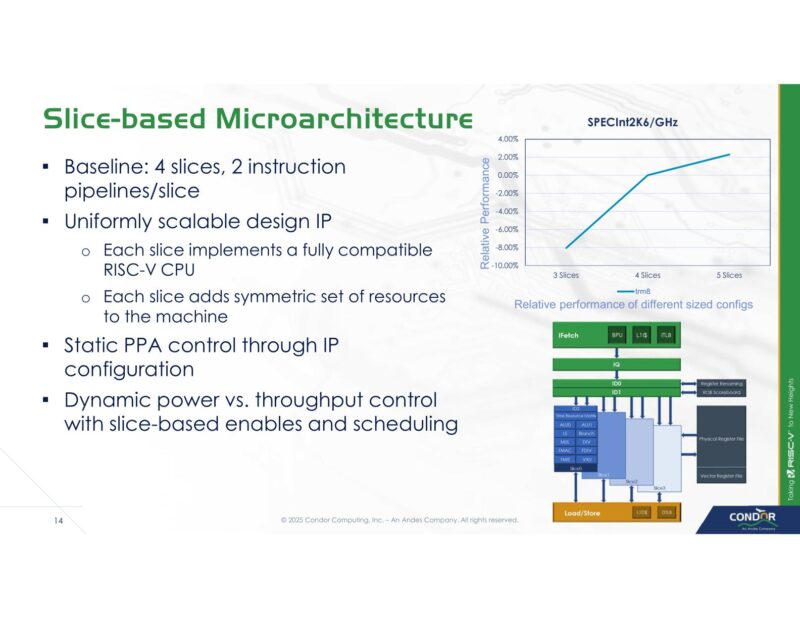

Cuzco uses a slice-based CPU design, with up to 8 CPU cores in total.

Compared to other OoO designs from their parent company, the Cuzco team believes that their design can deliver almost twice as much performance per clock in SPECint2006 than Andres’ current AX65 core.

The IP itself will be delivered at up to 8 cores with private L2 and shared L3. Interfacing via a wide CHI bus.