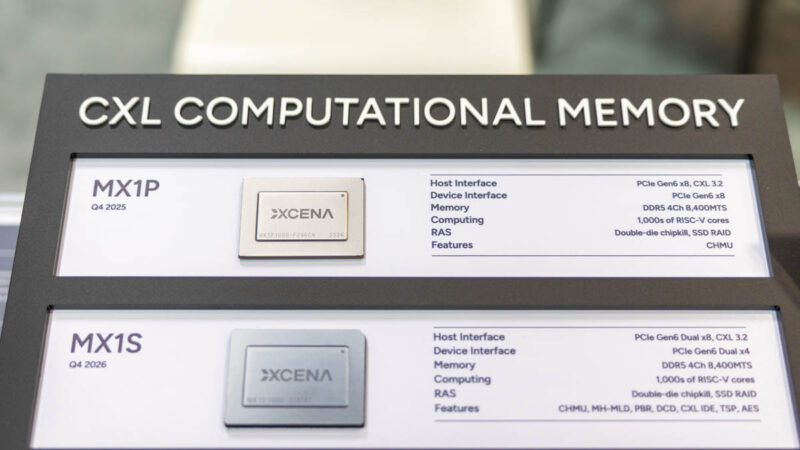

At FMS 2025, we got to see the upcoming XCENA MX1 that is apparently going into production in Q4. This is a new class of product as a PCIe Gen6-based CXL 3 memory device, but with a twist. It has “1000s” of RISC-V cores to offload compute without having to bring data back to main memory.

XCENA MX1 RISC-V Computational Memory in CXL

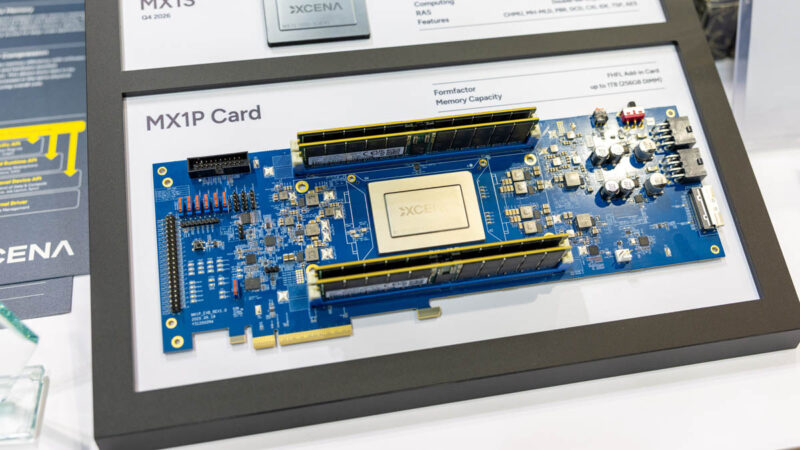

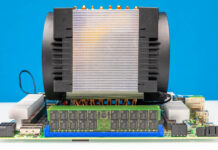

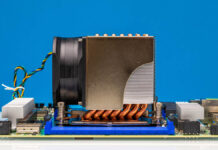

Here is the card shown at FMS 2025. One can see that this is a quad channel memory device.

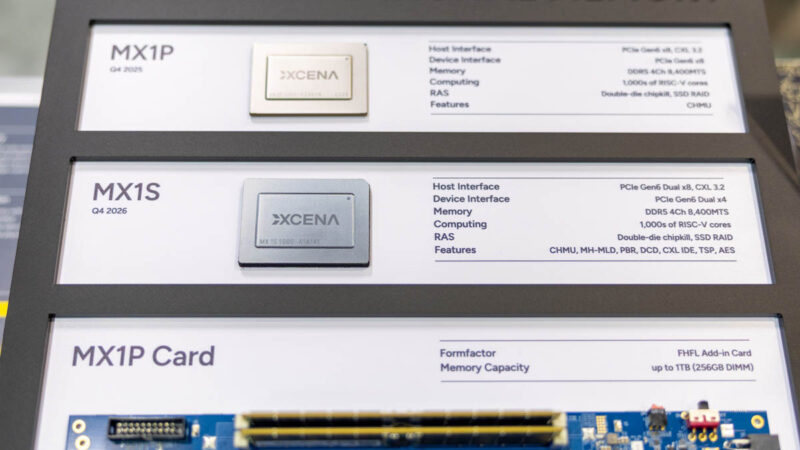

The new chips have DDR5-8400 memory controllers. The XCENA MX1P is the chip that will be coming in 2025.

The XCENA MX1S is the other CXL 3.2 chip, this time with dual PCIe Gen6 x8 links and additional features. That one is slated for 2026.

These cards support up to 256GB DIMMs for 1TB of capacity.

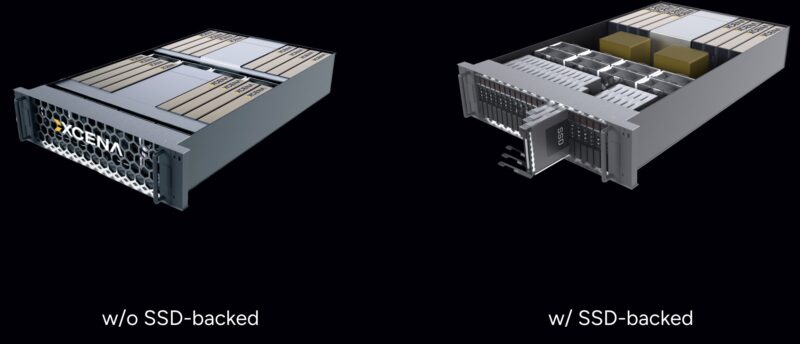

The SSD RAID feature may sound strange at first, but the application for this is very neat. XCENA has both more standard memory pools, but then also the ability to use SSD backing to expand capacity further using the SSDs as a slower tier.

Final Words

This is neat for a few reasons. First, we are pushing towards PCIe Gen6 in the near future and with that brings a lot more bandwidth for adding memory over CXL 3. Second, this is another product we are seeing to bring computational memory to CXL, in a similar concept to the 16 Arm Cores Marvell Structera A. The basic idea is that one can preserve memory bandwidth, and perhaps increase performance by offloading tasks closer to the memory versus bringing it over links back to the main processor. Also, having RISC-V cores next to the memory means that the compute it offloads next to the memory can potentially benefit not just what would happen on CPUs, but also other xPUs.

Yesterday, we looked at the XConn Tech PCIe Gen6 and CXL 3 Switch Chips, and we have already discussed the NVIDIA MGX PCIe Switch Board with ConnectX-8 with PCIe Gen6. NVIDIA needed that in place for its B300 generation PCIe Gen6 GPus even if PCIe Gen6 CPUs would not be out in 2025. Still, PCIe Gen6 and CXL 3 is coming soon.

I can’t seem to find it anywhere online but what’s the “PCIe gen 6 dual x8” or “dual x4” is it not the same as x16 or x8 respectively? It doesn’t say it’s multiple dies (like we’ll see on the MaxSun Arc Pro B60 Dual, where its actually 2 separate chips with their own x8 connection). Also the device interface on the MX1P seems to be faster than the MX1S even though it seems like the MX1S will have more features?

@Tim – I have no knowledgehere, but I speculate that it’s dual ported. ie. it’s 2x 4 lanes and it connects to both CPUs in a dual socket machine via a single hop vs a traditional setup where you have 8 lanes that are attached to a single CPU, but the second CPU would have multiple hops to reach the CXL memory.

I could be wrong, but it seems like the most obvious reason.