Serial attached memory is coming, and the Microchip SMC 1000 is one of the first chips we have seen supporting what will become the new paradigm. The Microchip SMC 1000 is an 8x25G chip that is being announced ahead of this year’s OpenPower Summit and new Power 9 chips.

Background on Serial Attached Memory

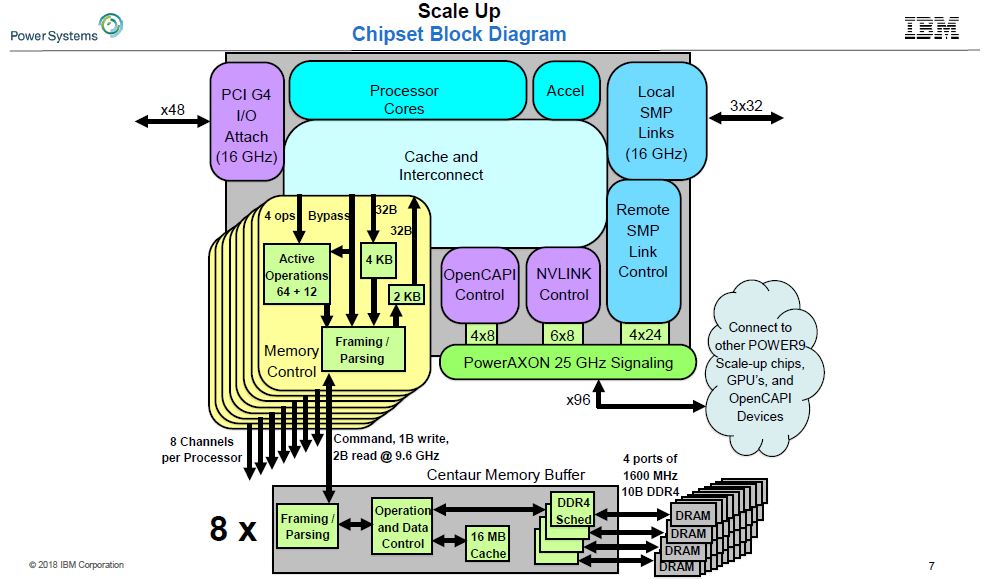

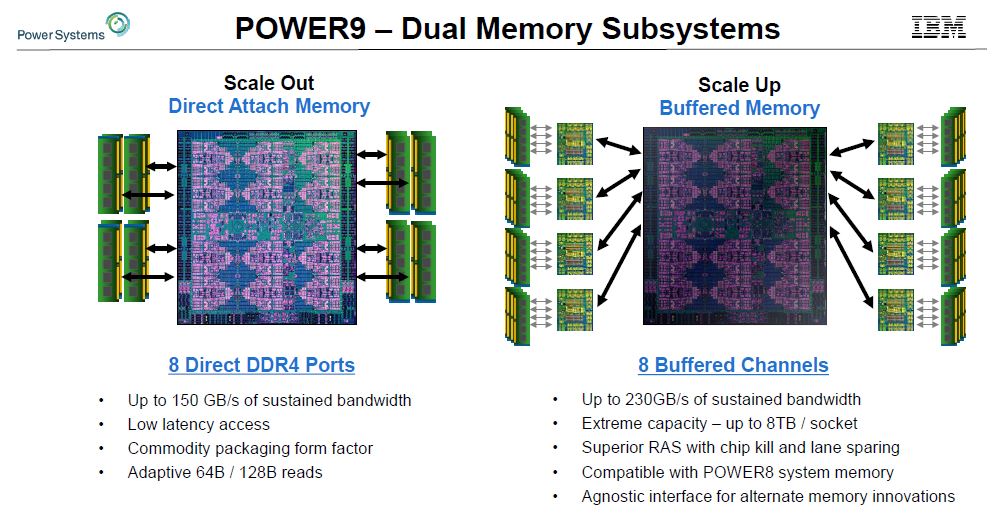

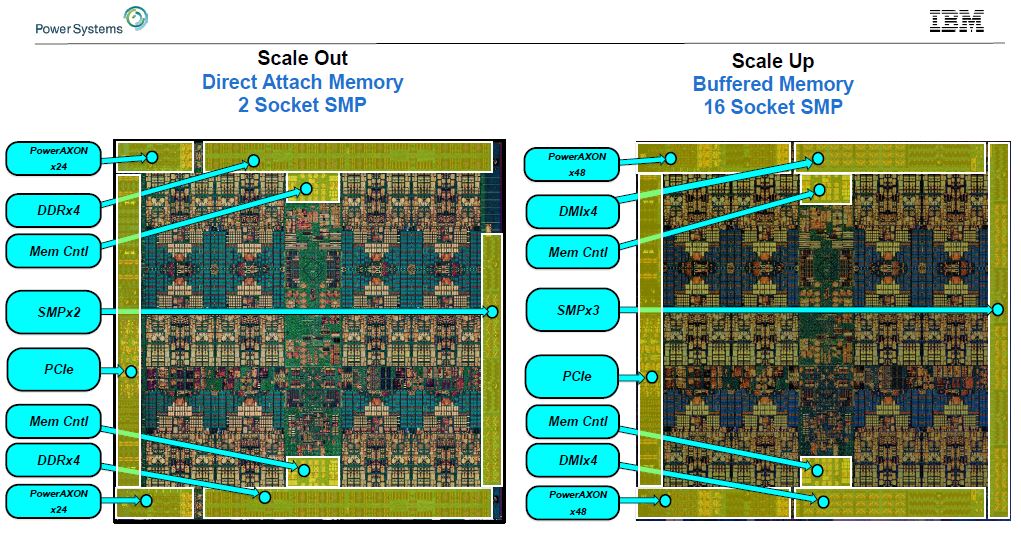

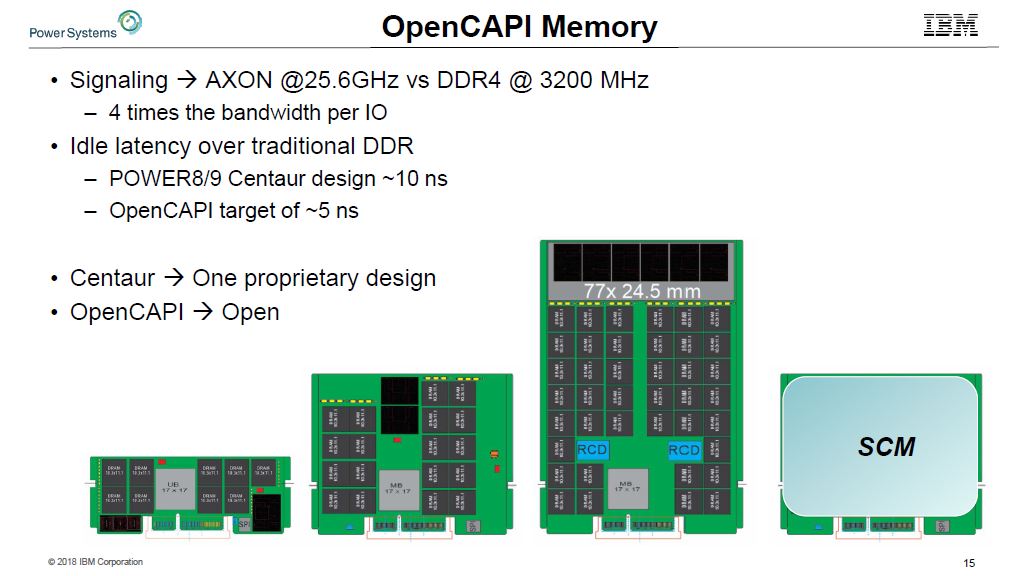

We had a primer on this during our IBM POWER9 Scale-Up CPUs with Huge IO and Effective 32 Channel DDR4 piece last year. IBM showed off its buffered memory design which we expect will be featured heavily in this year’s announcements.

The two versions of Power9 included a scale-out version with eight DDR4 ports and a scaled-up version with eight buffered memory channels.

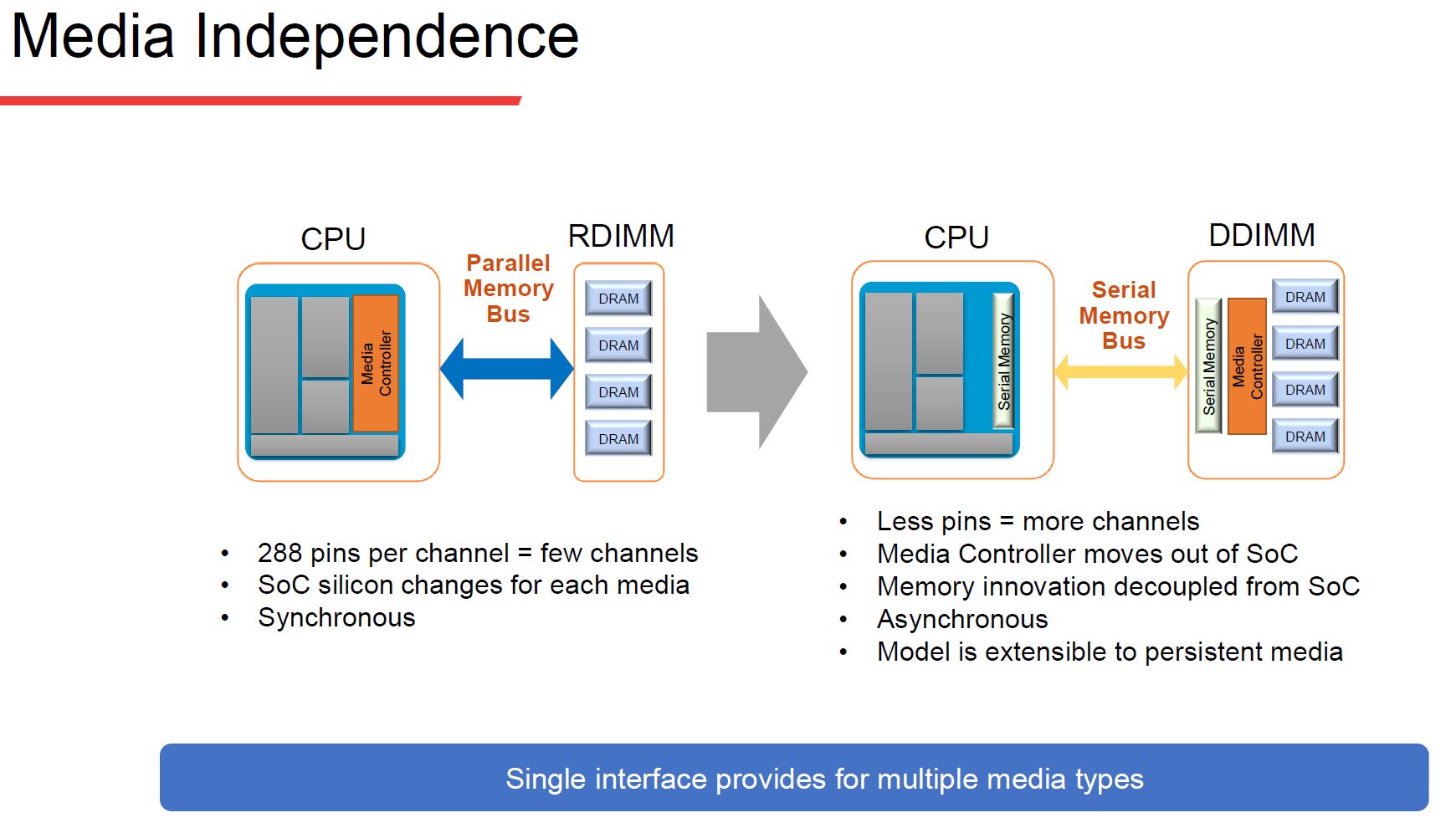

There are a few main advantages. One of the biggest is the more efficient controllers when using a serial link out of the CPU rather than DDR controllers. It requires fewer pins and less edge die space to use higher-speed serial links than DDR.

The memory that sits on the other side of the serial link is a bit different. For example, it can be designed to house DDR4, storage-class memory (SCM) or even DDR5. That is important because all the CPU sees is a point to point serial link. The logic for each memory happens on the other side of the link.

While IBM was showing off Centaur its proprietary design last year, the Microchip SMC 1000 is focused on OpenCAPI memory.

Microchip SMC 1000 Overview

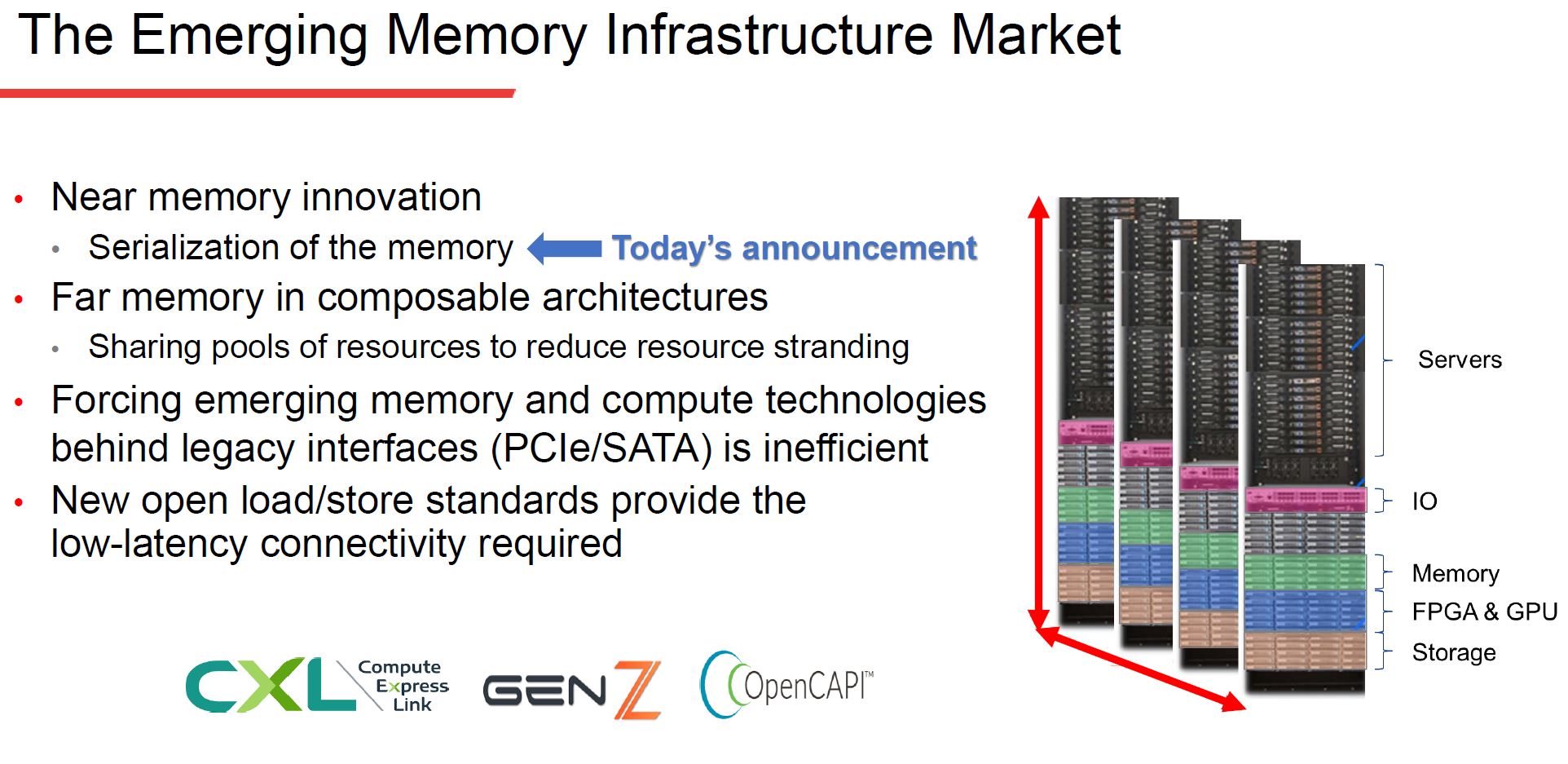

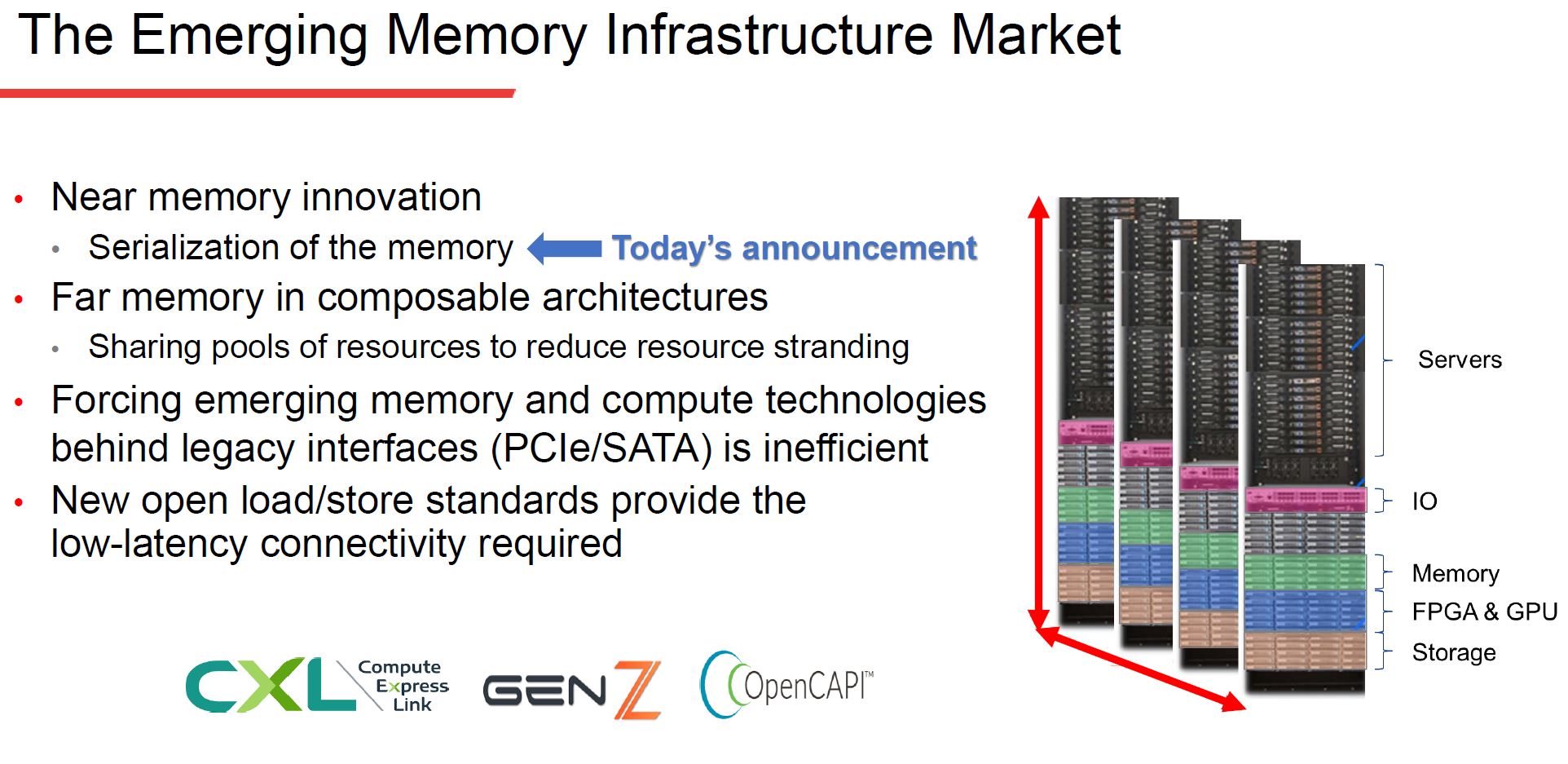

The Microchip SMC 1000 is the next progression in the market adopting serial attached memory. A future vision of the data center is racks with compute, I/O, memory, accelerators, and storage all in their own shelves. Serial attached memory is a major part of that vision as traditional DDR cannot cope with the distances.

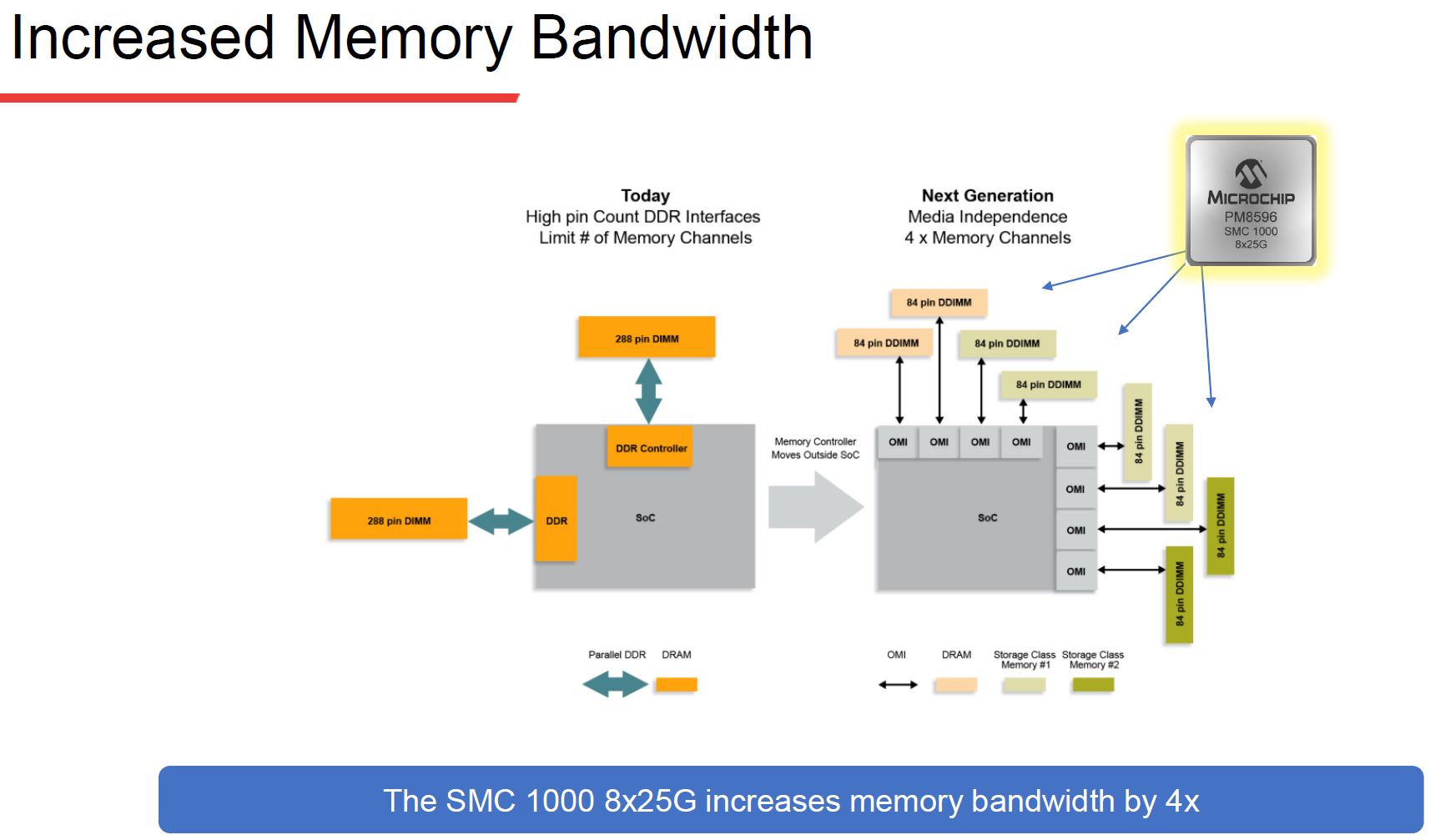

Microchip SMC 1000 is the controller that sits on the other side of a CPU serial link and interfaces with memory. The big savings here is approximately a 4:1 consolidation ratio of pins required to interface between the CPU and DDR4 chips.

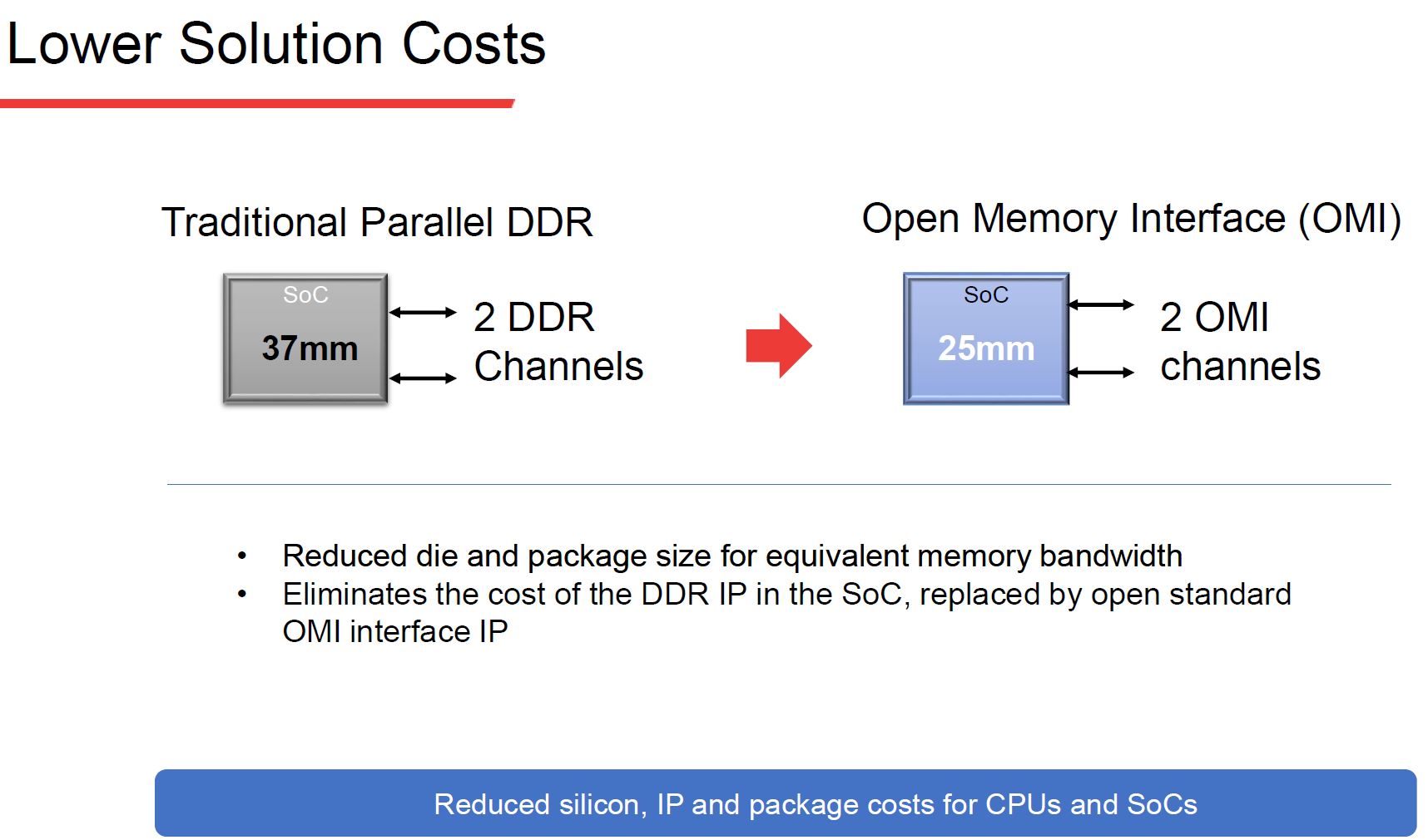

With about a quarter of the pins required, between an Open Memory Interface (OMI) and the Microchip SMC 1000 8x25G, the company says it is able to achieve 4x the memory bandwidth by using the same number of pins.

Microchip also says the solution will lower costs because the 75 or so pins on its OMI chip require less package bump space than traditional DDR4 chips.

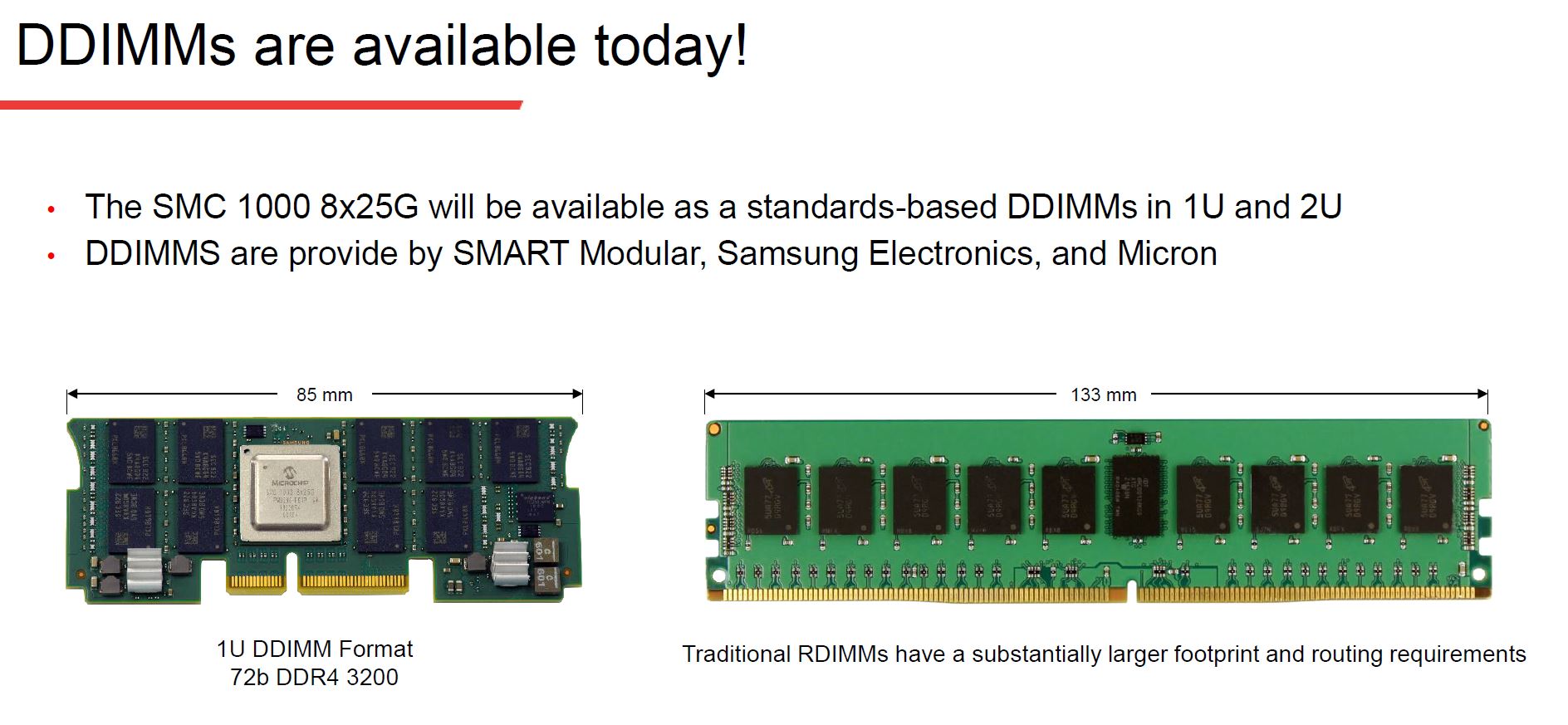

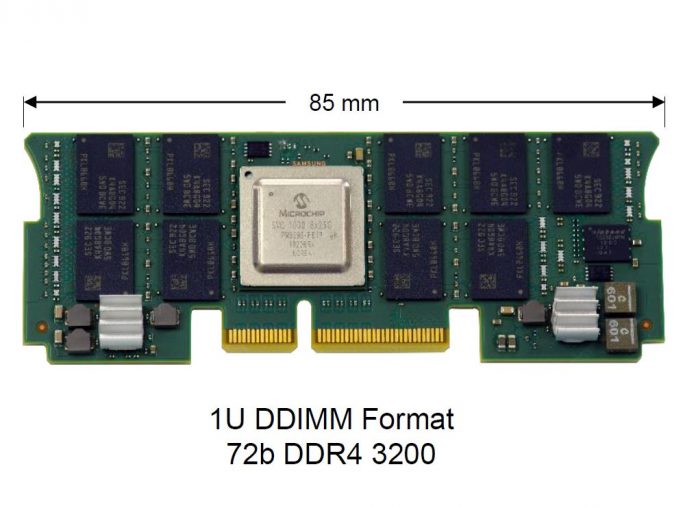

The DDIMMs for IBM Power 9 systems that support them are going to be available from SMART Modular, Samsung, and Micron starting today. One can see an example of the 1U DDIM format below compared to a standard DDR RDIMM. As you saw in the IBM slide above, with the serial memory design, one can go beyond 1U modules and pack more density per module. Also, smaller module sizes mean that motherboards can have more memory devices.

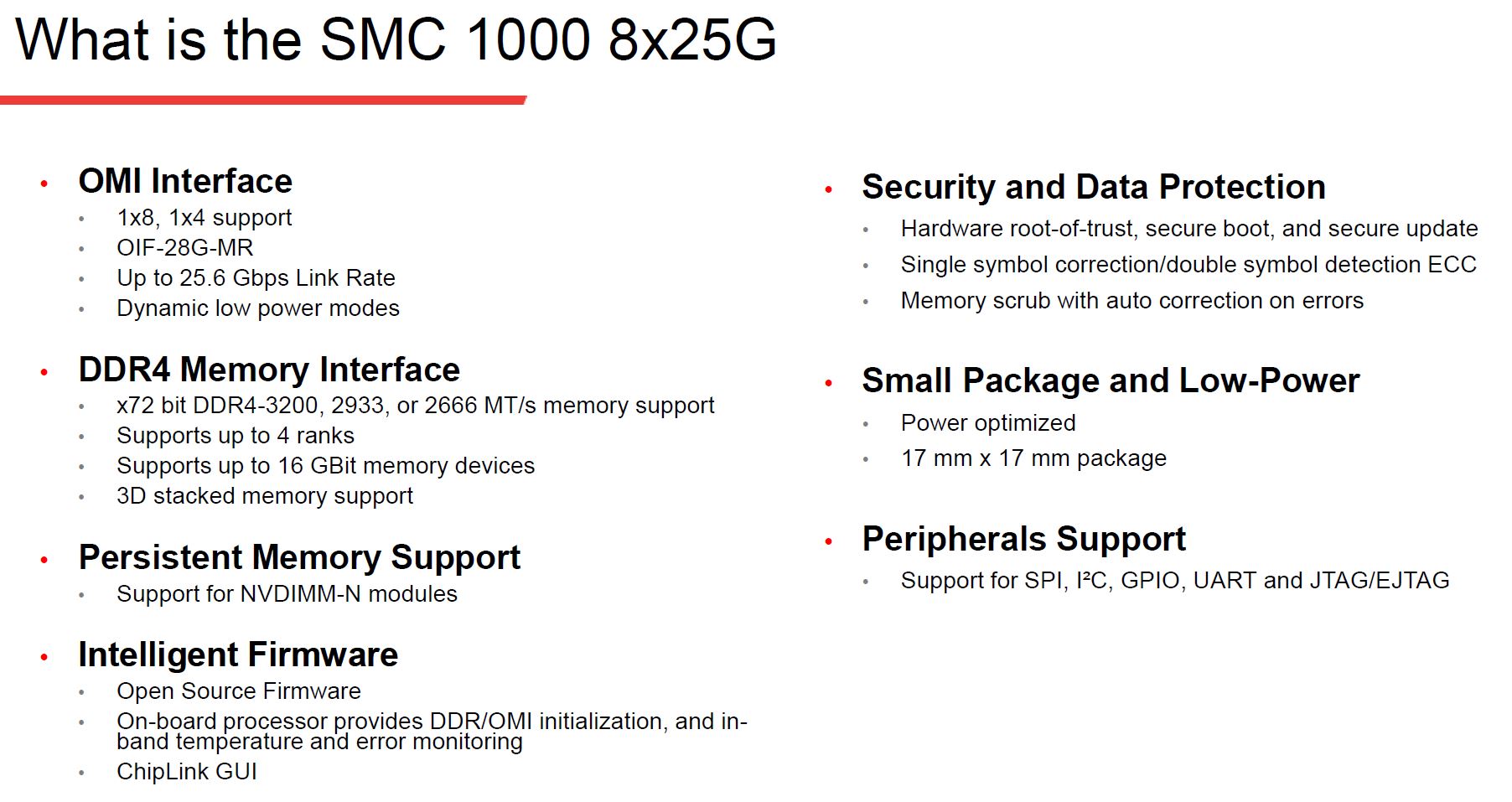

In terms of the Microchip SMC 1000 8x25G, it is as it sounds an 8x 25G link controller built for OpenCAPI / OMI. The package itself is only 17x17mm. It also can support not just traditional DDR4 memory (up to DDR4-3200 at present) but also NVDIMM-N devices.

Microchip also has all of the standard tooling I/O one would need to put these in a system and manage them.

Why this is the Future

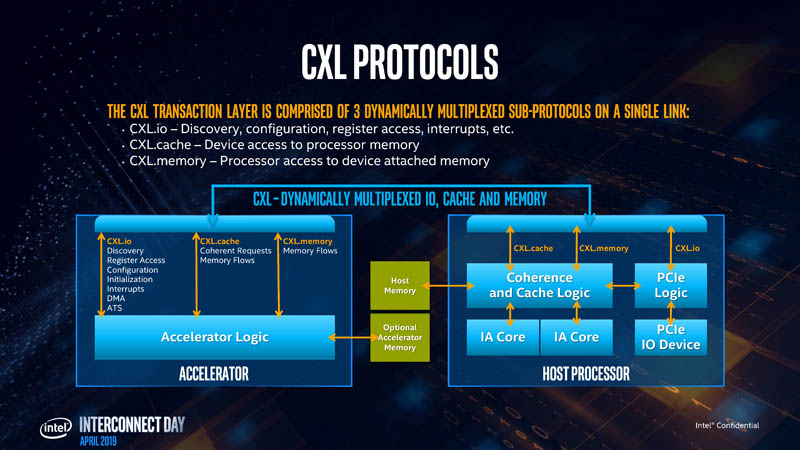

We will go to DDR5, but this is coming and not just to Power 9 and its OpenCAPI memory. If you saw the below slide earlier, CXL is clearly shown. We covered CXL Details at Intel Interconnect Day 2019. Recently, we saw AMD join CXL.

The IBM Power 9 and OpenCAPI story looks a lot like CXL, specifically the CXL.memory we saw at Interconnect Day 2019.

Moving outside the chassis, we spoke to Dell EMC and HPE about CXL and Gen-Z and those two companies currently envision CXL inside a chassis and then Gen-Z as the method to have memory sitting on a serial link on a disaggregated shelf. That may change as we get closer to real products, but it was clear in our Dell EMC PowerEdge MX Review that the system was designed for Gen-Z.

Microchip did not announce a CXL.memory product, nor a Gen-Z product. Instead, the Microchip SMC 1000 8x25G is an OpenCAPI product we will likely see mostly used with IBM Power 9 systems. At the same time, it is not hard to see where this technology and line is going. As the industry moves in this direction, Microchip is jumping on the opportunity early.

Reminds me of FB-DIMMs and those high latencies.